1、CC2530的IO口概述

CC2530芯片有21 个数字输入/输出引脚,可以配置为通用数字I/O 或外设I/O 信号,配置为连接到ADC、定时器或USART外设;这些I/O 口的用途可以通过一系列寄存器配置,由用户软件加以实现

I/O 端口具备如下重要特性:

(1)21 个数字I/O 引脚

(2)可以配置为通用I/O 或外部设备I/O

(3)输入口具备上拉或下拉能力

(4)具有外部中断能力

21 个I/O 引脚都可以用作于外部中断源输入口,因此如果需要外部设备可以产生中断,外部中断功能也可以从睡眠模式唤醒设备

2、未使用的I/O 引脚处理

未使用的I/O 引脚电平是确定的,不能悬空;一个方法是使引脚不连接,配置引脚为具有上拉电阻的通用I/O输入,这也是所有引脚复位后的状态(除了P1.0 和P1.1 没有上拉/下拉功能);或者引脚可以配置为通用I/O输出,这两种情况下引脚都不能直接连接到VDD 或GND,以避免过多的功耗

3、低I/O电压

在数字I/O 电压引脚DVDD1和DVDD2低于2.6V的应用中,寄存器位PICTL.PADSC应设置为1,以获得DC特性表中所述的输出DC 特性

4、通用I/O

用作通用I/O 时,引脚可以组成3个8位端口,端口0、端口1 和端口2,表示为P0、P1 和P2;其中,P0和P1 是完全的8 位端口,而P2 仅有5 位可用;所有的端口均可以通过SFR寄存器P0、P1 和P2 位寻址和字节寻址,每个端口引脚都可以单独设置为通用I/O或外部设备I/O

(驱动电流很重要,有时候和MOS管电路、上拉电阻的选择等密切相关)除了两个高驱动输出口P1.0 和P1.1 各具备20mA 的输出驱动能力之外,所有的输出均具备4 mA 的驱动能力

寄存器PxSEL(选择为通用IO模式还是外设IO信号),其中x 为端口的标号0~2,用来设置端口的每个引脚为通用I/O 或者是外部设备I/O 信号;作为缺省的情况,每当复位之后,所有的数字输入/输出引脚都设置为通用输入引脚

在任何时候,要改变一个端口引脚的方向,就使用寄存器PxDIR(选择输入或输出)来设置每个端口引脚为输入或输出;因此只要设置PxDIR 中的指定位为1,其对应的引脚口就被设置为输出了

当读取端口寄存器P0、P1 和P2 的值,不管引脚配置如何,输入引脚上的逻辑值都被返回,这在执行读-修改-写指令期间不适用;读-修改-写指令是:ANL,ORL,XRL,JBC,CPL,INC,DEC,DJNZ,MOV,CLR和SETB,在一个端口寄存器上操作,以下是正确的:当目标是端口寄存器P0、P1 或P2 中一个独立的位,寄存器的值,而不是引脚上的值,被读取、修改并写回端口寄存器

用作输入时,通用I/O 端口引脚可以设置为上拉、下拉或三态操作模式,作为缺省的情况,复位之后,所有的端口均设置为带上拉的输入,要取消输入的上拉或下拉功能,就要将PxINP(输入上拉、下拉、三态模式选择)中的对应位设置为1;I/O 端口引脚P1.0 和P1.1 没有上拉/下拉功能,注意配置为外设I/O 信号的引脚没有上拉/下拉功能,即使外设功能是一个输入

在电源模式PM1、PM2 和PM3 下I/O 引脚保留当进入PM1/PM2/PM3 时设置的I/O 模式和输出值(如果可用的话)

5、通用I/O 中断

通用I/O 引脚设置为输入后,可以用于产生中断,中断可以设置在外部信号的上升或下降沿触发;P0、P1 或P2 端口都有中断使能位,对位于IENl(端口中断使能寄存器)寄存器内的端口所有的位都是公共的,如下:

IEN1.P0IE:P0 中断使能

IEN2.P1IE:P1 中断使能

IEN2.P2IE:P2 中断使能

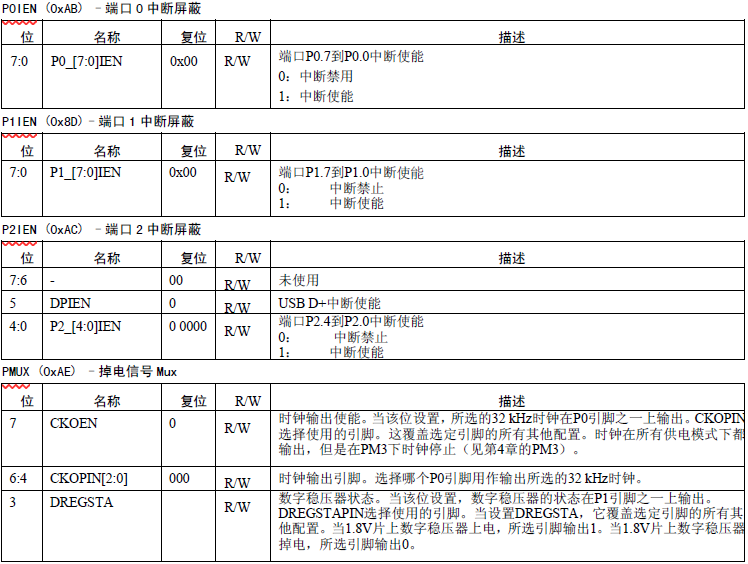

除了这些公共中断使能之外,每个端口的位都有位于SFR 寄存器P0IEN、P1IEN 和P2IEN(单独引脚中断使能寄存器)的单独的中断使能,即使配置为外设I/O 或通用输出的I/O 引脚使能时都有中断产生

当中断条件发生在I/O 引脚之一上面,P0-P2 中断标志寄存器P0IFG、P1IFG 或P2IFG(中断标志寄存器)中相应的中断状态标志将设置为1,不管引脚是否设置了它的中断使能位,中断状态标志都被设置;当中断已经执行,中断状态标志被清除,该标志写入0,这个标志必须在清除CPU 端口中断标志(PxIF)之前被清除;寄存器总结如下:

P0IEN:P0 中断使能

P1IEN:P1 中断使能

P2IEN:P2 中断使能

PICTL:P0、P1 和P2 触发沿设置

P0IFG:P0 中断标志

P1IFG:P1 中断标志

P2IFG:P2 中断标志

6、通用I/O DMA

当用作通用I/O 引脚时,每个P0 和P1 端口都关联一个DMA 触发,这些DMA 触发对于P0 为IOC_0,对于P1 为IOC_1;当一个中断发生在P0 引脚时IOC_0 触发是被激活的,当一个中断发生在P1 引脚时IOC_1 触发是被激活的

7、外设I/O

对于USART 和定时器I/O,在一个数字I/O 引脚上选择外设I/O 功能,需要设置对应的PxSEL 位为1

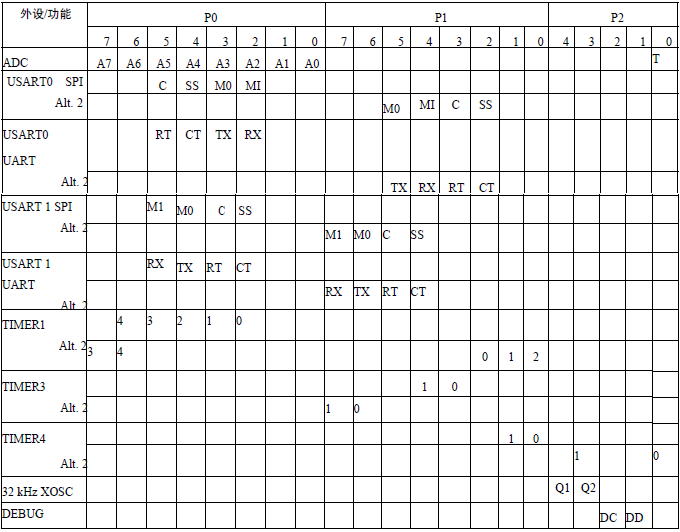

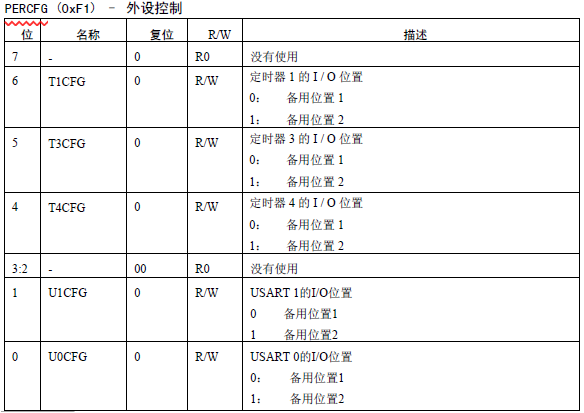

注意:该外部单元具有两个可以选择的位置对应它们的I/O 引脚,参见下表;如果有关于I/O 映射的冲突设置,可以在这些之间设置优先级(使用P2SEL.PRIxP1 和P2DIR.PRIP0 位),所有不会导致冲突的组合都可以使用

注意即使没有使用,外设一般也会出现在选定的位置,使用引脚的其他外设必须给予较高的优先级,例外情况是流量控制禁用时UART 模式下USART 的RTS 和CTS 引脚, 以及SPI 主模式下USART 配置的SSN 引脚

还要注意不管PxINP 的设置,有输入引脚的外设单元是从引脚接收输入,这可能会影响外设单元的状态,例如如果RX 引脚在用作一个UART 引脚之前,可能已经有活动, UART 在使用之前必须被清除

7.1、定时器1

PERCFG.T1CFG 选择是否使用备用位置1 或备用位置2

在上表中,定时器1 的信号显示如下:

0:通道0 捕获/比较引脚

1:通道1 捕获/比较引脚

2:通道2 捕获/比较引脚

3:通道3 捕获/比较引脚

4:通道4 捕获/比较引脚

P2DIR.PRIP0(指派端口0一些外设的优先顺序)选择为端口0 指派一些外设的优先顺序,当设置为10,定时器通道0-1 优先,当设置为11,定时器通道2-3 优先,要所有定时器1 通道在备用位置1 上可见,移动USART 0 和USART 1 到备用位置2;P2SEL.PRI1P1 和P2SEL.PRI0P1(外设优先级设置)选择为端口1 指派一些外设的优先顺序,当前者设置为低电平而后者设置为高电平时,定时器1 通道优先

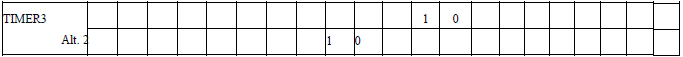

7.2、定时器3

PERCFG.T3CFG 选择是否使用备用位置1 或备用位置2

在表中,定时器3 的信号显示如下:

0:通道0 比较引脚

1:通道1 比较引脚

P2SEL.PRI2P1 和P2SEL.PRI3P1 选择为端口1 指派一些外设的优先顺序,当这两个位都设置为高电平时,定时器3 通道优先,如果P2SEL.PRI2P1 设置为高电平且P2SEL.PRI3P1 设置为低电平时,定时器3 通道优先于USART 1,但是USART 0 优先于定时器3 通道以及USART 1

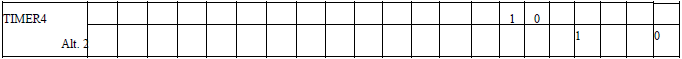

7.3、定时器4

PERCFG.T4CFG 选择是否使用备用位置1 或备用位置2

在表中,定时器4 的信号显示如下:

0:通道0 比较引脚

1:通道1 比较引脚

P2SEL.PRI1P1 选择为端口1 指派一些外设的优先顺序,当这个位设置时,定时器4 通道优先

7.4、USART 0

SFR 寄存器位PERCFG.U0CFG 选择是否使用备用位置1 或备用位置2

在表中,USART 0 信号显示如下:

UART:

● RX:RXDATA

● TX:TXDATA

● RT:RTS

● CT:CTS

SPI:

● MI:MISO

● MO:MOSI

● C:SCK

● SS:SSN

P2DIR.PRIP0 选择为端口0 指派一些外设的优先顺序,当设置为00 时,USART 0 优先,注意如果选择了UART 模式,且硬件流量控制禁用,UART 1 或定时器1 将优先使用端口P0.4 和P0.5;P2SEL.PRI3P1 和P2SEL.PRI0P1 选择为端口1 指派一些外设的优先顺序,当它们两个都设置为0 时,USART0 优先,注意如果选择了UART 模式,且硬件流量控制禁用,定时器1 或定时器3 将优先使用端口P1.2 和P1.3

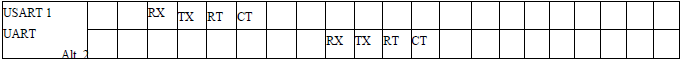

7.5、USART 1

SFR 寄存器位PERCFG.U1CFG 选择是否使用备用位置1 或备用位置2

在表中,USART 1 信号显示如下:

UART:

● RX:RXDATA

● TX:TXDATA

● RT:RTS

● CT:CTS

SPI:

● MI:MISO

● MO:MOSI

● C:SCK

● SS: SSN

P2DIR.PRIP0 选择为端口0 指派一些外设时的优先顺序,当设置为01,USART 1 优先,注意如果选择了UART 模式,且硬件流量控制禁用,USART 0 或定时器1 将优先使用P0.2 和P0.3;P2SEL.PRI3P1 和P2SEL.PRI2P1 选择为端口1 指派一些外设的优先顺序,当前者设置为1 而后者设置为0时,USART 1 优先,注意如果选择了UART 模式,且硬件流量控制禁用,USART 0 或定时器3 将优先使用P1.4和P1.5

7.6、ADC

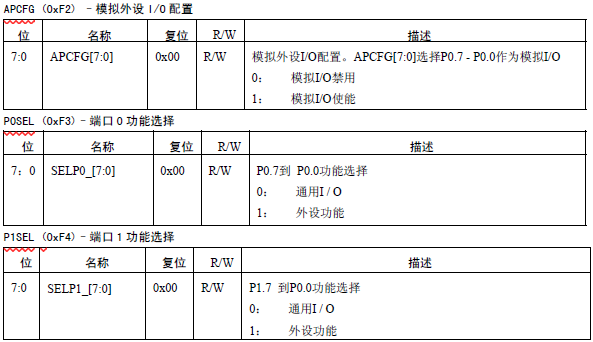

当使用ADC 时,端口0 引脚必须配置为ADC 输入,可以使用多达八个ADC 输入引脚,要配置一个端口0引脚为一个ADC 输入,APCFG 寄存器中相应的位必须设置为1,这个寄存器的默认值选择端口0 引脚为非ADC输入,即数字输入/输出;APCFG 寄存器的设置将覆盖P0SEL的设置,

ADC 可以配置为使用通用I/O 引脚P2.0 作为内部触发器来启动转换,当用作ADC 内部触发器时,P2.0 必须在输入模式下配置为通用I/O

7.7、调试接口

端口P2.1 和P2.2 分别用于调试数据和时钟信号,这些显示为表中的DD(调试数据)和DC(调试时钟);当处于调试模式,调试接口控制这些引脚的方向,当处于调试模式在这些引脚上禁用上拉/下拉

7.8、32 kHz XOSC 输入

端口P2.3 和P2.4 用于连接一个外部32 kHz 晶振,当CLKCONCMD.OSC32K 是低电平时,不管寄存器设置如何,这些端口引脚由32 kHz XOSC 使用,当CLKCONCMD.OSC32K 是低电平,这些端口引脚将设置在模拟模式

7.9 无线测试输出信号

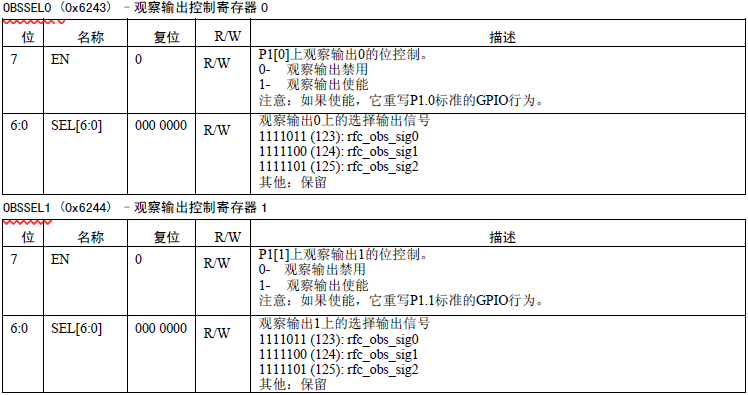

通过使用OBSSELx 寄存器(OBSSEL0-OBSSEL5),用户可以从RF 内核输出不同的信号到GPIO 引脚,这些信号可以用于调试低级别的协议或控制外部PA、LNA 或交换机;控制寄存器OBSSEL0-OBSSEL5 可以用于覆盖标准的GPIO 行为,以及在引脚P1[0:5]上输出RF 内核信号(rfc_obs_sig0、rfc_obs_sig1 和rfc_obs_sig2)

7.10、掉电信号MUX (PMUX)

PMUX 寄存器可以用于输出32 kHz 时钟和/或数字稳压器的状态,所选的32 kHz 时钟源可以输出在P0 其中的一个引脚上,使能位CKOEN 使得输出在P0 上,使用CKOPIN(详细信息见PMUX 寄存器描述)选择P0 的引脚,当CKOEN 被设置,所选引脚的所有其他配置都被覆盖,时钟在所有供电模式下都输出;但是,在PM3 下时钟停止,而且,数字稳压器的状态可以输出在P1 其中的一个引脚上,当DREGSTA 位被设置,数字稳压器的状态就被输出,DREGSTAPIN 选择P1 引脚(详细信息见PMUX 寄存器描述),当DREGSTA 被设置,所选引脚的所有其他配置都被覆盖,当1.8V 片上数字稳压器上电(芯片有调整过的电压),所选的引脚输出1,当1.8V片上数字稳压器掉电,即在PM2 和PM3 下,所选的引脚输出0

7.11 I/O 引脚

● P0 :端口0

● P1 :端口1

● P2 :端口2

● PERCFG :外设控制寄存器

● APCFG :模拟外设I/O 配置

● P0SEL :端口0 功能选择寄存器

● P1SEL :端口1 功能选择寄存器

● P2SEL :端口2 功能选择寄存器

● P0DIR :端口0 方向寄存器

● P1DIR :端口1 方向寄存器

● P2DIR :端口2 方向寄存器

● P0INP :端口0 输入模式寄存器

● P1INP :端口1 输入模式寄存器

● P2INP :端口2 输入模式寄存器

● P0IFG :端口0 中断状态标志寄存器

● P1IFG :端口1 中断状态标志寄存器

● P2IFG :端口2 中断状态标志寄存器

● PICTL :中断边缘寄存器

● P0IEN :端口0 中断掩码寄存器

● P1IEN :端口1 中断掩码寄存器

● P2IEN :端口2 中断掩码寄存器

● PMUX :掉电信号Mux 寄存器

● OBSSEL0 :观察输出控制寄存器0

● OBSSEL1 :观察输出控制寄存器1

● OBSSEL2 :观察输出控制寄存器2

● OBSSEL3 :观察输出控制寄存器3

● OBSSEL4 :观察输出控制寄存器4

● OBSSEL5 :观察输出控制寄存器5