当DRC和STA没有问题时,后仿真出了violation应该如何解决

后仿真出了问题如何解决

在ICC布局布线之后是PT,STA分析,当这些都显示ok时,我们还剩下最后一步工作--- 就是后仿真。

一般来讲,是基本不会有问题的,所以当出现问题的时候,我就懵了。师傅离职之前没有遇到过这情况,我该咋办呢?

好吧,经过我的摸索后,我如今已经知道了,写下来作为笔记和知识分享。

当出现violation集中报错在一个或几个寄存器时,不要惊慌

以一个corner下面的tb结果为例,

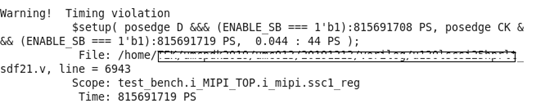

报出来的问题一般以如下图的形式给出:

根据类似上图的violation,我们能得到那些信息能呢?

- 首先看到有setup违规

- 出现违规的时间是815xxxxxPS和81569xxxxPS

- 寄存器D端到CK端发生SETUP时间不满足问题

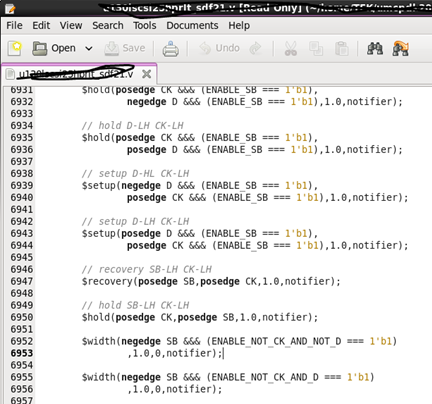

- 打开verilog.v的文件对应观察6943行(内容如下图,但是没有信息量,只能说是source到这个文件里)

5.非常重要的一点:出现问题的寄存器模块和名称i_mipi/ssc1_reg

l 对于所有信息已经分析完毕,下一步我们打开Debussy&。查看波形。

关于波形怎么debug问题。下面这些都是自己摸索的。希望有大佬或者好心人指点更好的功法吧。

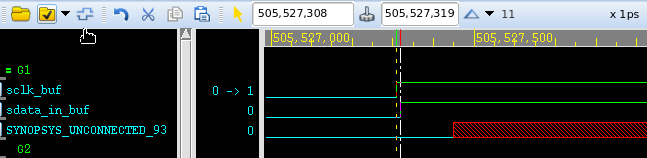

- 打开icc_layout的post_layout.v文件,并找到ssc1_reg(即出错的寄存器名)。可以看到使用的器件是DFSM2。把对应的相关信号加入nWave中查看,即SYNOPSYS_**93,sdata_buf,sclk_buf。

2.观察时钟CK端和D输入端的时间差。仅有11ps

3.方法一:

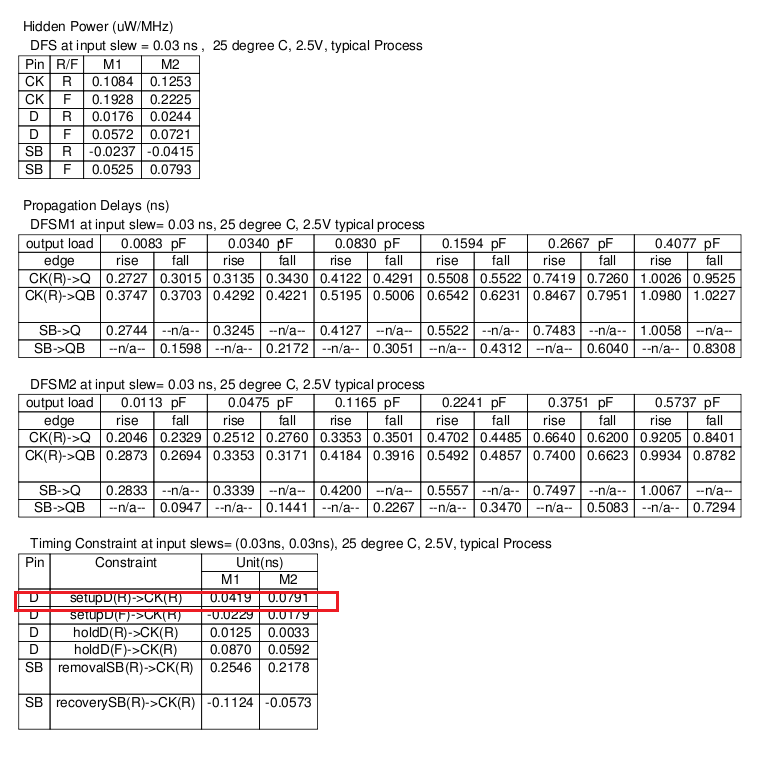

a) 在Foundry提供的Databook器件手册里找到关于DFM2的stdcell说明,红色是我想要的部分,显示了D到CK需要0.0791ns的时间。(至于是Rise 还是Fall需要自行到模块中去查找)。所以判断需要加入buf去增加setup时间

未完待续

浙公网安备 33010602011771号

浙公网安备 33010602011771号