LiteOS学习笔记[01]-weharmonyos-基础知识

双向链表

-

为什么

LOS_ListHeadInsert的实现是从头部节点的后面也就是第二个节点的位置插入新节点,而不是直接将头部节点更新为插入的节点?头部节点的作用:在双向链表中,头部节点(通常称为头结点或哑结点)通常不存储实际的数据,而是作为链表的起始点和操作的辅助节点。它使得链表的操作(如插入、删除、遍历等)更加统一和方便。

-

为什么LiteOS后面还有一个-A?

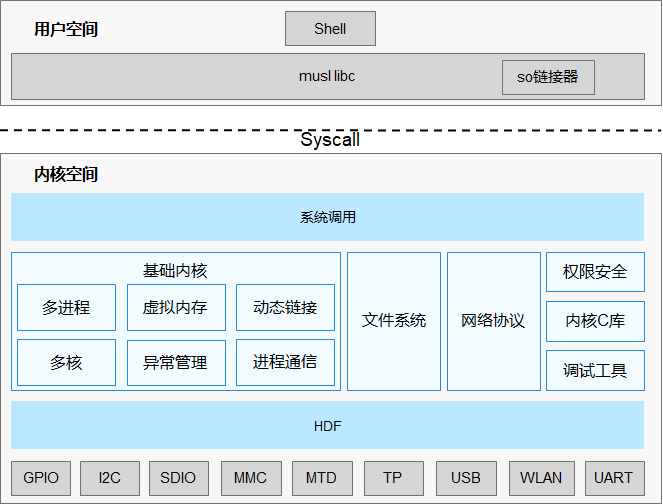

OpenHarmony LiteOS-A内核是基于Huawei LiteOS内核演进发展的新一代内核,Huawei LiteOS是面向IoT领域构建的轻量级物联网操作系统。在IoT产业高速发展的潮流中,OpenHarmony LiteOS-A内核能够带给用户小体积、低功耗、高性能的体验以及统一开放的生态系统能力,新增了丰富的内核机制、更加全面的POSIX标准接口以及统一驱动框架HDF(OpenHarmony Driver Foundation)等,为设备厂商提供了更统一的接入方式,为OpenHarmony的应用开发者提供了更友好的开发体验。

源码结构

-

读源码最需要的东西:架构图和源码结构

/kernel/liteos_a ├── apps # 用户态的init和shell应用程序 ├── arch # 体系架构的目录,如arm等 │ └── arm # arm架构代码 ├── bsd # freebsd相关的驱动和适配层模块代码引入,例如USB等 ├── compat # 内核接口兼容性目录 │ └── posix # posix相关接口 ├── drivers # 内核驱动 │ └── char # 字符设备 │ ├── mem # 访问物理IO设备驱动 │ ├── quickstart # 系统快速启动接口目录 │ ├── random # 随机数设备驱动 │ └── video # framebuffer驱动框架 ├── fs # 文件系统模块,主要来源于NuttX开源项目 │ ├── fat # fat文件系统 │ ├── jffs2 # jffs2文件系统 │ ├── include # 对外暴露头文件存放目录 │ ├── nfs # nfs文件系统 │ ├── proc # proc文件系统 │ ├── ramfs # ramfs文件系统 │ └── vfs # vfs层 ├── kernel # 进程、内存、IPC等模块 │ ├── base # 基础内核,包括调度、内存等模块 │ ├── common # 内核通用组件 │ ├── extended # 扩展内核,包括动态加载、vdso、liteipc等模块 │ ├── include # 对外暴露头文件存放目录 │ └── user # 加载init进程 ├── lib # 内核的lib库 ├── net # 网络模块,主要来源于lwip开源项目 ├── platform # 支持不同的芯片平台代码,如Hi3516DV300等 │ ├── hw # 时钟与中断相关逻辑代码 │ ├── include # 对外暴露头文件存放目录 │ └── uart # 串口相关逻辑代码 ├── security # 安全特性相关的代码,包括进程权限管理和虚拟id映射管理 ├── syscall # 系统调用 ├── testsuites # 单元测试用例 ├── tools # 构建工具及相关配置和代码 └── zzz # 中文注解版新增目录

计时单位

-

各种不同的周期概念:

- 时钟周期 这里的时钟指的就是晶振,也叫晶振周期/振荡周期。它是计算机的最小时间单元,其他周期只能是它的倍数。

- 机器周期 一个机器周期等于多个时钟周期。它是

CPU完成一个基本操作的时间单元。比如: 取指、译码、存储器读/写、运算等等操作。 - 指令周期 它是

CPU完成一条指令的时间。不同的机器分解指令周期的方式也不同,有的处理器对每条指令分解出相同数量的机器周期,另一些处理器根据指令的复杂程度分解出不同数量的机器周期。 - 总线周期 它是

CPU操作总线设备的时间,由于存贮器和I/O端口是挂接在总线上的,对它们的访问,是通过总线实现的。通常将进行一次访问所需时间称为一个总线周期。这种访问速度较慢,因硬件发展的原因,各个设备的工作频率无法同步,甚至相差几个数量级,就出现了分频概念,将高频信号变成低频信号。 - 从时间长短角度总结下 时钟周期 < 机器周期 < 指令周期 < 总线周期

优雅的宏

-

volatile关键字的作用究竟是什么?以前只知道是防止CPU从寄存器或缓存中读取临时值,而是直接从内存中读取新的值,这次一步到位彻底理解它:- 防止编译器优化

- 编译器在进行代码优化时,可能会将变量的值保存在寄存器中,以减少对内存的访问次数,从而提高程序的执行效率。然而,对于一些特殊的变量,如外部设备寄存器、中断服务程序中的共享变量等,每次访问都需要实时读写内存,不能依赖寄存器中的缓存值。使用volatile关键字可以告诉编译器不要对该变量进行优化,确保每次对该变量的读写都直接操作内存。

- 保证变量的可见性

- 在多线程编程中,当一个线程修改了被声明为volatile的变量后,其他线程能够立即看到这个变量的最新值,而不是看到可能被缓存的旧值。这是因为volatile变量会直接从主内存读取,而不是从线程的本地缓存中读取。这一特性有助于避免线程之间的数据竞争,并确保多线程环境下变量的值是最新的。

- 保证指令的有序性

- 使用volatile关键字可以防止编译器对代码进行指令重排序。在多线程环境中,指令重排序可能会导致数据不一致或难以预测的行为。volatile关键字可以确保对volatile变量的写入在所有前面的操作完成后才能被执行,从而保持指令的顺序性。

- 防止编译器优化

-

缓冲区(cache)

写缓冲是为了提高存储器的总体访问效率而设的,但它会带出来一个副作用就是同步问题,会导致写内存的指令被延迟几个周期执行,因此对存储器的设置不能即刻生效,这会导致紧临着的下一条指令仍然使用旧的存储器设置——但程序员的本意显然是使用新的存储器设置。这种紊乱危象是后患无穷的,常会破坏未知地址的数据,有时也会产生非法地址访问。

调试的时候经常遇到这种问题......现在遇到那种现象比较诡异的问题,一般都先加两条刷新Cache的代码看看有没有效果。

-

流水线

常常看到流水线的概念,也大致了解其是什么,但由于还没学用FPGA实现RISC-V内核,到现在还是不太理解流水线是怎么实现的,CPU什么时候决定使用流水线,还是说由编译器决定?在此记录以后追究。

位图管理

-

什么是位图,之前在文件系统源码中看到过,现在又在优先级模块中看到?

如其名,位图是一种比特数组或矩阵。位图管理器就是对其中位的各种操作。参考https://www.cnblogs.com/gongsir0630/p/13478205.html

POSIX

-

CMSIS,好久不用ARM架构的芯片 ,对这个东西都有些生疏。

ARM的硬件抽象层

CMSIS( Cortex Microcontroller Software Interface Standard)缩写,中文为Cortex系列微控制器软件接口标准。此标准是ARM公司,芯片供应商以及软件供应商共同制定的。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具