pre/post gate sim 仿真笔记

在芯片研发阶段至少存在三种仿真,只有在这三种仿真都通过后才可能进入到芯片的tape out阶段,这三种仿真分别是rtl 功能级仿真、综合后网表仿真(pre gate sim)、PR后网表仿真(post gate sim)。下面简单记录一下两种gate sim仿真。

不论是pre还是post的gate sim都是门级网表的仿真,进行门级仿真主要有两个目的:1 检查门级网表的功能是否符合设计意图;2 将门级网表的仿真波形用于功耗分析。

这里建议进行门级仿真的case由代码设计者或者算法设计人员提供场景,原因是他们十分清楚什么样的场景能充分得到可与目标功耗具有比较意义的功耗数据;同时也建议做门级仿真的人员最好是验证人员,因为门级仿真的环境是在功能仿真的环境上进行修改得到的,验证的人员更熟悉验证环境,同时需要门级功耗数据时已经进行到研发时间紧迫的阶段,这样能减少门级仿真所花费的时间,提升功耗决策效率,而且验证人员也更熟悉每支case如何确认波形的正确性,避免功耗的输入波形有误,造成决策失误,从而影响项目进程。

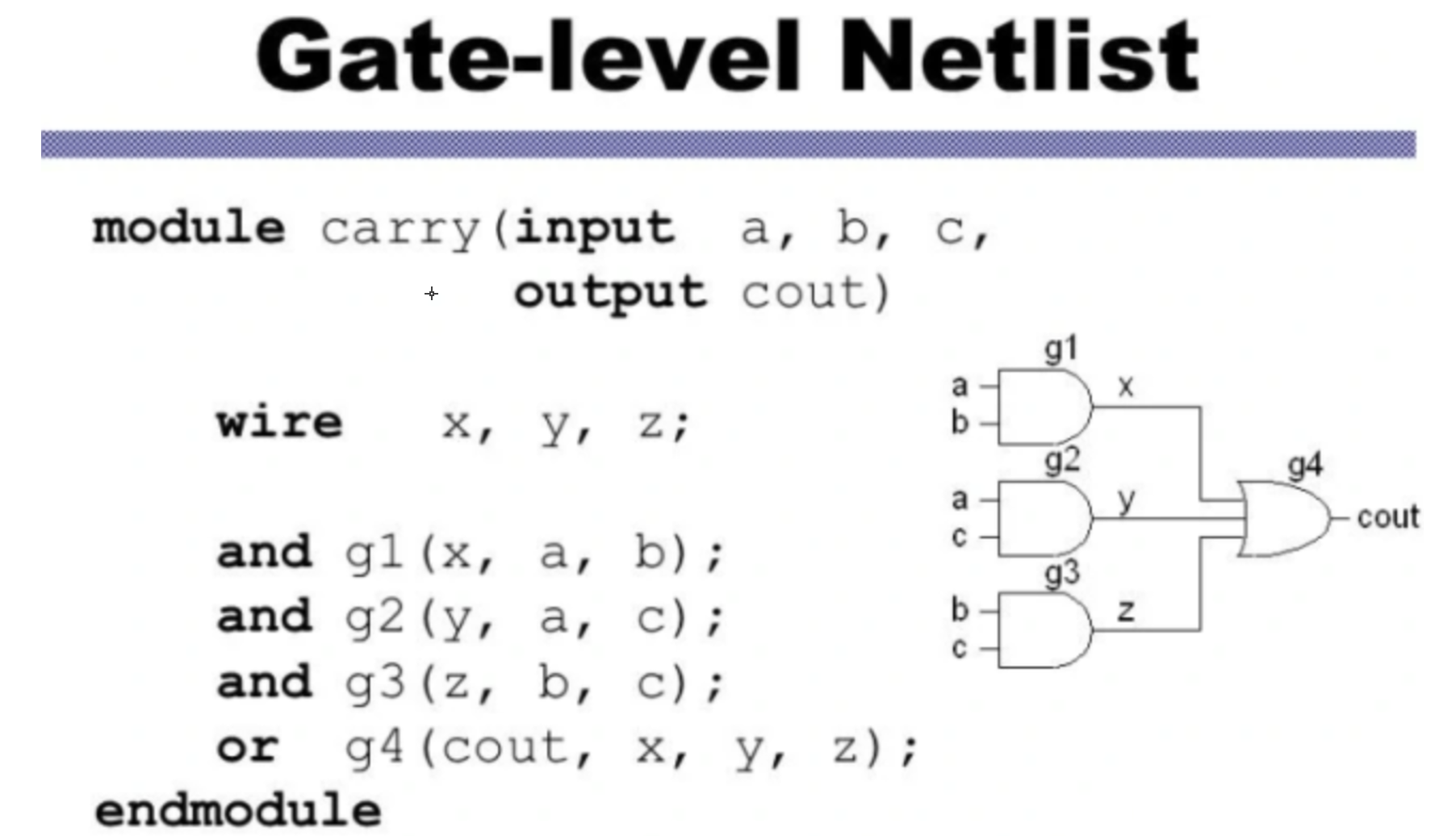

门级网表概念

数字前端设计的RTL代码 中的寄存器和组合逻辑,其物理实现还是对应到具体门电路。由于基本的寄存器或组合逻辑,对应的电路结构已经很稳定,电学特性也很明确,故而在综合级别较高的 EDA 工具中,一般不需要再亲自去描述它们的实现方法,而是调用现成的库信息。EDA 工具会根据 RTL 描述自动编译出门级的电路描述,这就是门级网表。门级网表分为pr前网表和pr后网表。

-

PR前网表: 又称为综合(一般为Design Compiler)后网表,采用的是工艺库中default的timing,且只有cell的timing信息。此时由于内部的setup和hold没有修好,会出现不少violation的情形。

-

PR后网表: 相比于pr前网表,pr后网表加上了buf,decap,filler和antenna等器件,timing信息也与pr前网表一致。

三、什么是sdf文件?

SDF文件(standard delay format),直译过来就是标准延时格式。它描述设计中的timing信息,指明了模块管脚与管脚之间的delay,时钟到数据的delay,内部连接delay等。后端布局布线之后由“QRC”出spef,通过PT生成sdf,所以sdf中timing信息都是布局布线之后客观存在的timing。总而言之,SDF文件是把布局布线过程中的器件延时和线延时信息记录下来,从而在进行路径时序分析时可以将整条路径的时序计算出来,再根据时序约束条件判断是否满足时序要求。

设计过程中如果时序不满足时需要多次迭代的。每次布局布线后都会通过QRC抽取连线寄生参数,配合timing library得到当前的SDF时序反标信息,从而帮助设计人员对时序违背的路径进行修改。一般来讲,在时序收敛前用SDF分析帮助修改设计,时序满足后,利用SDF进行动态仿真double check下时序满足情况。

四、如何反标sdf文件?

较为常见的方法是在bench中调用系统函数$sdf_annotate来完成。还有其他的方法,比如作为elaboration的选项指定等。$sdf_annotate的标准格式如下:

$sdf_annotate(“sdf_file”[,module_instance][,“sdf_configfile”][,“sdf_logfile”][,“mtm_spec”][,“scale_factors”][,“scale_type”]);

其中:

-

“sdf_file”: 指定SDF文件的路径。

-

“module_instance”: 指定反标设计的范围(scope)

-

“sdf_configfile”: 指定SDF配置文件

-

“sdf_logfile”: 指定VCS保存error 和warnings消息的SDF日志文件。也可以使用+sdfverbose runtime option来打印所有反标消息

-

“mtm_spec”: 指定延迟类型"MINIMUM(min)", "TYPICAL(typ)“或者"MAXIMUM(max)”。

-

“scale_factors”: 分别指定min:typ:max的缩放因子,默认是"1.0:1.0:1.0"

-

“scale_type”: 指定缩放之前延迟值的来源。

在反标SDF后,specify块中定义的延迟不再有用,取代的将是SDF文件中的延迟。

pre gate sim

前门级仿真使用综合后的网表进行的,一般综合时会在ss corner下完成,而用于功耗分析的前门级仿真会在tt corner下进行,因此在用vcs仿真时需要设置+nospecify+notimingcheck,即使加了反标sdf的语句:-sdf min:tb_top.u_asic_top:$(pre_sdf),也是需要设置+nospecify+notimingcheck。

pre gate sim是没有路径延时的,但存在cell内部的延时。如果pre gate sim仿真是使用的tt corner,而网表使用的是ss corner,则在pre gate sim仿真时会出现时序违例,仿真错误的情况,因此需要+nospecify和+notimingcheck。

为什么power 只需要在typical corner 做sign off?

关于tt corner、ss corner可以参看如下链接:

Corner芯片TT,FF,SS_tt corner_别想太多的博客-CSDN博客

在使用VCS仿真时使用的参数设置可参考如下网址:

仿真条件+nospecify +notimingcheck +delay_mode_zero的区别_no specify_风起云涌66的博客-CSDN博客

post gate sim

post gate sim是对在PR之后的网表和sdf进行功耗分析,在PR之后已经添加了完整的路径延时且不论是在SS还是TT corner下都应该能满足时序要求实现芯片功能,因此在进行gate sim仿真时不能使用nospecify和notimingcheck,需要把所有的时序都反标上去,这样才能尽最大限度的模拟真实芯片工作时的情况(如不同信号的延时导致毛刺的产生,导致功耗增大)。

同时,post gatesim也是最终网表的时序检查,当然时序检查的另一个方法是静态时序分析(STA)。

在进行post gate sim时会出现某个或者某些寄存的初始值为x,由于X的传播导致post gate sim无法正常仿真下去;同样某些memory也存在未初始化最开始的输出为X,由于X传播导致仿真不能继续。因此需要在进行仿真时需要将它们进行初始化,初始化这里用config_file.txt文件。

config_file.txt文件里的内容格式如下所示

defaultvalue x

tree tb_top.asic_top.u_module_a 0 random

这里“0”表示hierarchy中的层级,和dumpfsdb里的层级一个用法,“random”表示为将指定层级的寄存器或者存储器初始化为某个随机的确定值。

如果芯片中存在跨时钟域的同步处理,在post gate sim中可能会出现同步器件时序违例的情况,此时需要对同步器件进行针对性的notimingcheck,此处用config_list.f文件进行处理。

config_list.f文件里的内容如下所示

instance {tb_top.u_asic_top.u_module_b.u_sync1_reg} {noTiming};

以上两个文件需要在vcs仿真选项里手动加上,如:+vcs+initreg+config_list.f+../config_filt.txt \

gatesim debug技巧小记

(1)用gatesim的波形和同一个case的功能仿真波形对比分析;

(2)将门级网表和rtl的Verdi都打开,追信号用rtl代码对比分析溯源;

(3)门级网表的波形需要核对,比较的除了相应的标志信号,还需要比较数据,如最终输出的数据、输入到ram的数据作为每次门级网表波形正确的判断标准;

(4)在追数据X态时,使用Verdi中显示数据状态的功能,可以使用快捷键——键盘的x;

(5)在追数据X态时,需要从整体架构设计出发考虑,结合架构进行追溯X态信号的出处;

(6)需要明白复位信号和时钟信号的最开始的先后顺序,若顺序不当则会导致错误时序;同时也需要先确认模块的时钟信号和复位信号正确;

(7)跨时钟域信号的第一级寄存器时序违例可以忽略,写在config.list 文件中;

(8)mem有时需要初始化,未初始化会导致数据无法正常读写,可以在tb里面初始化mem,初始化方式之一:

initial begin #10; for (int i=0;i<128;i++)begin tb_top.u_digital_top.u_a.u_mem.mem[i]=0; end end

(9)rom文件的.rcf文件是否加载正确,可以查看rom的.v文件中memread处加载的.rcf文件是否正确(包括路径是否存在,里面的数据是否正确);

(10)mem的控制信号是否正确;

补充1 saif文件生成

在进行pre gatesim时,有时需要将fsdb波形文件转换成saif文件,用于进行功耗优化。用于转换saif的fsdb生成有一定的要求,格式可参考如下:

$fsdbDumpfile("xx_xx_xx.fsdb");

$fsdbDumpvars(100,"tb_top.u_top_module","+all");

注:tb即testbench的意思,在这个fsdb中不需要tb里信号的内容,因此要将层级直接引用到芯片逻辑的顶层。

将生成好的fsdb文件用fsdb2saif的命令直接在terminal中转换,格式如下:

fsdb2saif xx_xx_xx.fsdb -o xx_xx_xx.saif

如果波形文件过大,只需截取某段时间的波形,命令为:fsdb2saif xx_xx_xx.fsdb -bt 100ns -et 300ns -o xx_xx_xx.saif

补充2 仿真环境建立

可以比对一下功能仿真、pre gatesim和post gatesim的仿真设置。

功能仿真的makefile

VCS_OPTION= -V -Mupdate -full64 -debug_pp -sverilog +v2k +notimingcheck +no_tck_msg \ -P /tools/Synopsys/Verdi2017-SP1/share/PLI/VCS/linux64/verdi.tab \ /tools/Synopsys/Verdi201712-SP1/share/PLI/VCS/linux64/pli.a \ +vcs+initreg+config+config_file.txt \ +nospecify \ +define+vcs+sdfverbose+ASIC+FSDB+$(DF)+$(TC) \ -Marchive=128+noline-transport-pathpulse -timescale=1ns/1ps -notice \

pre gatesim仿真的makefile

VCS_OPTION=-V -Mupdate -full64 -debug_pp -sverilog +v2k +notimingcheck +no_tchk_msg \ -P /tools/Synopsys/Verdi2017-SP1/share/PLI/VCS/linux64/verdi.tab \ /tools/Synopsys/Verdi201712-SP1/share/PLI/VCS/linux64/pli.a \ +vcs+initreg+config+config_file.txt \ +nospecify \ -sdf min:tb_top.u_asic_top: /xx/xx/xx/xx_pre.sdf \ +vcsd+v2k+pathpulse+delay_mode_path+fsdb \ +define+vcs+ASIC+FSDB+$(DF)+$(TC) \ -Marchive=128+noline-transport-pathpulse -timescale=1ns/1ps -notice

post gatesim仿真的makefile

VCS_OPTION=-V -Mupdate -full64 -debug_pp -sverilog +v2k +negdelay +sdfverbose +neg_tchk \ -P /tools/Synopsys/Verdi2017-SP1/share/PLI/VCS/linux64/verdi.tab \ /tools/Synopsys/Verdi201712-SP1/share/PLI/VCS/linux64/pli.a \ -sdf min:tb_top.u_asic_top: /xx/xx/xx/xx_post.sdf \ +vcsd+v2k+pathpulse+delay_mode_path+fsdb \ +optconfigfile+../config.list +vcs+initreg+config+../config_file.txt \ +define+vcs+ASIC+FSDB+$(DF)+$(TC) \ -Marchive=128+noline-transport-pathpulse -timescale=1ns/1ps -notice

而compile的设置除了VCS_OPTION外其它都一样

compile:

vcs $(VCS_OPTION) \ -f /xx/xx/filelist.f \ -top sim_top_name \ -l /xx/xx/log/xxx_compile.log; \ ./simv+no_pulse_msg +fsdb+force \ -cm line+cond+tgl_fsm+branch -l /xx/xx/log/xxx_sim.log; \

注:这里的filelist.f应该包含(1)网表文件;(2)sdf文件;(3)网表中各种cell对应的Verilog模型的.v文件;(4)用于验证仿真的testbench文件。

补充3 将bin文件转成rom文件

如果是SOC级别的仿真,可能会存在直接将嵌入式人员导出的bin文件用于仿真的情况。SOC级别的功能运行是通过CPU读取指令来调动各个模块协调工作来实现的,而嵌入式导出的bin文件就是cpu运行的指令文件,只不过是二进制文件。虽然仿真中指令ROM中存储的也是二进制文件,但仿真时需要ROM的行为级模型中初始化调用的可能不是二进制格式,因此需要将bin文件转换成ROM能识别调用的文件格式,因此可以通过linux的od命令来实现。

浙公网安备 33010602011771号

浙公网安备 33010602011771号