计算机存储单元结构

存储层次结构概况

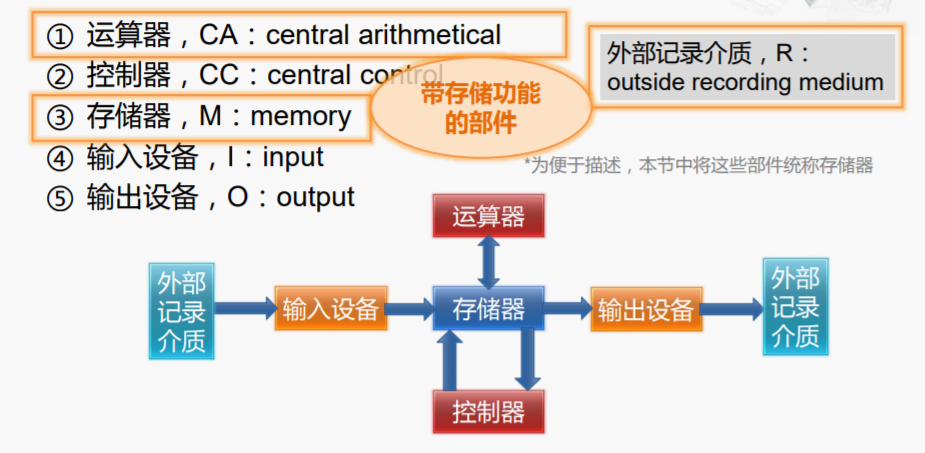

这是我们非常熟悉的冯·诺依曼计算机结构, 那这其中哪些部件和存储功能有关呢?

存储器和外部记录介质肯定具有存储功能,另外还有一个自带存储功能的运算器,为了描述方便,我们把这些部件统称为存储器。那么我们看一下计算机中对存储器有哪些要求 ?

1、首先存储器当中应该保存了将要运行的程序和需要运算的数据,那这些内容在系统通电启动的时候就应该在存储器当中了,而且在断电之后也不会丢失。那么具有这样特定的存储器我们称之为非易失性存储器。而断电后存储的信息就会丢失的存储器则称为易失性存储器。

- 易失性存储器:主存和CPU中的通用寄存器都是易失性的存储器,断电后信息就丢失了

- 非易失性存储器:bios芯片和硬盘:在系统通电之后CPU必须要从bios芯片开始执行程序,然后这段程序把硬盘等设备配置好之后再将更多的程序和数据从硬盘搬运到内存,之后CPU才可以在内存里执行程序。 因此在系统中必须要有非易失性的存储器。

2、其次,这样的存储器肯定得是可读又可写的。那在这个结构当中硬盘和主存都是可读可写的, 而bios芯片则是一个只读的芯片,倒不是说它完全不支持写操作,而是对它的写需要 借助特殊的设备或者特殊的操作过程,非常的麻烦,无法支持经常性地写入数据。

3、最后,存储器最好是能够支持随机访问。所谓随机访问是指对存储器当中任何一个数据的访问所花费的时间与这个数据所在的位置没有关系。对主存的读写和Bios芯片的读都是支持随机访问的。而硬盘内部实际上是由多个盘片构成,这些盘片处于高速旋转的状态,并由一个机械的读写头去寻找需要访问的数据的位置。这就不是随机访问的模式,而且由于期中有机器部件的存在,速度就变得非常的慢。

DRAM和SRAM

SRAM比较快,DRAM比较慢,SRAM比较贵,DRAM比较便宜,记住这些结论是很容易的, 但是比是什么更重要的是为什么,我们就从电路的级别来探索DRAM 和SRAM为什么会具有他们这样各自的特点。

DRAM

这是我们计算机中使用的内存条,准确的说叫内存模组,这上图这个内存模组中共有8块DRAM芯片。

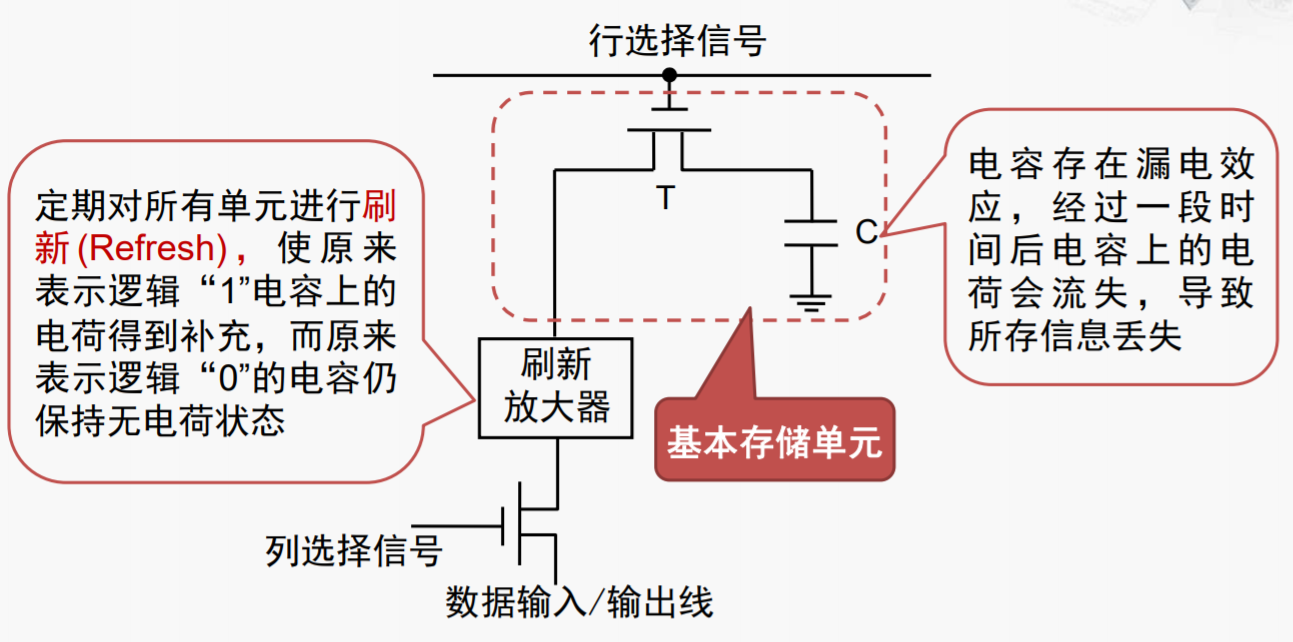

DRAM芯片内部核心结构就是这个存储阵列,由若干行、若干列构成。如果外部给定行地址和列地址,DRAM中有地址译码逻辑电路,就能选中一个存储单元,而每个存储单元往往包含若干个比特,常见的有4比特和8比特,每个比特都采用如下的电路结构,称为DRAM的基本存储单元。

DRAM的基本存储单元(1bit)

这个基本单元就是都过一个电容来保存一个比特,写入就是由外部的数据线驱动对电容进行充电或者放电的操作,从而完成写入0或1,读操作则是由电容对外部的数据信号线进行驱动,从而完成读出0或1。

这个电路非常简单,由于电容存在漏电效应,需要定期“刷新”以保证DRAM的存储信息的正确性。如果原先保存的数据是0,则通过刷新使它保持无电荷状态,如果原先保存的数据为1,则补充这个电容的电荷。

现在PC机中大多是采用DRAM作为主存储器(即内存),DRAM也有很多种不同的实现,比如SDRAM这个s是同步的缩写,那它是在DRAM的基本结构基础上对输入输出接口进行时钟同步。从而提高了读写的效率,而现在更为常用的内存 则是在SDARAM的基础上又进行了进一步的改进,比如说这些年有DDR1,DDR2,DDR3, 这些不同的内存标准都是在SDRAM的基础上进行的改进和升级。

总体来说,DRAM的基本存储单元简单,所以能做到很高的集成度,而且功耗也比较低,我们可以用较低的成本制造大容量的DRAM芯片。它的读写是通过充放电的方式,所以速度较慢,而且它还需要定期刷新,这进一步影响了DRAM的读写性能。

SRAM

SRAM的基本存储单元(1bit)

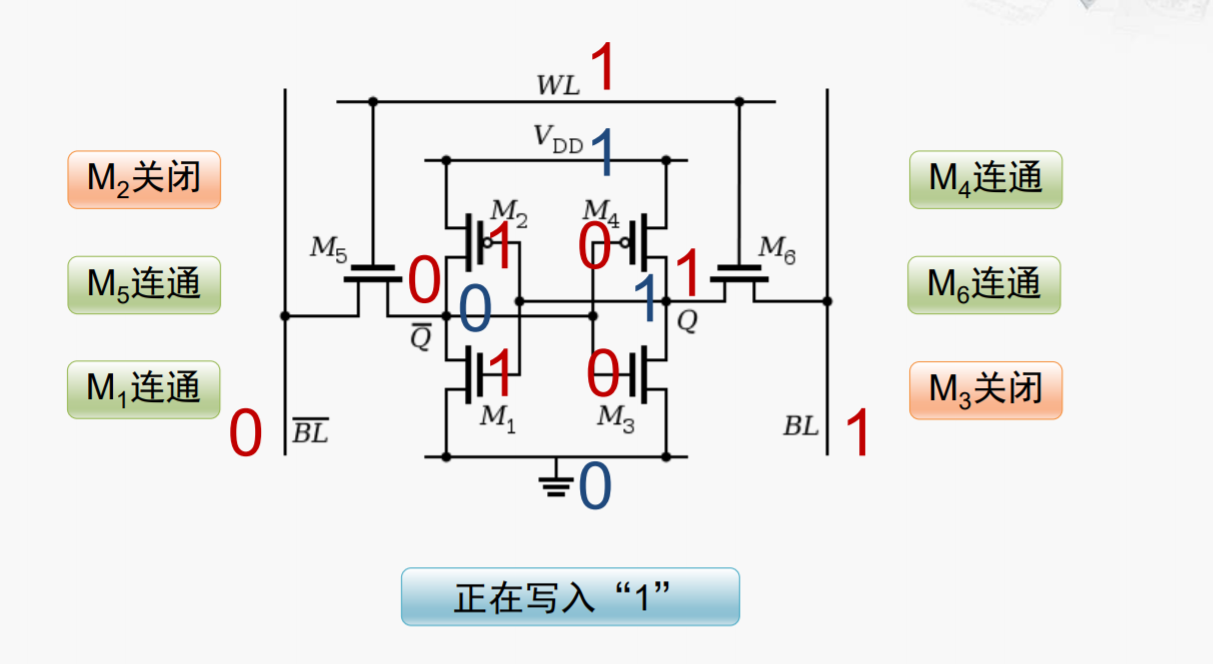

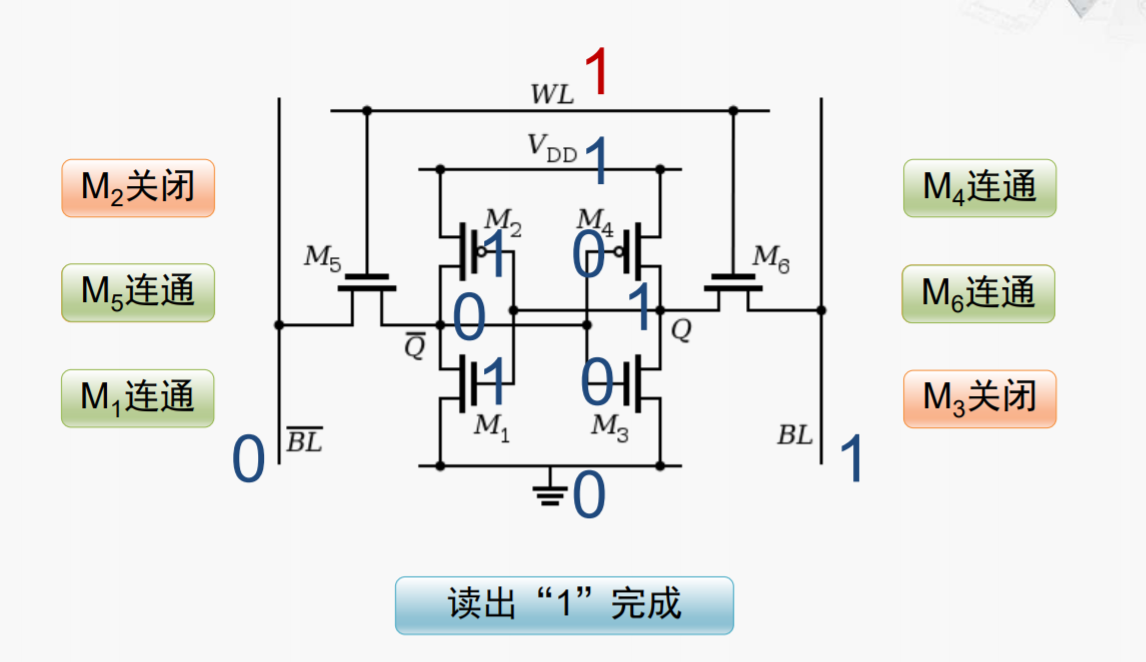

这个结构共有6个晶体管,M1~M6表示,6个合在一起才可以保存一个比特。对外有3个接口信号,BL、~BL用于传送读写时的数据,WL用于标识外部是否能访问这个存储单元。

写入数据1时的工作过程:

- 首先,只有通电,VCC总为1,地总为0

- 将BL置为1,这样~BL为0,要写入的数据就准备好了

- 然后我们需要访问这个SRAM单元,要将WL置为1,随之M5、M6的gate端也为1

- 根据NMOS、PMOS的性质,可推导出电路保持稳定且不会有冲突(分析略),Q = 1,~Q = 0

- 因为晶体管的速度很快,写入过程也很快,等这几个晶体管稳定后,写入过程就结束了

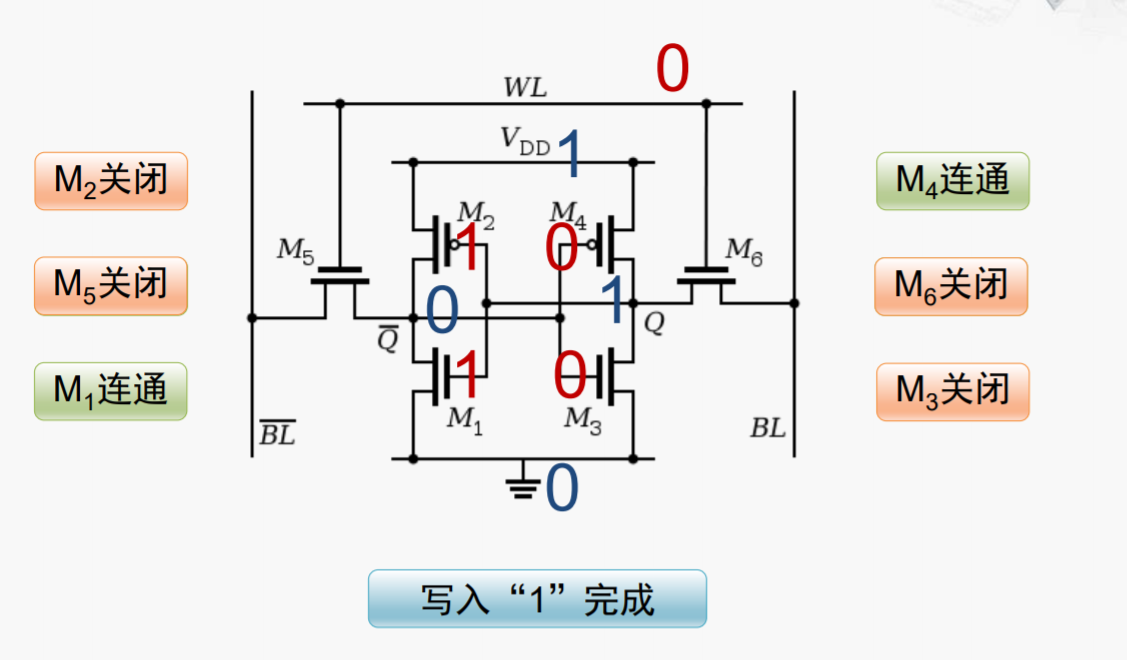

- 现在可以撤销WL信号了(即由1变0),从而M5、M6关闭,BL和~BL也可以撤销了

- M4处于导通状态,电源对传到Q,使得M1、M2的Gate端始终为1

- 那么在这4个晶体管的相互作用下,SRAM就保持住了刚才写入的1

- WL保持为0,则存储的数据始终为1,当然不能断电(断电Vdd没有了)

读出数据1时的工作过程:

- 把WL置为1,因此M5、M6会是导通状态

- 此时外部并不驱动BL和~BL,它们会通过M5、M6被SRAM驱动

- BL被驱动为1,~BL被驱动为0

晶体管的开关速度远比电容充放电速度快,所以SRAM更快。但是它每存储一个比特就需要6个晶体管,晶体管数量多会造成芯片面积大,带来集成度和价格高的问题。同时每个晶体管都是要耗电的,晶体管越多功耗就越高。现在CPU中的高速缓存都是用SRAM实现的。