微处理器架构和存储器系统

1. 微处理器介绍

处理器核/CPU核:通常指微控制器产品或芯片产品内部的处理器,不包括内存系统、外围设备和其他系统支持组件(如电源管理、,时钟产生电路)。在某些文章中,“核”一词也可能指处理器内部处理软件执行的部分,不包括中断控制器和调试支持硬件。

微处理器:包含一个或者多个处理器的芯片设备,主要用于处理计算任务,也可处理控制任务。系统设计人员通常需要添加内存和可能的附加外围硬件来构建一个完整的微处理器系统。术语“微处理器”和“CPU”在某些情况下可以互换(如果指芯片设备)。

•微控制器:包含处理器的芯片设备,设计用于处理控制和计算任务。该芯片通常包含存储系统(例如,程序ROM用的flash存储器和静态随机存取存储器(SRAM)以及一些外围设备)

1.1 基本微控制器

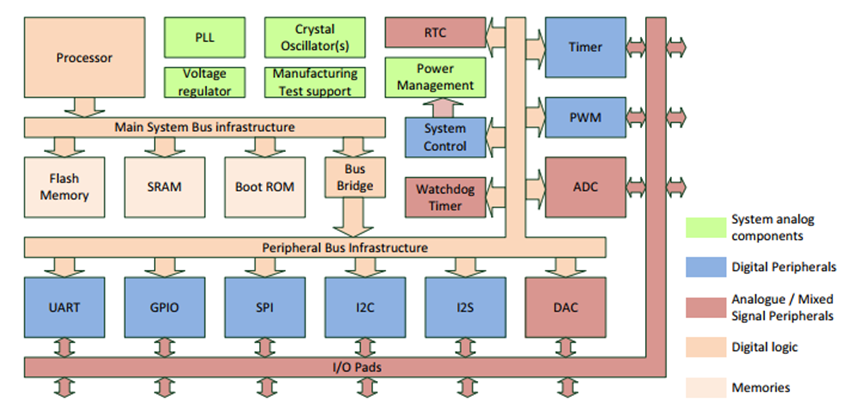

基本微控制器内部可以有许多组件。例如,下图中显示了一个简化的框图:图中有许多首字母缩略词。

如图所示,微控制器中可能有许多组件(更不用说以太网、USB等其他复杂接口)。在某些微控制器中也可以找到直接内存访问(DMA)控制器和硬件加速器的加密功能;DMA:存储器之间的数据搬移。

芯片可以集成CPU/ARM处理器,并包含SD,USBNandFlash,SPI等高速通讯接口以及GPIO,UART,I2C等通用接口。这些IP挂在AMBA总线上,CPU通过AMBA总线和这些外设IP通信。芯片可能会有很多IP组成,包括模拟IP(电源,PLL,时钟),Designware IP(根据具体实现可配置的IP,例如乘法器加法器的位宽),soft IP。

架构设计文档:功能列表,软硬件划分,软硬件协同工作,硬件模块功能描述

微架构设计文档:功能框图(详细),各模块详细描述包括模块框图,信号描述,模块功能定义

微控制器中的典型组件

ROM:Read Only Memory,只读存储器,用于程序代码存储的非易失性存储器。

FLASH:闪速存储器,一种特殊类型的只读存储器,可多次重新编程,通常用于存储程序代码。

SRAM:Static Random Access Memory,静态随机存取存储器,用于数据存储(易失性),SRAM内存条,存储平时运行时的程序和数据。

PLL(Phase Lock Loop)锁相环,基于参考时钟产生可编程时钟频率。

RTC:Real Time Clock,实时时钟,低功耗计时器,用于计时秒数(通常在低功耗振荡器上运行),在某些情况下还用于分钟、小时和日历功能。

GPIO:General Purpose Input/Output,通用输入/输出一种具有并行数据接口的外设,用于控制外部设备和读取外部信号状态。

UART:Universal Asynchronous Receiver/Transmitter,通用异步接收器/发送器,用于处理简单串行数据协议中的数据传输的外设。

I2C:Inter-Integrated Circuit,内部集成电路,以串行数据协议处理数据传输的外围设备。与UART不同,它需要时钟信号,并且可以提供更高的数据速率。

SPI:Serial Peripheral Interface,串行外设接口,用于片外外设的另一个串行通信接口。

I2S:Inter-IC Sound,内部IC Sound,专门用于音频信息的串行数据通信接口。

PWM:Pulse Width Modulator,脉冲宽度调制器,具有可编程占空比的输出波形的外围设备。

ADC:模数转换器:将模拟信号电平信息转换成数字形式的外围设备。

DAC:数模转换器将数据值转换成模拟信号电平的外设。

Watchdog:看门狗定时器,一种可编程定时器装置,用于确保处理器正在运行程序。启用时,运行的程序需要在一定的时间间隔内更新看门狗计时器。如果程序崩溃,看门狗超时,这可以用来触发复位或严重中断事件。CPU需要隔一段时间告诉watchdog处于正常状态,若很长一段时间watchdog没收到CPU的信息,则可能CPU出现问题,陷入死循环等,此时就要复位。相当于一种保护机制.

Pflash:存储系统程序启动代码,或者用户程序,上电时读。

单周期读写,读写只需要一个周期,每个时钟周期都可以读写出数据,多周期读写就需要很多等待时间。

1.3 ARM Cortex-M0总线系统

Cortex-M0处理器具有32位系统总线接口,以及32位地址线(4GB的地址空间)。系统总线基于 AHB Lite总线协议(高级高性能总线),该协议定义在高级微控制器总线架构( Advanced Microcontroller Bus Architecture)(AMBA)标准中。

利用相应的存储器接口逻辑,系统总线接口可以连接不同类型的存储器。总线接口可以支持32位、16位和8位数据的读/写传输,且支持等待状态和从机响应(可以是OK或ERROR)。连接到处理器的存储器设备可以是任意大小和宽度的,例如存储器设备可以是8位、16位或64位宽,但是在和不同宽度的总线相连时需要加上其他的硬件,32位的片上存储器一般可以将设计的复杂度降到最低。

AHB Lite协议为存储器系统提供了高速高性能的访问方式,外设等较慢的设备则通常需要利用其他的总线模块,如下图所示。在ARM微控制器中,外设总线系统一般采用APB(高级外设总线)协议,APB通过一个总线桥连接到 AHB Lite上,并且运行的时钟频率和AHB系统总线不同。APB的数据链路也是32位的,但由于外设的地址区域往往较小,因此地址线一般要少于32位。

由于主总线系统和外设总线是相互分离的,有些情况下时钟频率控制也不同,应用程序在访问外设前需要初始化微控制器的时钟控制硬件。有些情况下,一个微控制器可能有多个外设总线段,并且每个段运行在不同的时钟频率下,除了可以让系统的某些部分运行在较低频率下以外,独立的总线段还可以停止某些外设系统的时钟,这样能够降低功耗。

根据微控制器设计的不同,有些高速外设可以不连到APB,而是连接到 AHP Lite上这是因为与APB相比,基于 AHH Lite协议的传输每次需要的时钟周期数更小。总线系统的行为从许多方面都影响着系统操作,以及开发者对储器系统的认识。

1.4 存储器系统

所有处理器系统都需要存储器。微控制器一般都需要Flash或掩码ROM等非易失性存储器(NVM)进行程序存储,用SRAM(静态随机存取存储器)之类的存储空间等实现数据的写和读操作。SRAM通常用于数据变量,栈存储以及动态存储分配的堆(例如,在使用C语言中使用的alloc()函数时)。

对于大多数微控制器,存储器是集成在微控制器芯片内部的。这使这些微控制器更易于使用(所需的外部连接更少,并降低了最终嵌入式产品的成本)。但是,片上Flash和SRAM存储器的大小是有限的,许多低成本微控制器具有大约128 KB(或更少)的Flash和大约32 KB(或更少)的SRAM。

许多微控制器中还存在一个 Bootloader ROM,这样微控制器可以在Flash存储器中的用户应用启动前执行单片机(MCU)厂商提供的一段程序。 Bootloader ROM可能还会提供多个启动选项,以及 Flash编程功能,同时可以设置内部时钟源或内部参考电压的厂内校准数据。有些微控制器设计不允许软件开发人员修改或擦除 Bootloader.

所以通常的CPU或者MCU内部都有一个ROM, 用来存储BOOT load 程序,上电时,自动启动该段程序的执行,该程序中还存在将EEPROM内的程序搬到SRAM或者配置寄存器的代码,即读EEPROM 内容到SRAM的程序。

若工程需要在系统中增加更多的存储器,系统设计人员则需要选择一款支持外部存储器接口的微控制器。需要注意的是,许多微控制器产品是不支持片外存储器系统的。即使微控制器支持外部存储器,每次访问片外存储器系统可能会花费几个时钟周期,因此系统性能可能低于所有数据都放入片上存储器的系统。

传统的微控制器需要单独的NVM和SRAM,由于和NVM类似的 Flash存储器需要复杂的编程过程,因此不适合用作数据存储(例如需要频繁更新的数据变量和栈)。

近年来,有些微控制器产品开始使用FRAM(铁电RAM或MRAM(磁阻RAM),利用这些技术,同一个存储器块可用于程序代码和数据存储,且这种存储器系统在完全掉电后可以在不丢失RAM中数据的情况下继续运行(传统的方法则需要将SRAM置入一种会带来漏电流的状态保存模式),这也是其一大优势。尽管现有的基于Cortex-M处理器的微控制器产品并没有使用这些存储器技术,但是 Cortex- M处理器并没有限制这些技术,因此也是可以使用的.

微控制器中NVM存储器的一个重要特点在于,和SRAM的访问速度相比,NVM技术相对较慢。因此,当处理器总线比存储器的最大访问速度高时,Flash或FRAM存储器的总线接口就需要插入等待状态。例如,片上Flash存储器的访问速度一般介于25MHz到50MHz之间(有些高速Flash存储器可以运行在100MHz以上,但由于它们的功耗相对较高,因此一般不会用在低功耗微控制器设备中)

1.4.1 存储器映射

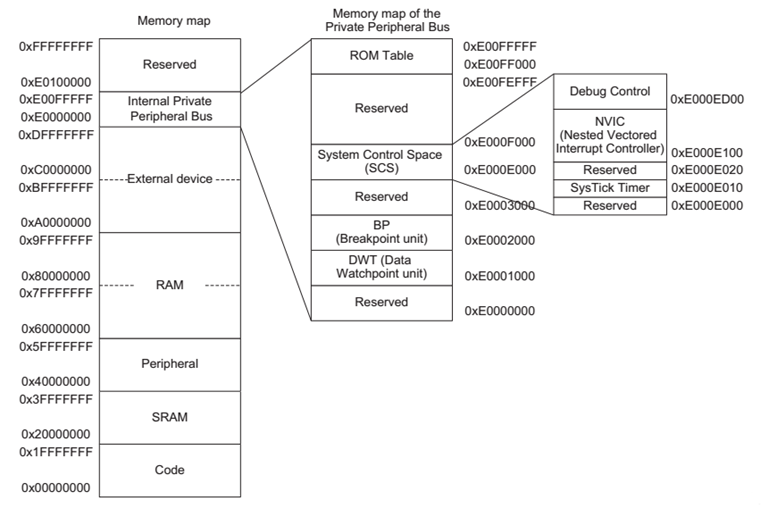

Cortex-M0和 Cortex-M0+处理器的4GB存储器空间从架构上被分为多个区域(见图7.2),每个区域对应一种推荐的用途并且各区域的操作方法也有所不同,存储器区域的定义使得 ARM Cortex微控制器的存储器划分相似,这有助于微控制器间的软件移植。

尽管存储器映射已经被架构预先定义,存储器映射的实际用法却可以非常灵活,使用中的限制也不多。例如,用于外设的存器区域不允许程序代码执行,并且为了保证软件的可移植性,一些内部部件的存储器地址是固定的。

下面介绍每个区域的用途:

1.代码区域(0x00000000-0x1FFFFFFF)

代码区越的大小为512MB,它主要用于存储程序代码,其中包括作为程序映像一部分的向量表,另外也可以用作数据存储器(连接到RAM)。

2.SRAM区域(0x20000000-0×3FFFFFFF):SRAM区域位于存储器映射的第二个512MB,它主要用于数据存储,其中也包括栈,它还可以用于程序代码存储。例如,有些情况下,数据有可能需要从低速外部存储器复制到SRAM中,并且在SRAM中执行程序。尽管该区域被命名为SRAM,实际的存储器也可以是SRAM、SDRAM或其他可读写的设备。

3.外设区域(0×40000000-x5FFFFFFF):外设区域的大小为512MB,主要用于外设以及数据存储。外设区域中不允许执行程序。连接到该存储器区域的外设可以是 AHB Lite外设,也可以是APB外设(通过总线桥)

4.RAM区域(0x60000000-0x9FFFFFF)

RAM区域包括两个512MB的块,这样就得到一个总共1GB的区域。这两个512MB存储器块主要用于数据存储,并且多数情况下RAM区域可使用1GB的连续存储器空间.RAM区域中还可以执行程序代码,这两个区域的唯一差异在于它们的存储器属性不同。如果设计中存在一个系统级的缓存(level-2缓存),这个差异就会带来缓存行为的差异.

5.设备区域(0xA0000000-0xDFFFFFFF):外部设备区域包括两个512MB的存储器块,总共得到1GB空间.两个512MB块主要用于外设和IO,设备区域不允许程序执行,但可用作通用数据存储。同RAM区域类似,设备区域的两部分也有不同的存储器属性

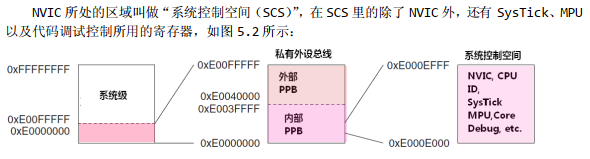

6.内部私有外设总线(PPB)(0xE000000×E00FFFFF):内部PPB存储器空间用于处理器内部的外设,包括向量中断控制器(NVIC)和调试部件等,内部PPB存储器空间的大小为1MB,并且这个区域内不允许执行程序。

在PPB存储器区域中,有一段特殊的存储器区域被定义为系统控制空间(SCS),其地址范围为0xE000E000-0xE000EFFF.该区域包括中断控制寄存器,系统控制寄存器和调试控制寄存器等,NVIC寄存器也是SCS存储器空间的一都分,SCS中还包含一个可选定时器Systick.

7.保留存储器空间(0xE0100000× FFFFFFFF)

存储器映射的最后511MB为保留存储器空间,这段空间在某些微控制器中预留为供应商特定的用途。

尽管 Cortex-M0处理器的存储器映射是固定的,存储器的用法却可以非常灵活。处理器可以在SRAM区域包含多个SRAM存储器块,CODE区域也是一样,并且外部RAM区域也可以执行程序,微控制器供应商可以增加它们自己的系统级存储器特性,例如有必要的话可以增加系统级缓存.对于一个典型的 Cortex-M0微控制器,其实际系统的存储器映射通常包含以下部分:

(1). Flash存储器(用于程序代码)

(2).内部SRAM(用于数据)

(3).内部外设

(4).外部存储器接口(用于外部存储器和外部外设,这是可选的)

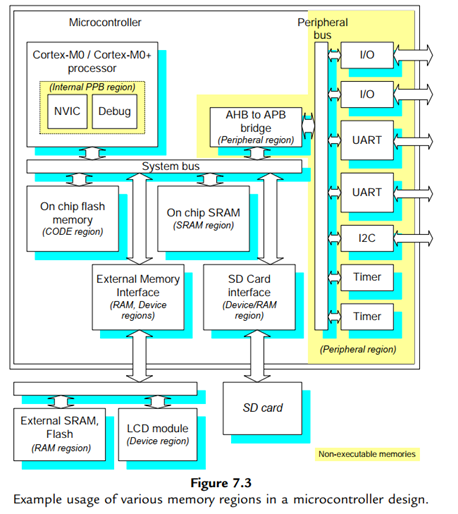

(5).其他外部外设的接口(可选)。将这些部件放到一起可以得到如图所示的微控制器示例。

上图演示了一些存储器区域应该怎么用,不过,在许多低成本微控制器中,系统设计中没有外部存储器接口或者SD卡接口,在这些情况下,外部RAM或外部设备区域等存储器区域可能会用不上。

1.4.2 程序存储器

Cortex-M0/M0+的程序存储器一般使用片上 Flash存储器,不过,程序也可以存储在外部或者使用其他类型的存储器设备(如外部SPI flash, EEPROM)。当 Cortex-M0/M0+处理器从复位中启动时,它会首先访问0地址的向量表,从而取得MSP(MSP:主栈指针)的初始值和复位向量,然后它就可以从复位向量开始执行程序。要保证系统正常工作,系统中需要有合法的向量表和合法的程序存储器,这样处理器才不会执行恶意软件代码。

要实现这个目的, Flash存储器一般是从地址0开始的。不过,在用户编程以前,市面上的微控制器产品的 Flash存储器中可能没有任何程序。为了保证处理器可以正确地启动,有些基于 Cortex-M0的微控制器含有一个 Boot loader,这是个位于微控制器芯片上的一小段程序,它会在处理器上电,利用复位按键执行程序跳转,而且如果 Flash存储器已编程的话,它会跳转到 Flash中的用户程序执行。Boot loader由芯片供应商预先编程,有时它位于片上Flash存储器并且与用户程序是分离的(这样用户更新程序也不会影响到 Boot loader),而其他情况下Boot loader则会位于和可编程程序存储器相互独立的非易失性存储器中(防止用户意外擦除 Boot loader)。

当 Boot loader存在时,微控制器通常会在系统总线上使用一种存储器映射切换特性,也就是“重映射”( remap)。存储器映射的切换由硬件寄存器控制, Boot loader执行时会设置这些寄存器。系统可以使用多种重映射方案,一种常见的处理是, Boot loader会在上电阶段通过地址别名被重映射到存储器的开头(见图7.4)。

Boot loader可能还具有其他特性,比如硬件初始化(时钟和PLL设置)、多种启动配置、固件保护,甚至可以用作 Flash擦除工具。系统总线上的存储器映射特性并不是 Cortex-M0/M0+处理器的一部分,因此,不同微控制器供应商产品的设计不同。

ARM微控制器使用的另外一种重映射特性为SRAM块可以重映射到地址0上(见图7.5)。微控制器使用的非易失性存储器如Flash等要比SRAM慢,如果微控制器运行在较高的时钟频率下, Flash存储器中的程序在执行时就会需要插入等待状态。而将SRAM重映射到地址0后,程序就可以被复制到SRAM并以最快速度执行,这样会避免取向量表时出现等待,否则会增加中断等待的时间。

每一个从设备都占用系统中的一段地址空间,所有的从设备都是可寻址的,寄存器/存储器都是存储器映射方式访问,CPU/IP读写其他IP的数据类似于读写存储器

1.4.3 Boot/Bootload

Boot在计算机专业英文中的意思是“引导”,它是计算机系统(上电)复位后CPU的第一个机器动作。简要地说,Boot就是引导CPU如何装入机器指令。最简单的Boot动作就是8位单片机系统复位后从复位向量中取出跳转指令,转移到用户程序代码段执行的这个过程。

通常,在计算机系统中,(上电)复位后除了执行Boot动作,还跟随着一个Load过程。一般情况下,该Load从低速非易失性存储器中“搬运”一些数据到高速易失性存储器中。Boot和Load连续执行,一气呵成,我们称之为Bootload。最典型的例子之一就是DSP实时信号处理系统,系统上电后,将存储在EEPROM中的实时信号处理程序复制到系统的RAM中,然后CPU直接从RAM中读取机器指令运行。

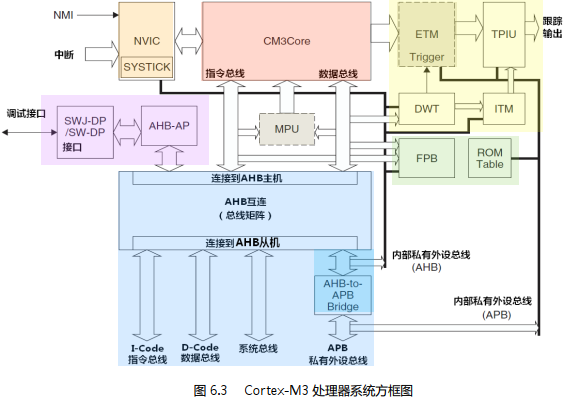

ARM Cortex-M3总线架构图和存储系统

系统图

- NVIC 嵌套向量中断控制器

- SYSTICK Timer 一个简易的周期定时器,用于提供时基, 亦被操作系统所使用

系统滴答定时器是一个非常基本的倒计时定时器,用于在每隔一定的时间产生一个中断,即使是系统在睡眠模式下也能工作。它使得 OS 在各 CM3 器件之间的移植中不必修改系统定时器的代码,移植工作一下子容易多了。 SysTick 定时器也是实现在NVIC 内部的。

- MPU 存储器保护单元(可选)

MPU 是一个选配的单元,有些 CM3 芯片可能没有配备此组件。如果有,则它可以把存储器分成一些 regions,并分别予以保护。例如,它可以让某些 regions在用户级下变成只读,从而阻止了一些用户程序破坏关键数据

- CM3BusMatrix 内部的 AHB 互连

- AHB to APB 把 AHB 转换为 APB 的总线桥

- SW-DP/SWJ-DP 串行线调试端口/串行线 JTAG 调试端口。通过串行线调试协议或者是传统的 JTAG 协议(专用于 SWJ-DP),都可以用于实现与调试接口的连接

- AHB-AP AHB 访问端口,它把串行线/SWJ 接口的命令转换成 AHB 数据传送

- ETM 嵌入式跟踪宏单元(可选组件),调试用。 用于处理指令跟踪

- DWT 数据观察点及跟踪单元,调试用。这是一个处理数据观察点功能的模块

- ITM 仪器化跟踪宏单元

- TPIU 跟踪单元的接口单元。所有跟踪单元发出的调试信息都要先送给它,它再Cortex-M3

- 转发给外部跟踪捕获硬件的。

- FPB Flash 地址重载及断点单元

flash地址重载是指:当CPU访问某条指令时,若该地址在FPB中“挂了号”,则将把该地址重映射到另一个地址,后者亦在编程FPB时指出。 实际结果是从映射过的地址处取指(通常,映射前的地址是flash中的地址,映射后的地址是SRAM中的地址,所以才是”Flash”地址重载)。此外,匹配的地址还能用来触发断点事件。

- ROM 表 一个小的查找表,其中存储了配置信息

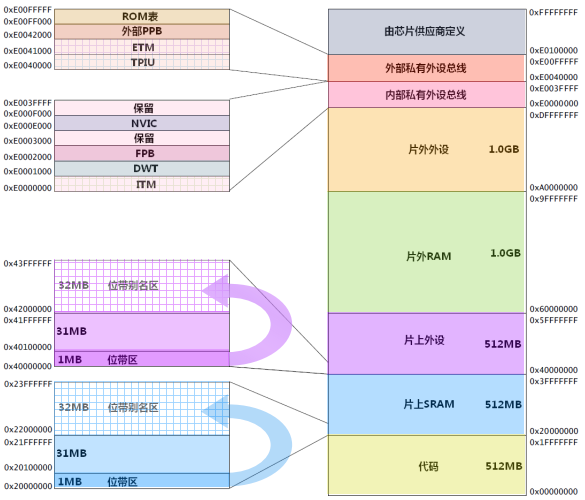

存储系统功能概览

第一,它的存储器映射是预定义的,并且还规定好了哪个位置使用哪条总线。

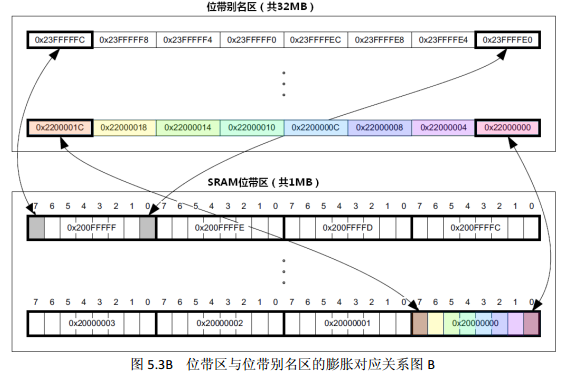

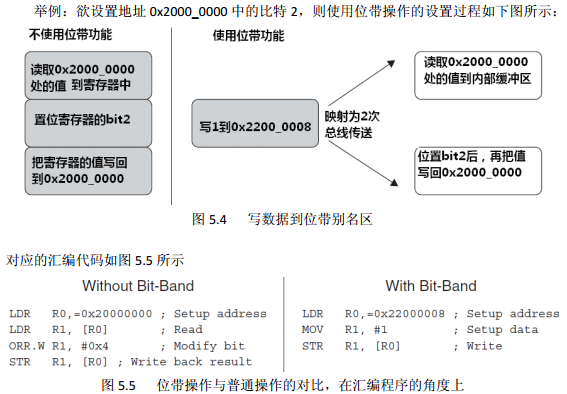

第二,CM3的存储器系统支持所谓的“位带”(bit-band)操作。通过它,实现了对单一比特的原子操作。位带操作仅适用于一些特殊的存储器区域中。

第三,CM3 的存储器系统支持非对齐访问和互斥访问。这两个特性是直到了 v7M 时才出来的。

最后,CM3 的存储器系统支持 both 小端配置和大端配置。

存储器映射

CM3 只有一个单一固定的存储器映射。这一点极大地方便了软件在各种 CM3 单片机间的移植。举个简单的例子,各款 CM3 单片机的 NVIC 和 MPU 都在相同的位置布设寄存器,使得它们变得与具体器件无关。尽管如此, CM3 定出的条条框框是粗线条的,它依然允许芯片制造商灵活细腻地分配存储器空间,以制造出各具特色的单片机产品。

存储空间的一些位置用于调试组件等私有外设,这个地址段被称为“私有外设区”。私有外设区的组件包括:

- 闪存地址重载及断点单元(FPB)

- 数据观察点单元(DWT)

- 仪器化跟踪宏单元(ITM)

- 嵌入式跟踪宏单元(ETM)

- 跟踪端口接口单元(TPIU)

- ROM 表

CM3的地址空间是4GB, 程序可以在代码区,内部 SRAM 区以及外部 RAM 区中执行。但是因为指令总线与数据总线是分开的,最理想的是把程序放到代码区,从而使取指和数据访问各自使用自 己的总线,并行不悖。

内部 SRAM 区的大小是 512MB,用于让芯片制造商连接片上的 SRAM,这个区通过系统总线来访问。在这个区的下部,有一个 1MB 的位带区,该位带区还有一个对应的 32MB 的“位带别名(alias)区”,容纳了 8M 个“位变量”,位带别名区里面的每个字对应位带区的一个比特。位带操作只适用于数据访问,不适用于取指。通过位带的功能,可以把多个布尔型数据打包在单一的字中,却依然可以从位带别名区中,像访问普通内存一样地使用它们。位带别名区中的访问操作是原子的,消灭了传统的“读-改-写”三步曲。地址空间的 512MB 范围由片上外设(的寄存器)使用。这个区中也有一条 32MB位带别名,以便于快捷地访问外设寄存器。例如,可以方便地访问各种控制位和状态位。要注意的是,外设内不允许执行指令。

1GB 的范围,分别用于连接外部 RAM 和外部设备,它们之中没有位带。两者的区别在于外部 RAM 区允许执行指令,而外部设备区则不允许。

0.5GB 的隐秘地带,属于 CM3 核心空间,包括了系统级组件,内部私有外设总线 s,外部私有外设总线 s,以及由提供者定义的系统外设。

私有外设总线有两条:

AHB 私有外设总线,只用于 CM3 内部的 AHB 外设,它们是:NVIC, FPB, DWT 和 ITM。

APB 私有外设总线,既用于 CM3 内部的 APB 设备,也用于外部设备(这里的“外部”是对内核而言)。 CM3 允许器件制造商再添加一些片上 APB 外设到 APB 私有总线上,它们通过 ABP 接口来访问。

CM3 中的 MPU 是选配的,由芯片制造商决定是否配上。

上述的存储器映射只是个粗线条的模板,半导体厂家会提供更展开的图示,来表明芯片中片上外设的具体分布, RAM 与 ROM 的容量和位置信息。

存储器访问属性

CM3 在定义了存储器映射之外,还为存储器的访问规定了 4 种属性,分别是:

- 可否缓冲(Bufferable)

- 可否缓存(Cacheable)

- 可否执行(Executable)

- 可否共享(Sharable)

CM3 片内没有配备缓存,也没有缓存控制器,但是允许在外部添加缓存。通常,如果提供了外部内存,芯片制造商还要附加一个内存控制器,它可以根据可否缓存的设置,来管理对片内和片外 RAM 的访问操作。如果配了 MPU,则可以通过它配置不同的存储区,并且覆盖缺省的访问属性。

- 代码区(0x0000_0000‐ 0x1FFF_FFFF)。该区是可以执行指令的,缓存属性为 WT(“写通”,Write Through),即不可以缓存。此区亦可写数据。在此区上的数据操作是通过数据总线接口的(读数据使用 D‐Code,写数据使用 System),且在此区上的写操作是缓冲的。

- SRAM 区(0x2000_0000 – 0x3FFF_FFFF)。此区用于片内 SRAM,写操作是缓冲的,并且可以选择 WB‐WA(Write Back, Write Allocated)缓存属性。此区亦可以执行指令,以允许把代码拷贝到内存中执行——常用于固件升级等维护工作。

- 片上外设区(0x4000_0000 – 0x5FFF_FFFF)。该区用于片上外设,因此是不可缓存的,也不可以在此区执行指令(这也称为 eXecute Never, XN)。

- 外部 RAM 区的前半段(0x6000_0000 ‐ 0x7FFF_FFFF)。该区用于片外 RAM,可缓存(缓FF_FFFF)。并且可以执行指令。

- 外部 RAM 区的后半段(0x8000_0000 – 0x9FFF_FFFF)。除了不可缓存(WT)外,同前半段。

- 外部外设区的前半段(0xA000_0000 – 0xBFFF_FFFF)。用于片外外设的寄存器,也用于多核系统中的共享内存(需要严格按顺序操作,即不可缓冲)。该区也是个不可执行区。外部外设区的后半段(0xC000_0000 – 0xDFFF_FFFF)。目前与前半段的功能完全一致。

- 系统区(0xE000_0000 – 0xFFFF_FFFF)。此区是私有外设和供应商指定功能区。此区不可执行代码。系统区涉及到很多关键部位,因此访问都是严格序列化的(不可缓存,不可缓冲)。而供应商指定功能区则是可以缓存和缓冲的。

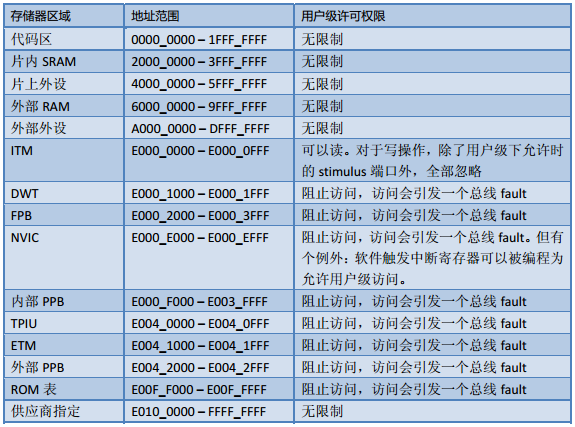

存储器缺省访问权限

CM3 有一个缺省的存储访问权限,它能防止用户代码访问系统控制存储空间,保护NVIC、MPU等关键部件。缺省访问许可在下列条件时生效:1)没有配备 MPU 2)配备了 MPU,但MPU未使能。

位带操作

位带操作,可以使用普通的加载/存储指令来对单一的比特进行读写。在CM3中中,有两个区中实现了位带。其中一个是 SRAM 区的最低 1MB 范围,第二个则是片内外设区的最低 1MB 范围。这两个区中的地址除了可以像普通的 RAM 一样使用外,它们还都有自己的“位带别名区”,位带别名区把每个比特膨胀成一个 32 位的字。当你通过位带别名区访问这些字时,就可以达到访问原始比特的目的。

位带操作的优势

通过GPIO控制LED点亮或者熄灭;对共享资源的互锁访问。

端模式

在 CM3 中, 是在复位时确定使用哪种端模式的,且运行时不得更改。指令预取永远使用小端模式,在配置控制存储空间的访问也永远使用小端模式(NVIC),另外外部私有总线地址也只使用小端模式。

存储保护单元MPU

在Cortex-M3处理器中可以选配一个存储器保护单元(MPU),它可以实施对存储器(主要是内存和外设寄存器)的保护,从而使软件更加健壮和可靠。如果打算启用MPU,则在使用前,必须根据需要对其编程。如果没有启用MPU,则等同于系统中没有配MPU。 MPU有如下的能力可以提高系统的可靠性:

- 阻止用户应用程序破坏操作系统使用的数据。

- 阻止一个任务访问其它任务的数据区,从而把任务隔开。

- 可以把关键数据区设置为只读,从根本上消除了被破坏的可能。

- 检测意外的存储访问,如,堆栈溢出,数组越界。

- 此外,还可以通过MPU设置存储器regions的其它访问属性,比如,是否缓区,是否缓冲等。

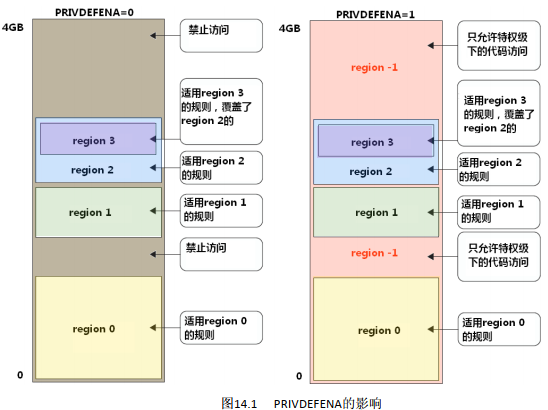

MPU在执行其功能时,是以所谓的“region”为单位的。一个region其实就是一段连续的地址,只是它们的位置和范围都要满足一些限制(对齐方式,最小容量等)。 CM3的MPU共支持8个regions,个数有限。允许启用一个“背景region”(即没有MPU时的全部地址空间),不过它是只能由特权级享用。在启用MPU后,就不得再访问定义之外的地址区间,也不得访问未经授权的region。否则,将以“访问违例”处理,触发MemManage fault。MPU定义的regions可以相互交迭。如果某块内存落在多个region中,则访问属性和权限将由编号最大的region来决定。比如,若1号region与4号region交迭,则交迭的部分受4号region控制。背景region与其他region重合的部分,就要受各region的限制。

浙公网安备 33010602011771号

浙公网安备 33010602011771号