在FPGA当中有几个速率名词很常用。ADC的速率算是一个,数据时钟速率是一个,符号率是一个。本文做一个区分

ADC速率:ADC的采样率一般是一个固定值,比如说一个非常垃圾的ADC采样率是512ksps,也就是512k samples/s,每秒钟采512k个样本。常见的是IQ正交采样器,也就是ADC会对IQ两路的模拟信号进行同时采样,当然这里需要两个ADC,那么这个速率应该就是说每个ADC的速率都是每秒采512k个样本。对于一个12bits的ADC,那么一次采样的输出就应该是12bits的I和12bits的Q。

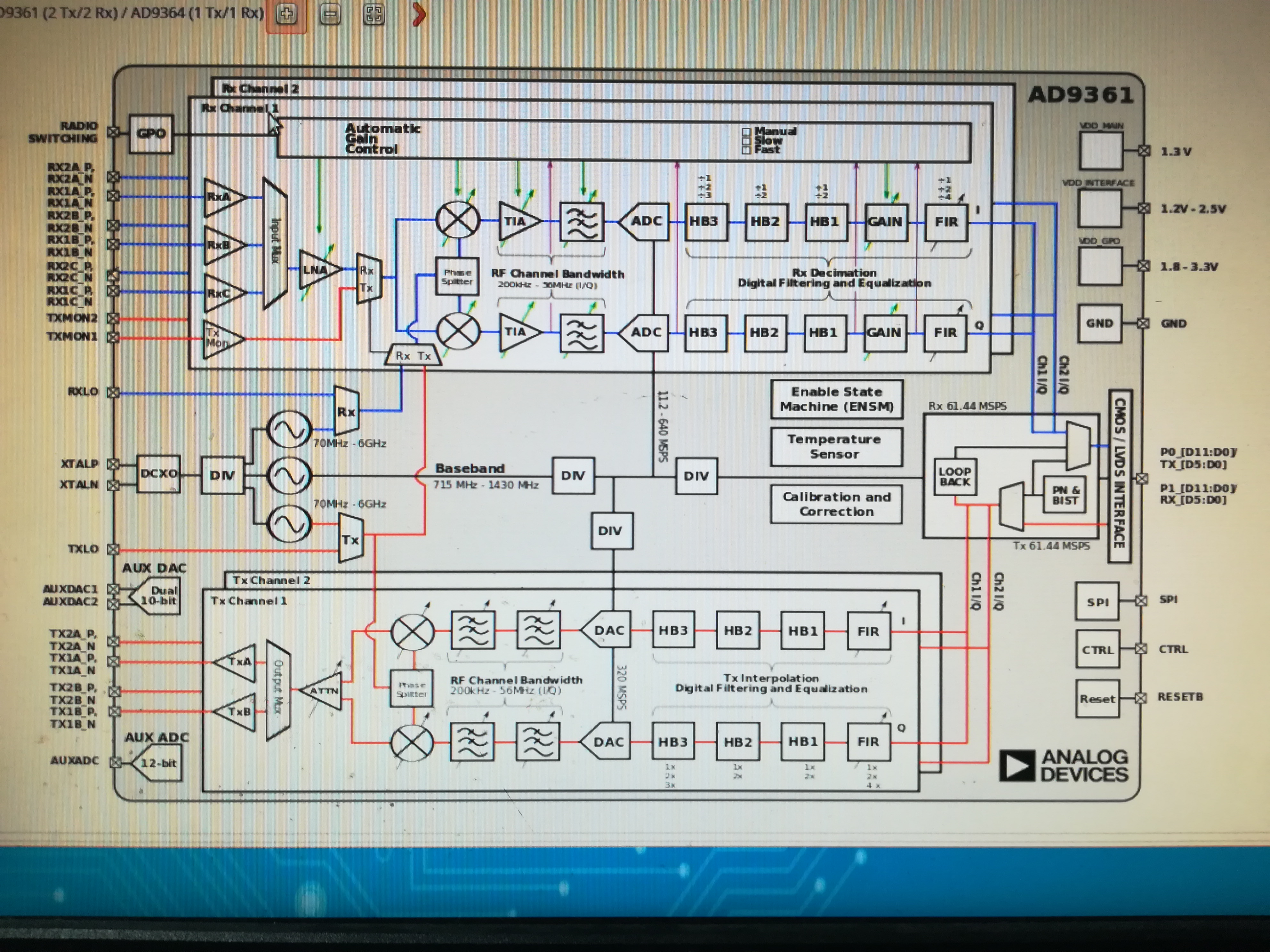

符号率:接上,如果是单通道,只有一路I和一路对应的Q,那么这里的符号率应该是1024k*16b/s。如果是AD9361的双通道芯片,而且同时工作的情况下,在后面样本不出现拥塞的速率就应该是2048k*16b/s。

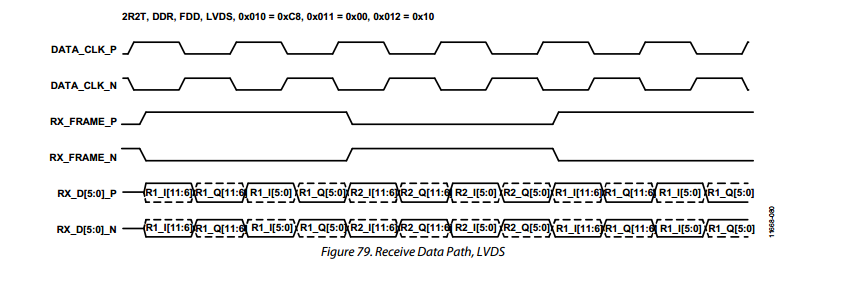

数据驱动时钟速率:可能与具体的系统构成有关。还以AD9361举例的话是这样,在4个通道全部工作的情况,2r2t,ddr,fdd,lvds的模式下,要以12bits的数据线传输给FPGA的话数据驱动时钟就应该至少是4倍的采样率(双通道*IQ两路(lvds会拆分12bits的数据位,但是ddr又相当于把这种拆开的影响消除了,参见最后那个图吧,不行就看看ug570接口那一章。))。

上图可见于ug570,page110。