在Vivado中使用AXI DMA

参考链接:http://www.fpgadeveloper.com/2014/08/using-the-axi-dma-in-vivado.html

http://www.fpgadeveloper.com/2017/10/using-axi-dma-in-vivado-reloaded.html

什么是DMA?

DMA代表直接内存访问,而DMA引擎使您可以将数据从系统的一部分传输到另一部分。DMA的最简单用法是将数据从内存的一部分传输到另一部分,但是DMA引擎可用于将数据从任何数据生成器(例如ADC)传输到内存,或从内存传输到任何内存数据使用者(例如DAC)。

教程概述

在此设计中,我们将使用DMA将数据从内存传输到IP块,然后再传输回内存。原则上,IP块可以是任何类型的数据生产者/消费者,例如ADC / DAC FMC,但是在本教程中,我们将使用简单的FIFO创建环回。之后,您将可以中断循环并插入您喜欢的任何自定义IP。

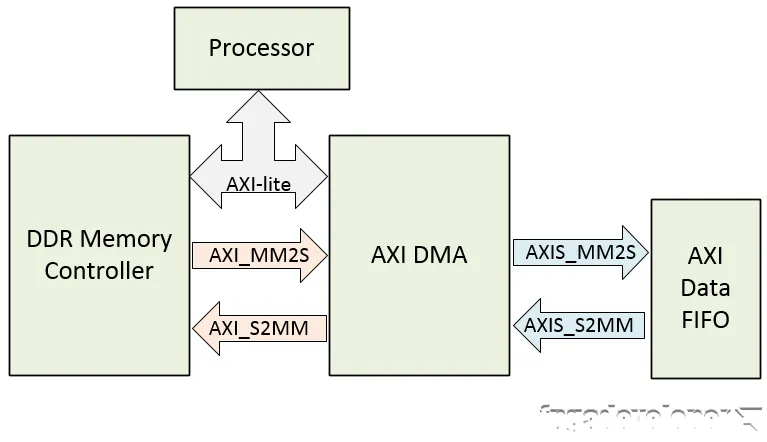

上面的框图说明了我们将创建的设计。处理器和DDR内存控制器包含在Zynq PS中。AXI DMA和AXI数据FIFO在Zynq PL中实现。AXI-lite总线允许处理器与AXI DMA通信以建立,启动和监视数据传输。AXI_MM2S和AXI_S2MM是存储器映射的AXI4总线,并提供对DDR存储器的DMA访问。AXIS_MM2S和AXIS_S2MM是AXI4流总线,它提供和接收连续的数据流,而没有地址。

- MM2S代表 (memory-mapped to stream),而S2MM代表 (stream to memory-mapped) 。

- 使用Scatter-Gather时,在DMA和内存控制器之间有一条额外的AXI总线。为了简单起见,将其保留在图中。

浙公网安备 33010602011771号

浙公网安备 33010602011771号