FPGA小白学习之路(5)clk为什么要用posedge,而不用negedge(转)

clk为什么要用posedge,而不用negedge

转自:http://www.cnblogs.com/dangxia/archive/2012/03/07/2383744.html

Verilog中典型的counter逻辑是这样的:

1 always@(posedge clk or negedge reset) begin 2 3 if(reset == 1'b0) 4 5 reg_inst1 <= 8'd0; 6 7 else if(clk == 1'b1) 8 9 reg_inst1 <= reg_inst1 + 1'd1; 10 11 else 12 13 reg_inst1 <= reg_inst1; 14 15 end

clk为什么要用posedge,而不用negedge呢?请教丹内先生,答案如下:

- 一般情况下,系统中统一用posedge,避免用negedge,降低设计的复杂度,可以减少出错。

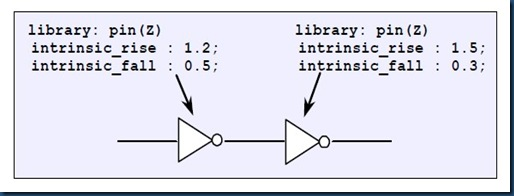

- 在ModelSim仿真中,时钟是很严格的,但是在真实的晶振所产生的clock却是不严格的,比如高电平和低电平的时间跨度不一样,甚至非周期性的微小波动。如果只使用posedge,则整个系统的节拍都按照clock上升沿对齐,如果用到了negedge,则系统的节拍没有统一到一个点上。上升沿到上升沿肯定是一个时钟周期,但是上升沿到下降沿却很可能不是半个周期。这都会出现问题。

![]()

- FPGA特有的东西:Global CLK。FPGA内部有专门的CLK“线”,和一般的逻辑门的走法不一样,目的是为了保证整个FPGA片内的时钟一致,这个东西就叫Global CLK

今天找这方面的资料,但发现信息很少,感觉本文说的蛮有道理,所以转载了和大家分享。希望对这个问题有不同理解的,可以交流交流。

真正不羁的灵魂不会真的去计较什么,因为他们的内心深处有着国王般的骄傲。

浙公网安备 33010602011771号

浙公网安备 33010602011771号