41. FSMC

一、FSMC简介

FSMC(Fleible static memory controller),即灵活的静态存储控制器,能够与同步或异步存储器和 16 位 PC 存储器卡连接,FSMC 接口可以通过地址信号,快速地找到存储器对应存储块上的数据。STM32F407 的 FSMC接口支持包括 SRAM、NAND FLASH、NOR FLASH 和 PSRAM 等存储器。F4 系列的大容量型号,且引脚数目在 100 脚及以上的 STM32F407 芯片都带有 FSMC 接口。

FSMC 把 AHB 总线上的数据转换为对应外设的通信协议,控制外设的访问时序,以至于我们可以直接在程序中寻址访问。配置好 FSMC 后,会定义一个指向这些地址的指针,通过对指针的操作就可以直接修改存储单元的内容,FSMC 自动完成读写命令和数据访问操作,不需要程序去实现时序。

FSMC 只能扩展静态的内存,不能是动态的内存,比如 SDRAM 就不能扩展。

二、FSMC框图

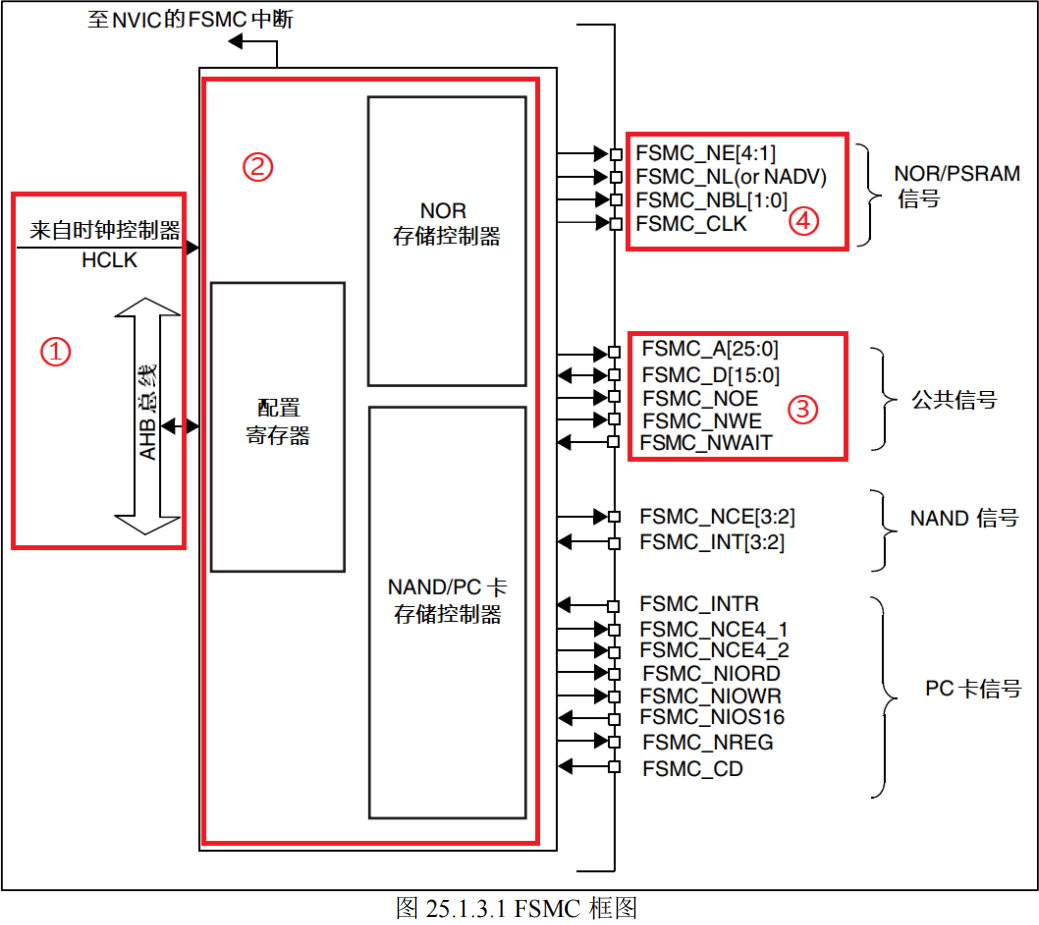

FSMC 接口的结构如图下所示:

FSMC 主要由 4 部分组成,AHB 总线接口(包括 FSMC 的配置寄存器)、NOR FLASH/SRAM 控制器、NAND FLASH/PC 卡控制器、外设接口 四个部分组成。

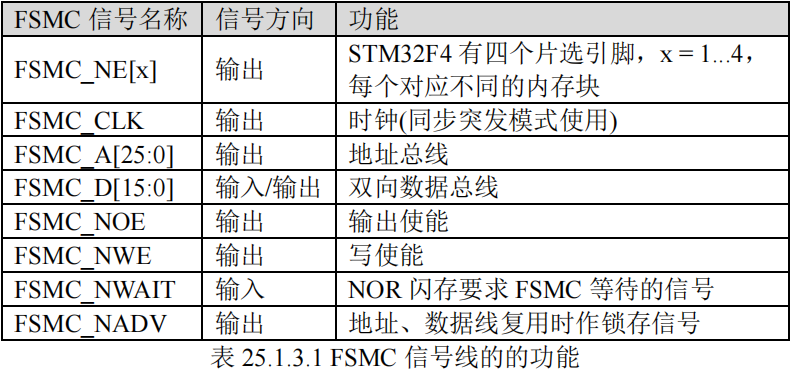

从图中我们可以看出,STM32 的 FSMC 可以驱动 NOR/PSRAM、NAND、PC 卡这 3 类设备,他们具有不同的 CS 以区分不同的设备。① 为 FSMC 的总线和时钟源,② 为 STM32 内部的 FSMC 控制单元,③ 是 连接硬件的引脚,这里的 “公共信号” 表示不论我们驱动前面提到的 3 种设备中的哪种,这些 IO 是共享的,所以如果需要用到多种功能的情况,程序上还要考虑分时复用。④ 是 NOR/PSRAM 会使用到的信号控制线,③ 和 ④这些信号比较重要,它们的功能如表下所示:

【1】、AHB 总线接口

AHB 总线接口时 CPU、DMA 等 AHB 总线主设备访问 FSMC 的通道,它负责把 AHB 总线事务转换成外设通信的协议。AHB 总线事务的请求可以是 8、16 或者 32 位的,但外设器件的数据线位宽是恒定的。如果两者宽度相同就不存在什么问题,如果总线事务的位宽大于外设的位宽,那么总线接口将把总线事务拆分为多个连续的 8 位或 16 位形式访问外设。我们应该尽量避免总线事务宽度小于外设宽度的情况出现,因为这将可能导致数据的不一致,具体与外设类型有关系。

配置寄存器则描述了扩展外设的具体形式、通信协议和接口方式,用于总线接口将 AHB 总线事务转换为外设通信协议,驱动 NOR FLASH/SRMA 控制器和 NARD FLASH/PC 卡控制器,从未控制外设。

【2】、NOR FLASH/SRAM 控制器

NOR FLASH/PSRAM 内存控制器支持各种同步和异步的内存。所谓同步内存就是在读写内存的时候需要一个同步时钟来指导数据数据的发送和接收。对于同步内存,FSMC 只会在读写操作的时候产生驱动时钟,并且其频率是系统总线时钟 HCLK 的分频。

NOR FLASH/PSRAM 控制器用于生成适当的时序,以驱动 8 位、16 位、32 位的异步 SRAM 和 ROM、异步或者突发模式的 PSRAM 和 NOR FLASH。我们通过配置寄存器描述外设的特征和时序后,控制器就可以为我们生成对应的驱动程序。

【3】、NAND FLASH/PC 卡控制器

NAND FLASH/PC 卡控制器驱动 8 位或者 16 位的 NAND FLASH 闪存以及 16 位的 PC 卡兼容设备。

【4】、外设接口

用于与要扩展外设联通用的。在接线时必须根据每个外设的特点,来进行合适的接线。

三、FSMC地址映射

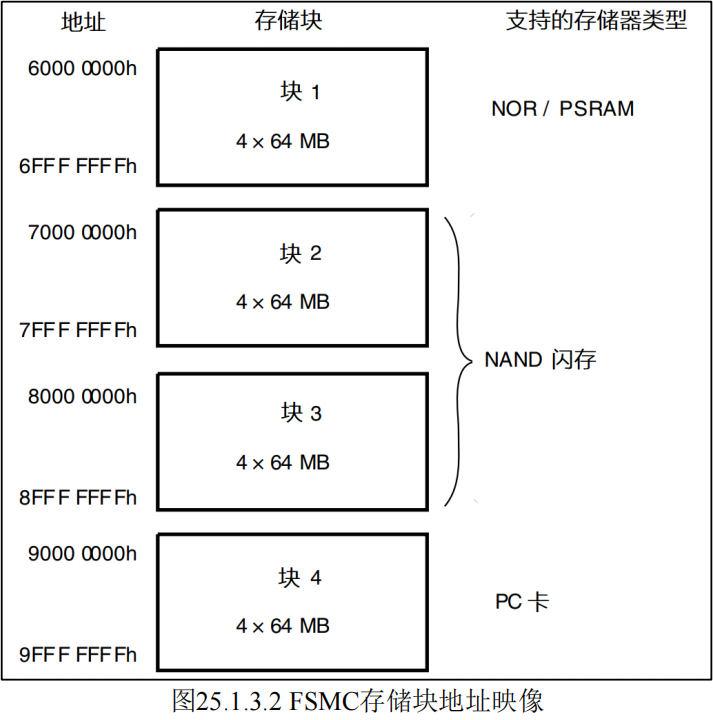

STM32F407 的 FSMC 将外部存储器划分为固定大小为 256M 字节的四个存储块,FSMC 的外部设备地址映像如图下所示:

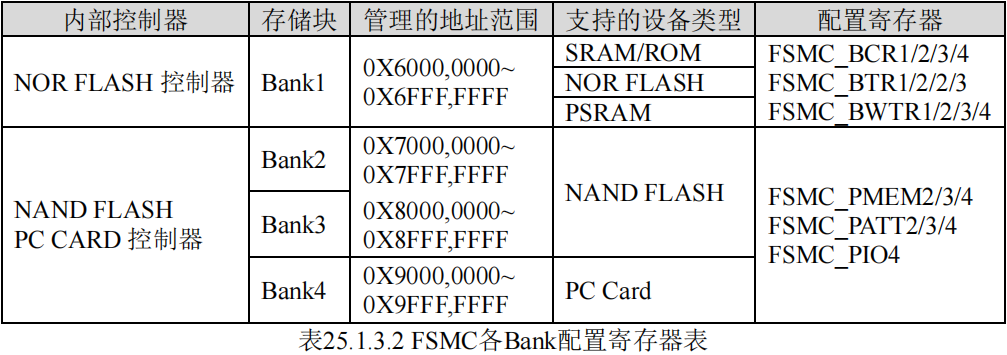

从上图可以看出,FSMC 总共管理 1GB 空间,拥有 4 个存储块(Bank),FSMC 各 Bank 配置寄存器如表下所示:

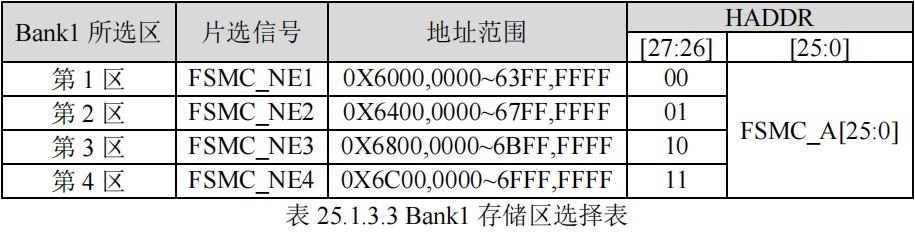

STM32F407 的 FSMC 存储块 1(Bank1)被分为 4 个区,每个区管理 64M 字节空间,每个区都有独立的寄存器对所连接的存储器进行配置。Bank1 的 256M 字节空间可以通过 28 根地址线(HADDR[27:0])寻址后访问。这里 HADDR 是内部 AHB 地址总线,其中 HADDR[25:0] 来自外部存储器地址 FSMC_A[25:0],而 HADDR[26:27]对 4 个区进行寻址。如表下所示:

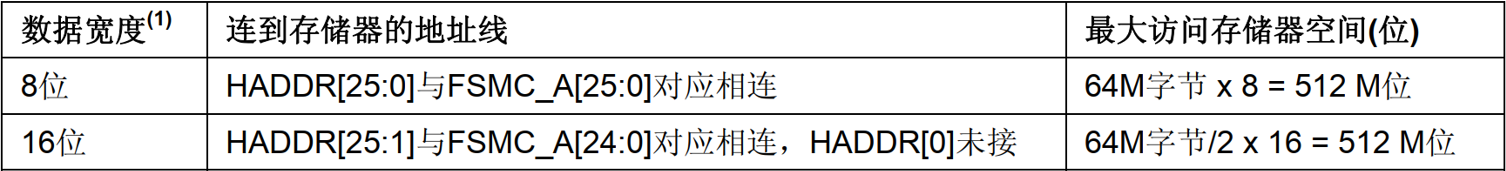

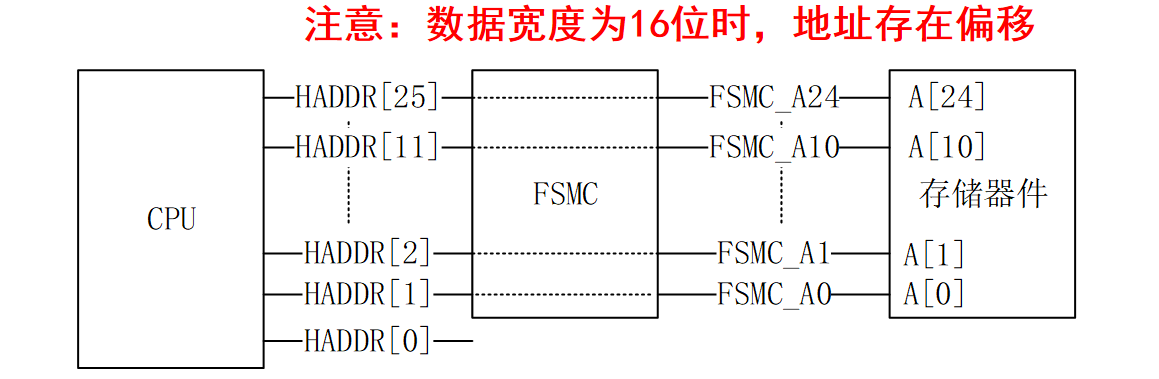

HADDR 总线是转换到外部存储器的内部 AHB 地址线。简单来说,从 CPU 通过 AHB 总线到外部信号线之间的关系。HADDR 是字节地址,而存储器访问不都是按字节访问,接到存储器的地址线与其数据宽度相关。

当 Bank1 接的是 16 位宽度存储器的时候:HADDR[25:1] → FSMC_A[24:0]。当 Bank1 接的是 8 位宽度存储器的时候:HADDR[25:0] → FSMC_A[25:0]。不论外部接 8 位/16 位宽设备,FSMC_A[0] 永远接在外部设备地址 A[0]。

当 FSMC 外设被配置成正常工作,并且外部接了 PSRAM,若向 0x60000000 地址写入数据,如 0xABCD,FSMC 会自动在各信号线上产生相应的电平信号,写入数据。FSMC 会控制片选信号 NE1 输出低电平,相应的 PSRAM 芯片被片选激活,然后使用地址线 A[25:0] 输出 0x60000000,在 NWE 写使能信号线上发出低电平的写使能信号,而要写入的数据信号 0xABCD 则从数据线 D[15:0] 输出,然后数据就被保存到 PSRAM 中了。

四、FSMC控制NOR FLASH或PSRAM的时序

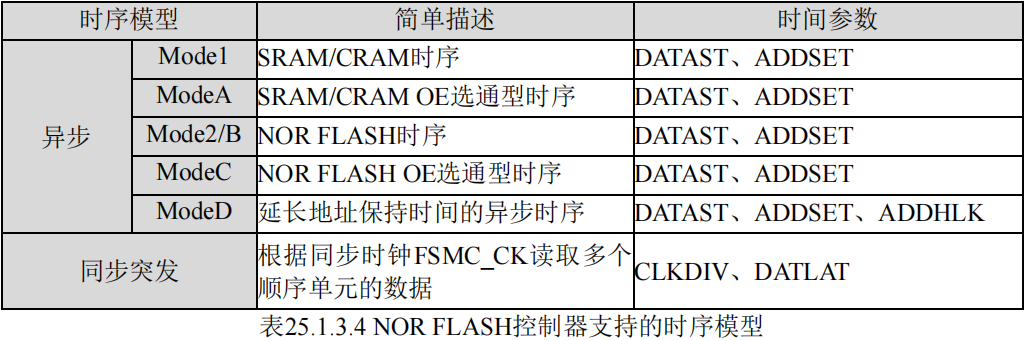

对于异步突发访问方式,FSMC 主要设置 3 个时间参数:地址建立时间(ADDSET)、数据建立时间(DATAST)和 地址保持时间(ADDHLD)。FSMC 综合了 SRAM/ROM、PSRAM 和 NOR FLASH 产品的信号特点,定义了 4 种不同的异步时序模型。

| 访问模式 | 对应的外部存储器 | 时序特点 |

|---|---|---|

| 模式 1 | SRAM/CRAM | OE 在读时序片选过程不翻转,由 NBL 信号,无 NADV 信号 |

| 模式 A | SRAM/PSRAM(CRAM) | OE 在读时序片选过程翻转,由 NBL 信号,无 NADV 信号 |

| 模式 B/2 | NOR FLASH | OE 在读时序片选过程不翻转,无 NBL 信号,有 NADV 信号 |

| 模式 C | NOR FLASH | OE 在读时序片选过程翻转,无 NBL 信号,有 NADV 信号 |

| 模式 D | 带地址扩展的异步操作 | OE 在读时序片选过程翻转,无 NBL 信号,有 NAL 信号,存在地址保存时间 |

所有信号信号由内部时钟 HCLK 保持同步,但该时钟不会输出到外部扩展的存储器。FSMC 始终在片选信号 NE 失效前对数据线采样,这样能保证符合存储器的数据保持时序。所有的控制器输出信号在内部时钟(HCLK)的上升沿变化,在同步写模式(PSRAM)下,读写的数据在存储器时钟(CLK)的下降沿变化。

下面以模式 A 为例:

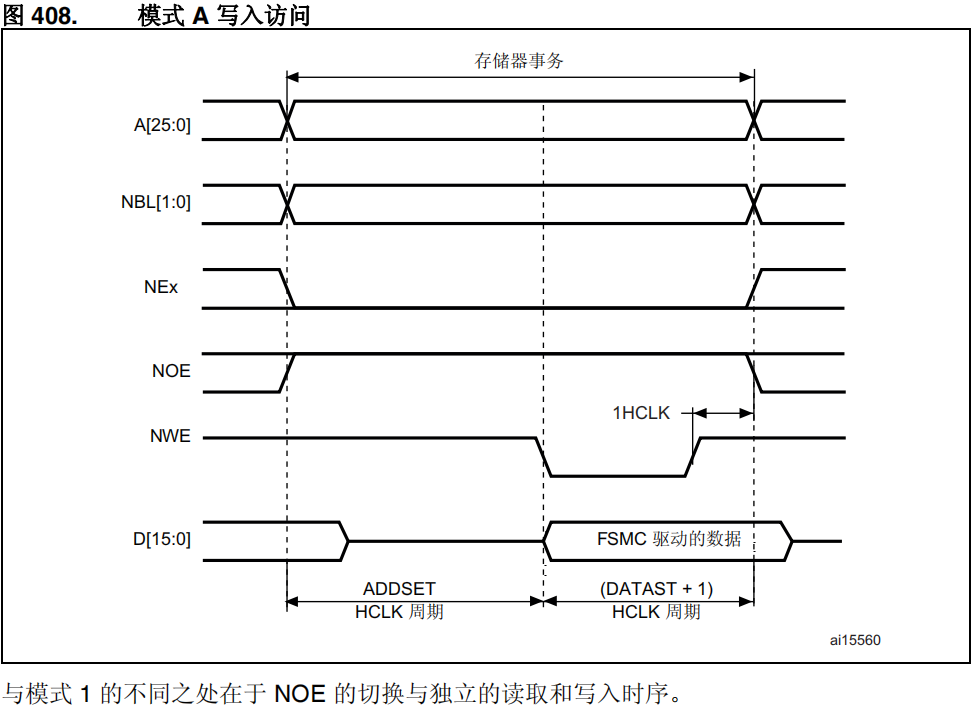

上图是 FSMC 模式 A 的写操作时序,该图表示一个存储器操作周期由 地址建立周期(ADDSET)、数据建立周期(DATAST)组成。在地址建立周期中,数据建立周期期间 NWE 信号拉低发出写信号,接着 FSMC 把数据通过数据线传输到存储器中。注意:NWE 拉高后的那 1 个 HCLK 是必要的,以保证数据线上的信号被准确采样。

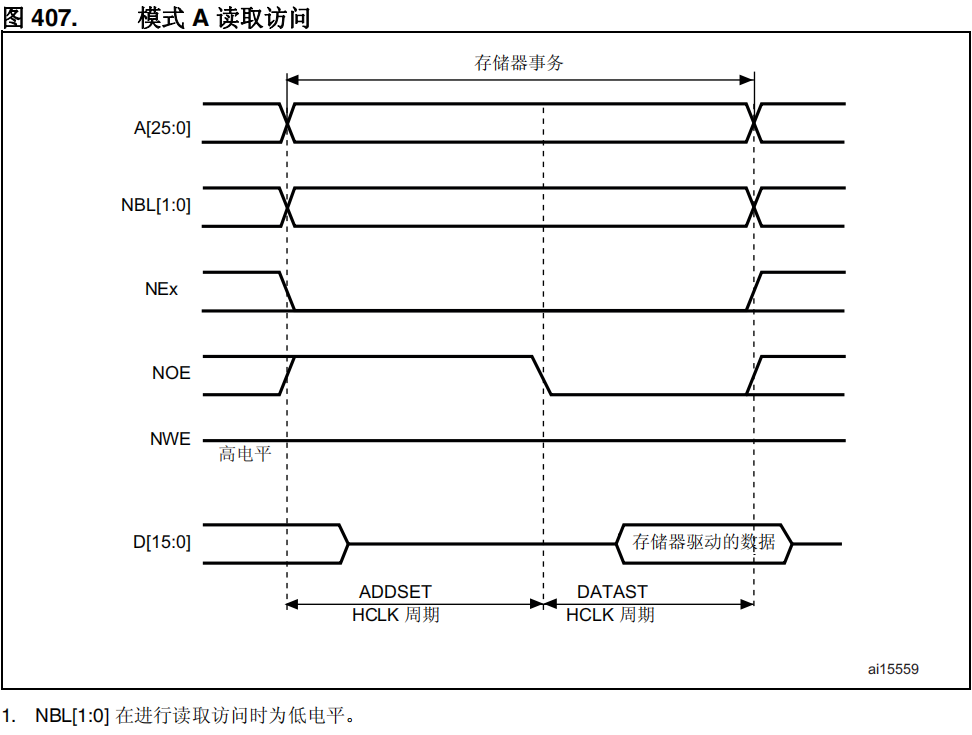

读操作模式时序类似,区别是它的一个存储器操作周期由 地址建立周期(ADDSET)和 数据建立周期(DATAST)以及 2 个 HCLK 周期 组成,且 在数据建立周期期间地址线发出要访问的地址,数据掩码信号线指示出要读取地址的高、低字节部分,片选信号使能存储器芯片;地址建立周期结束后读使能信号线发出读使能信号,接着存储器通过数据信号线把目标数据传输给FSMC,FSMC 把它交给内核。

五、FSMC常用寄存器

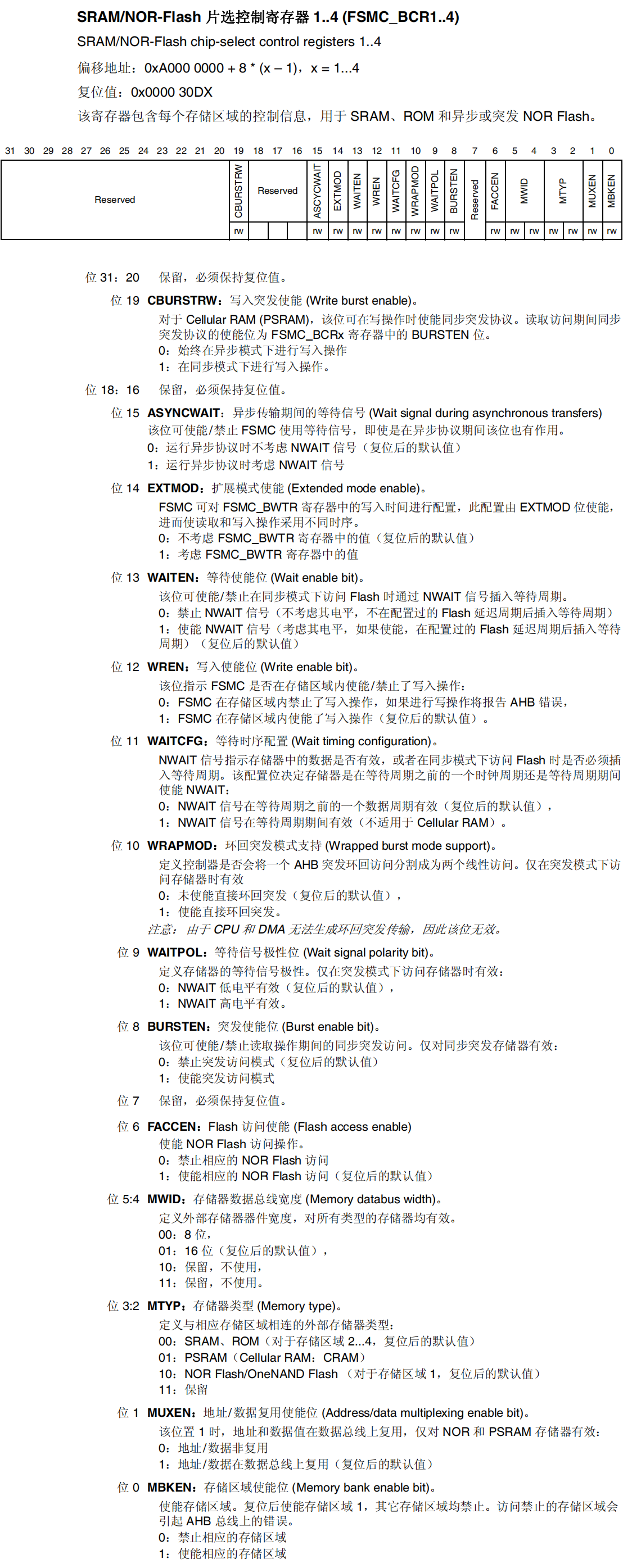

5.1、SRAM/NOR-Flash片选控制寄存器

位 14 EXTMOD 位:扩展模式使能位,也就是是否允许读写不同的时序。

位 12 WREN 位:写使能位。

位 WID[5:4]:存储器数据总线宽度。

位 MTYP[3:2]:存储器类型。

位 0 MBKEN 位:存储块使能位。

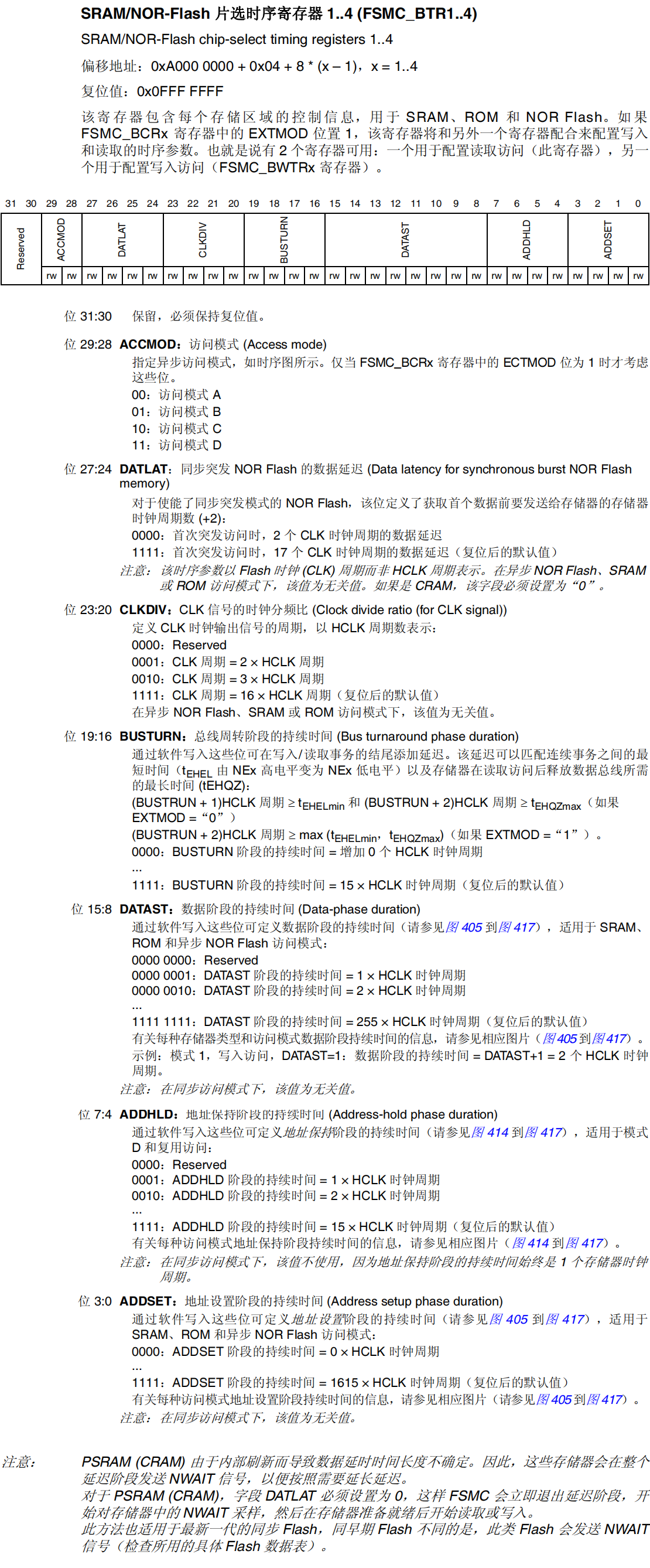

5.2、SRAM/NOR-Flash片选时序寄存器

这个寄存器包含了每个存储器块的控制信息,可以用于 SRAM、ROM 和 NOR FLASH 存储器。如果 FSMC_BCRx 寄存器中设置了 EXTMOD 位,则有两个时序寄存器分别对应读(本寄存器)和写操作(FSMC_BWTRx寄存器)。因为我们要求读写分开时序控制,所以 EXTMOD 是使能了的,也就是本寄存器是读操作时序寄存器,控制读操作的相关时序。

位 ACCMOD[29:28]:访问模式。

位 DATAST[15:8]:数据保持时间。0 为保留设置,其他设置则代表保持时间为:DATAST 个 HCLK 时钟周期,最大为 255 个 HCLK 周期。一个 HCLK 时钟周期为 6ns 左右(1/168Mhz)。

位 ADDSET[3:0]:地址建立时间。其建立时间为:ADDSET 个 HCLK 周期,最大为 15 个 HCLK 周期。

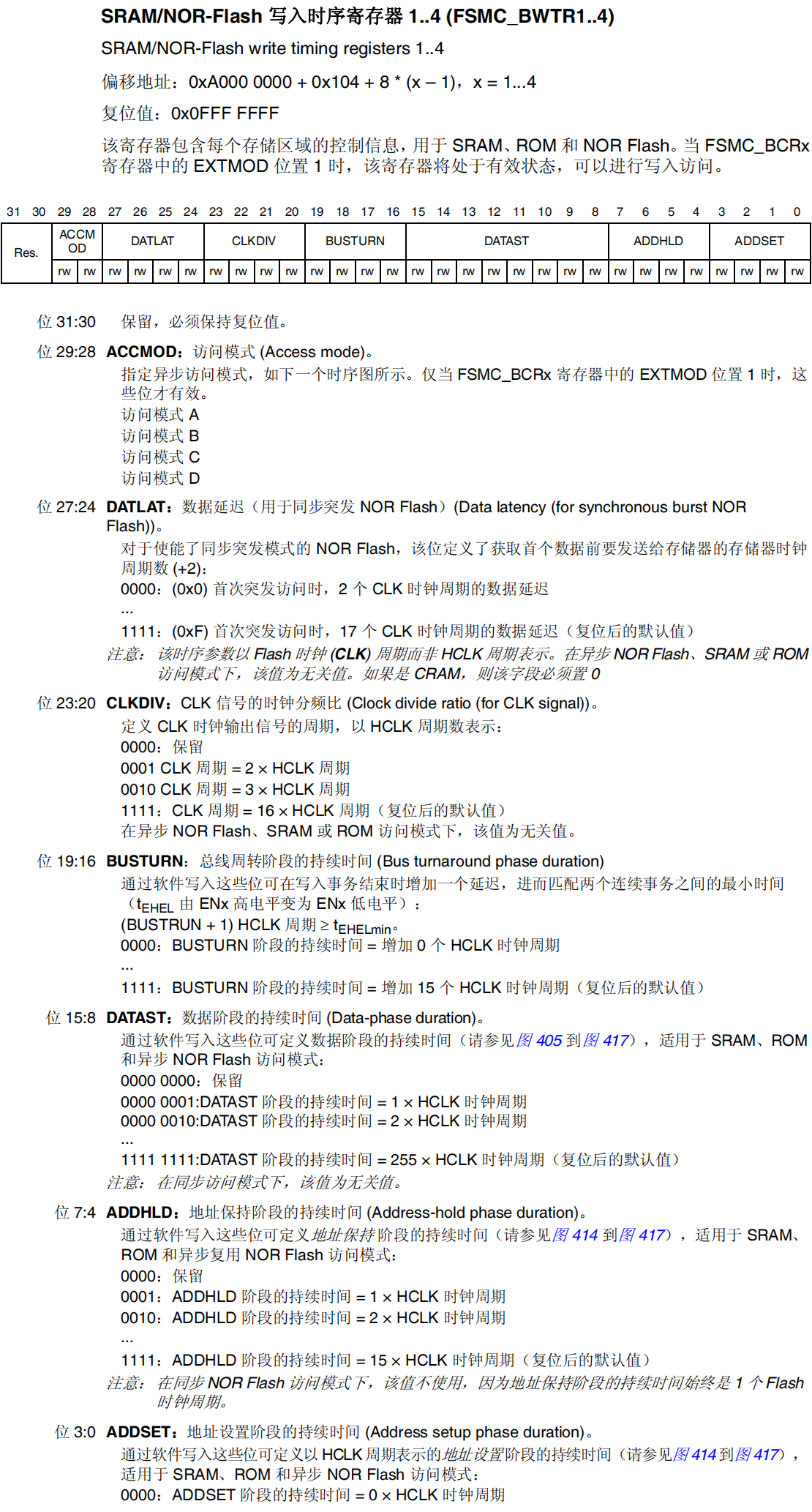

5.3、SRAM/NOR-Flash写入时序寄存器

该寄存器用作写操作时序控制寄存器,需要用到的设置同样是:ACCMOD、DATAST 和 ADDSET 这三个设置。这三个设置的方法同 FSMC_BTRx 一模一样,只是这里对应的是写操作的时序,ACCMOD 设置同 FSMC_BTRx 一模一样,同样是选择模式 A,另外 DATAST 和 ADDSET 则对应低电平和高电平持续时间。