CPU与高速缓存

CPU

CPU负责执行指令,是所有计算机硬件中速度最快的。一般用时钟周期(时钟频率)来衡量CPU的性能。

时钟周期

CPU时钟周期是操作的最小时间单位,值是主频的倒数,现代计算机的主频可以达到几GHZ。

指令周期是取出并执行一个指令的时间单位,一个指令需要多个CPU操作来执行,一般来说一个指令周期至少包含2个CPU时钟周期(取指+执行)。

同一个硬件架构下不同CPU的时钟周期越高,相同时间内能够执行的指令就越多,性能就越好;但在不同的硬件架构下只比较CPU主频大小意义不大,处理器结构不同,指令集就不同,相同意义的指令所需的CPU时钟周期也就不同。

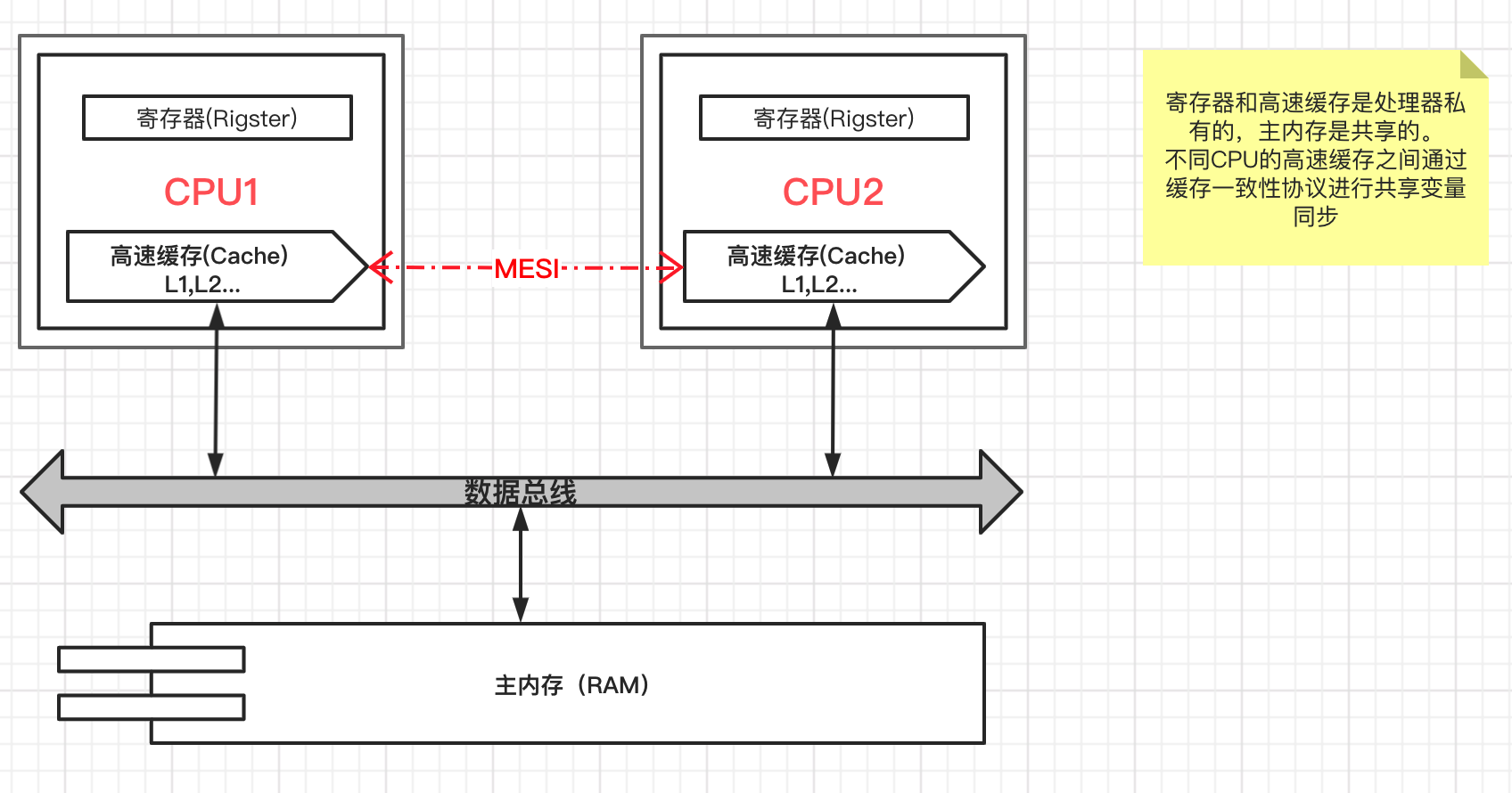

除了计算机架构不同外,在比较计算机整体性能的时候还需要考虑很多因素,例如前端总线("front side bus",FSB),内存的时钟周期,CPU通用寄存器的数据宽度和机器的一级、二级缓存等。

寄存器

寄存器是CPU的内部组成单元,是CPU运算时取指令和数据的地方,速度很快,可以理解为对于CPU来说读/写寄存器是不需要时间的,或者说如果只是操作寄存器(比如类似mov BX,AX之类的操作),那么一秒钟执行的指令个数理论上说就等于主频,因为寄存器是CPU的一部分。

寄存器可以用来暂存指令、数据和地址。在CPU中,通常有通用寄存器,如指令寄存器IR;特殊功能寄存器,如程序计数器PC、sp等。

高速缓存

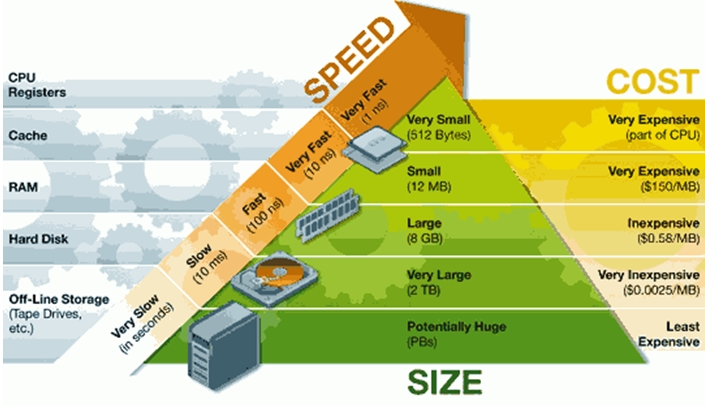

高速缓存(cache)通常分为L1,L2,L3三级,速度递减,容量递增,是为了弥补CPU与内存之间运算速度的差异而设置的硬件。

作用

Cache一词来源于1967年的一篇电子工程期刊论文。其作者将法语词“cache”赋予“safekeeping storage”的涵义,用于电脑工程领域。

当CPU处理数据时,它会先到Cache中去寻找,如果数据因之前的操作已经读取而被暂存其中,就不需要再从主内存中读取数据——由于CPU的运行速度一般比主内存的读取速度快,主存时钟周期(访问主存储器所需要的时间)为数个CPU时钟周期。因此若要访问主内存的话,就必须等待数个CPU周期从而造成浪费。L1缓存的速度可以在2-4个CPU时钟频率内完成,速度很快。

Linux下可以通过lscpu命令来查看CPU的信息,其中包括cache层次。

原理

提供“缓存”的目的是为了让数据访问的速度适应CPU的处理速度。

通常它不像系统主存那样使用DRAM技术,而使用昂贵但较快速的SRAM技术。其基于的原理是内存中“程序执行与数据访问的局域性行为”,即一定程序执行时间和空间内,被访问的代码集中于一部分。为了充分发挥缓存的作用,不仅依靠“暂存刚刚访问过的数据”,还要使用硬件实现的指令预测与数据预取技术——尽可能把将要使用的数据预先从内存中取到缓存里。

数据结构

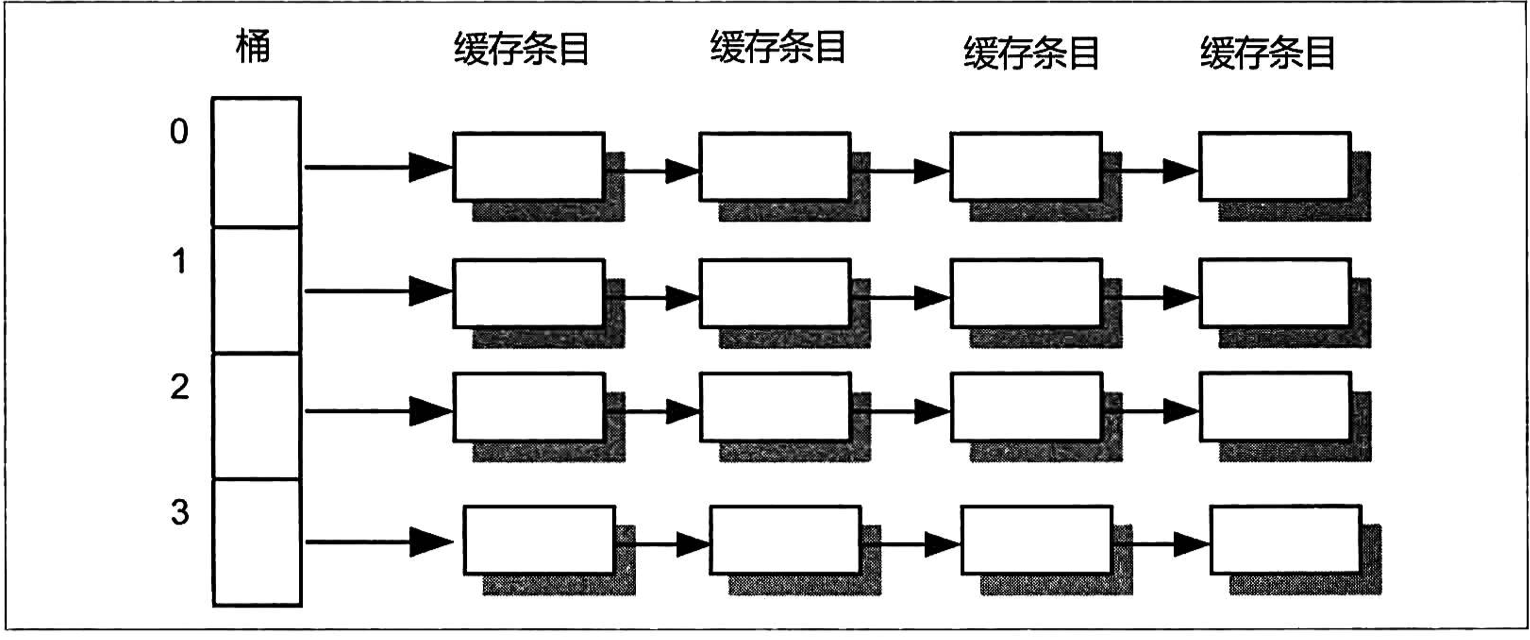

高速缓存的数据结构类似于拉链式的散列表,key是内存地址,值是内存数据的副本或即将写入内存的数据。

缓存条目中又包含三个属性:

其中tag可以理解为数据的内存地址,Data Block是内存数据,Flag用于标识数据状态。

历史

CPU的缓存曾经是用在超级计算机上的一种高级技术,不过现今个人电脑上使用的微处理器都将L1缓存集成在CPU芯片内部,用于存储数据缓存和指令缓存;而L2缓存曾经被放在CPU外部(主板或者CPU接口卡上),但是现在已经成为CPU内部的标准组件;更昂贵的CPU会配备比L2缓存还要大的L3缓存。

概念的扩展

如今缓存的概念已被扩充,不仅在CPU和主内存之间有Cache,而且在内存和硬盘之间也有Cache(磁盘缓存),乃至在硬盘与网络之间也有某种意义上的Cache──称为Internet临时文件夹或网络内容缓存等。凡是位于速度相差较大的两种硬件之间,用于协调两者数据传输速度差异的结构,均可称之为Cache。

计算机的存储体系金字塔

https://zh.wikipedia.org/wiki/%E6%97%B6%E9%92%9F%E9%A2%91%E7%8E%87

https://blog.csdn.net/hellojoy/article/details/54744231

《Java多线程编程实战指南-核心篇》

浙公网安备 33010602011771号

浙公网安备 33010602011771号