深入理解计算机系统(第4章 处理器体系结构)

目录

4.1 Y86-64指令集体系结构

指令集体系结构是汇编语言、机器语言的抽象。是程序员可见的计算机状态。是一种软件和硬件之间的接口规范。

4.2 逻辑设计和硬件控制语言HCL

数字逻辑与数字系统部分

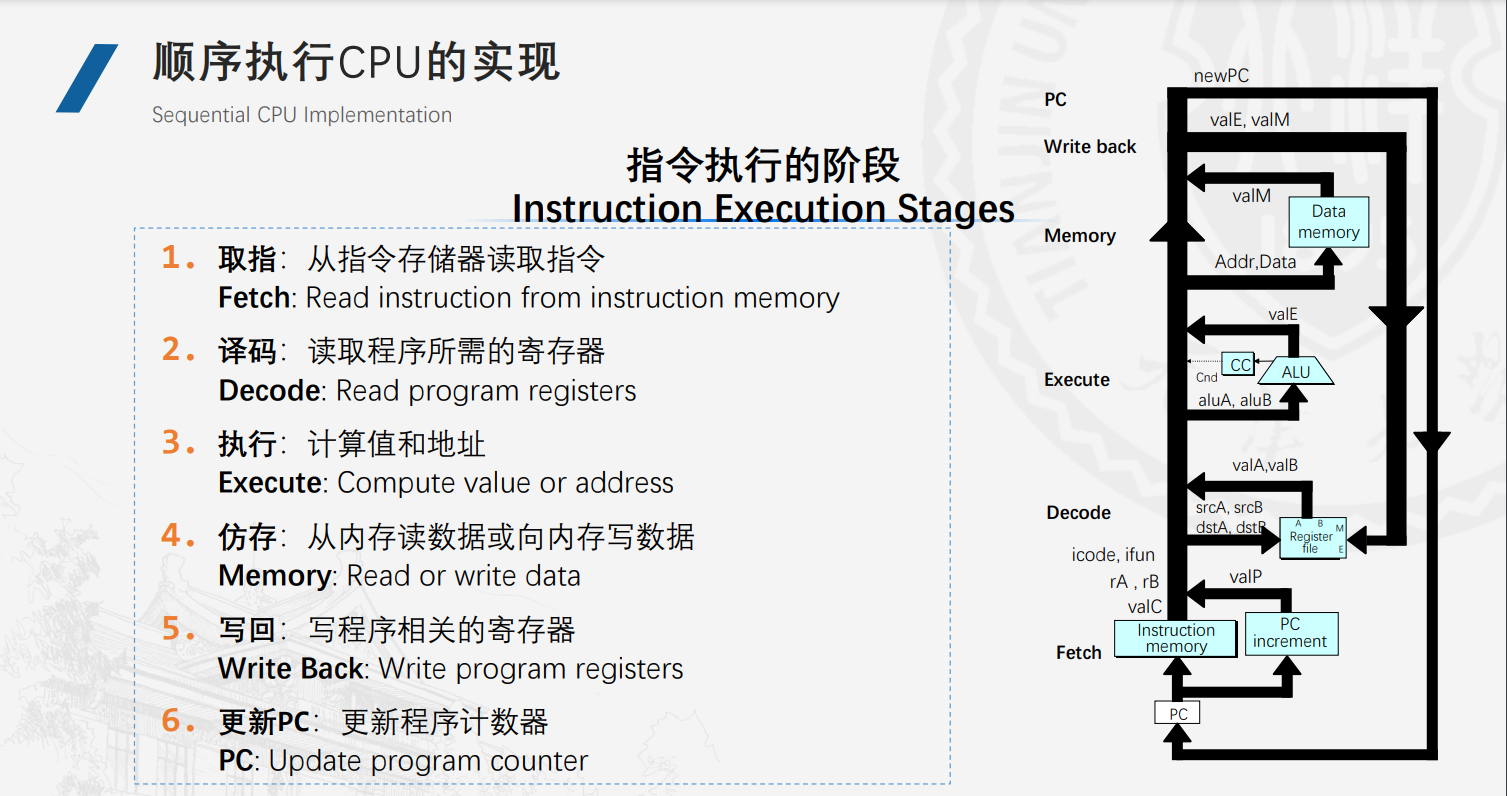

4.3 Y86-64的顺序实现

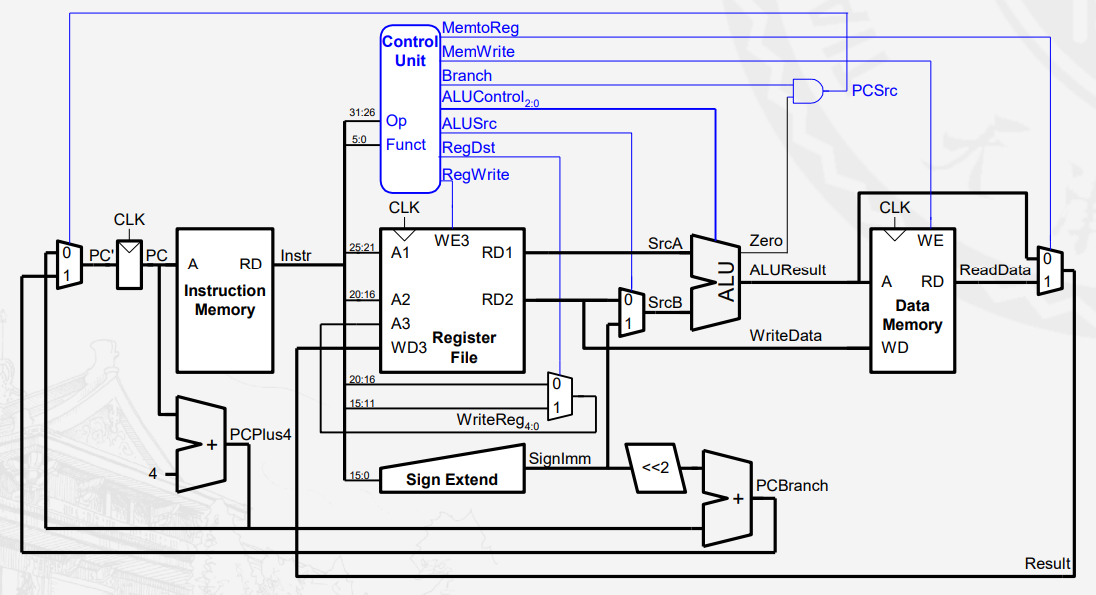

4.3.2 SEQ硬件结构

4.3.3 SEQ的时序

原则:从不回读。

4.3.4 SEQ阶段的实现

- 取指(Instruction Fetch, IF)

- 译码(Instruction Decode, ID)

- 执行(Execute, EXE)

- 访存(Memory, MEM)

- 写回(Write Back, WB)

- 更新PC

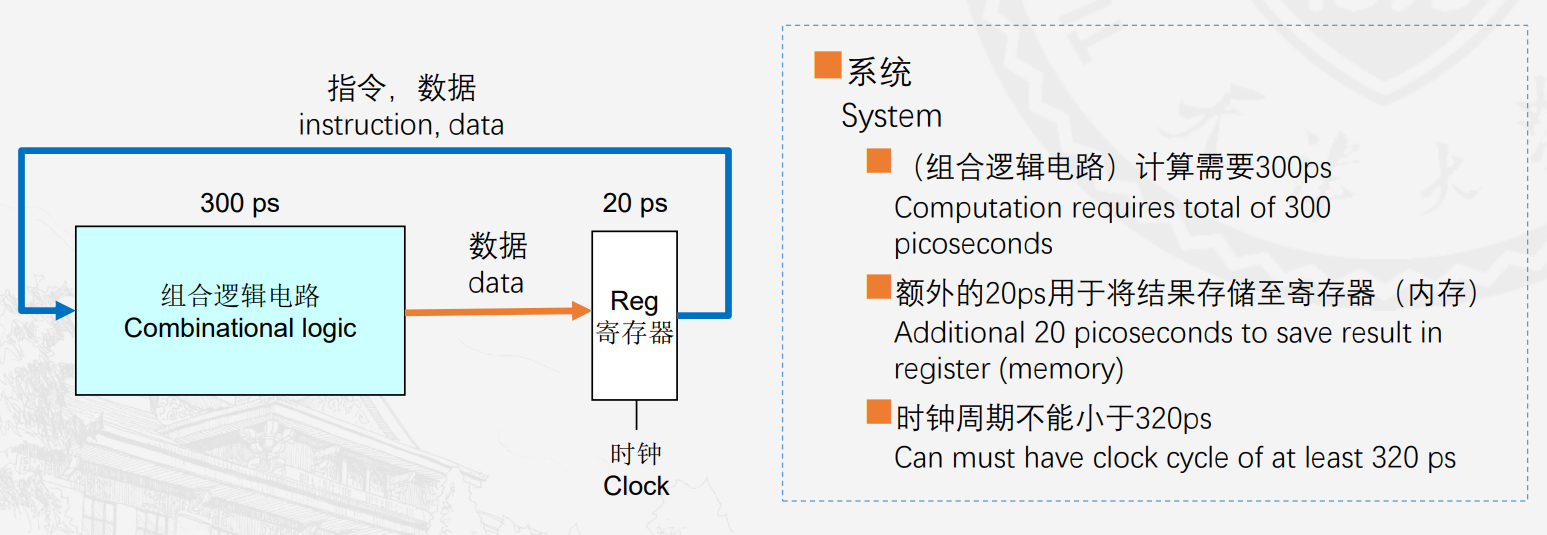

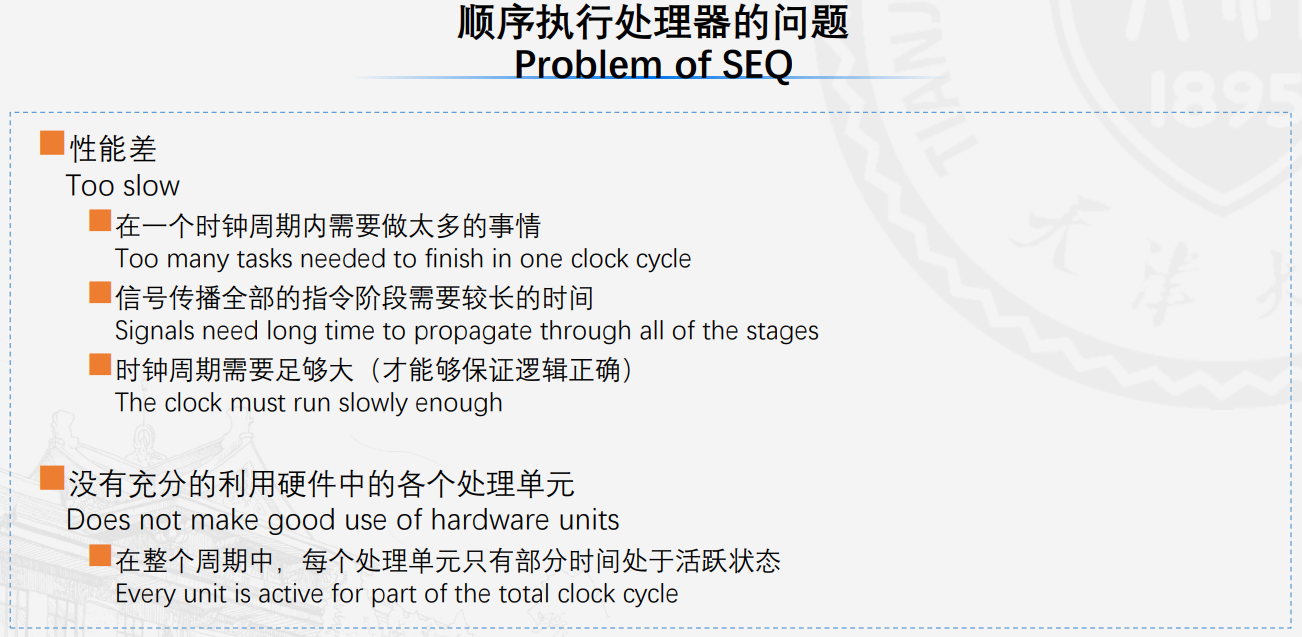

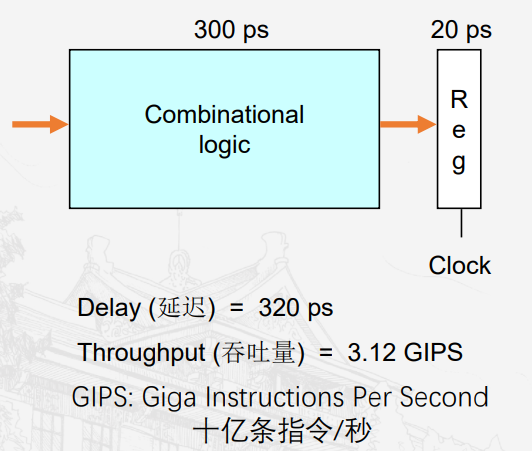

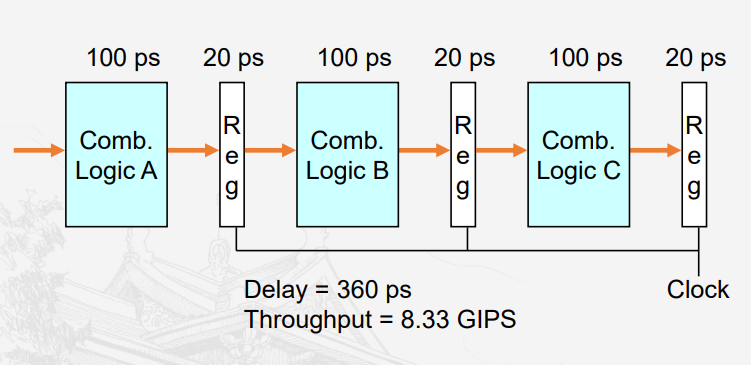

4.4 流水线的通用原理

流水线化的一个重要特性节省提高了系统的吞吐量(throughput),也就是单位时间执行的指令条数,但会轻微地增加延迟(latency),也就是从头到尾执行一条指令所需要的时间。

4.4.1 计算流水线

吞吐量 = \(\cfrac{1}{latency}\)

单位:每秒千兆条指令(GIPS)

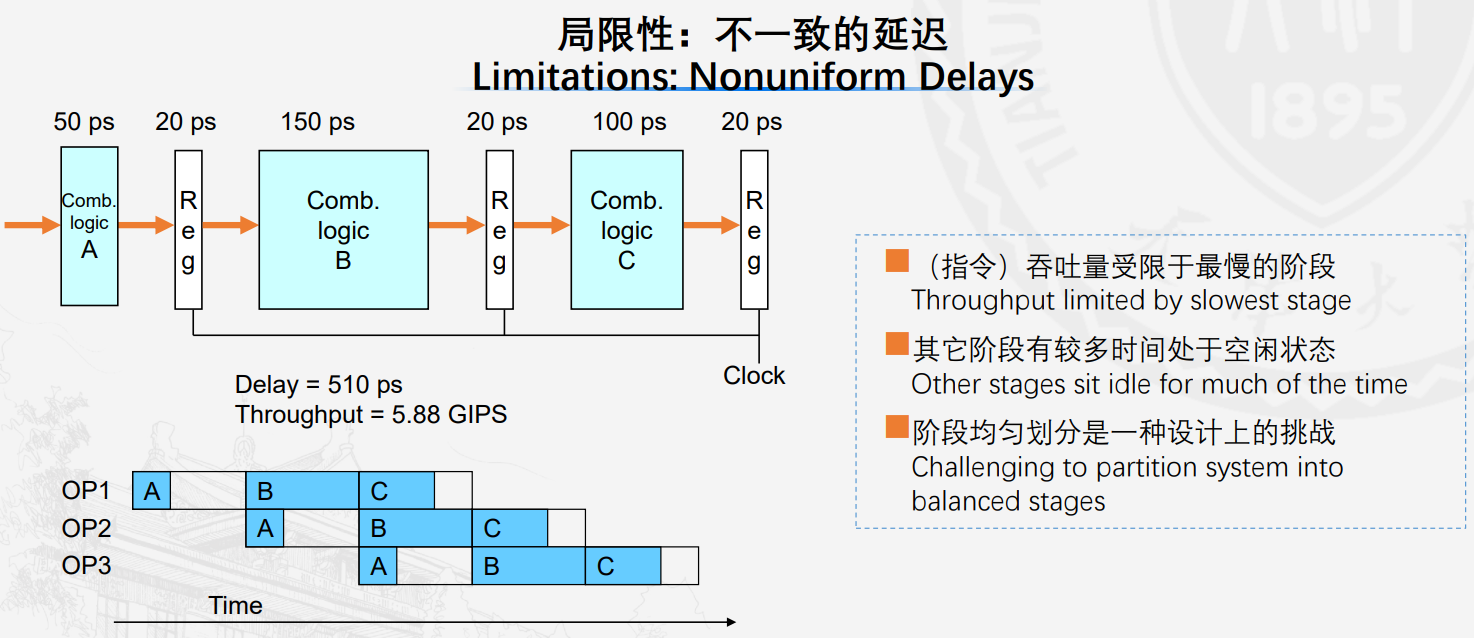

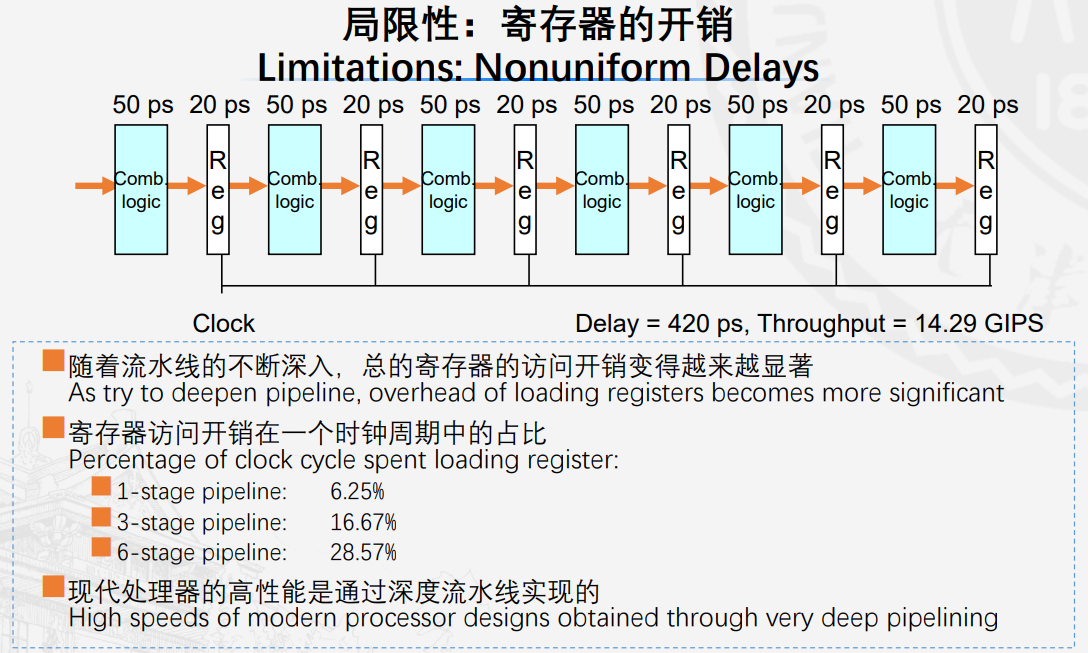

4.4.3 流水线的局限性

1. 不一致的划分

2. 流水线过深,收益反而下降

4.4.4 带反馈的流水线系统

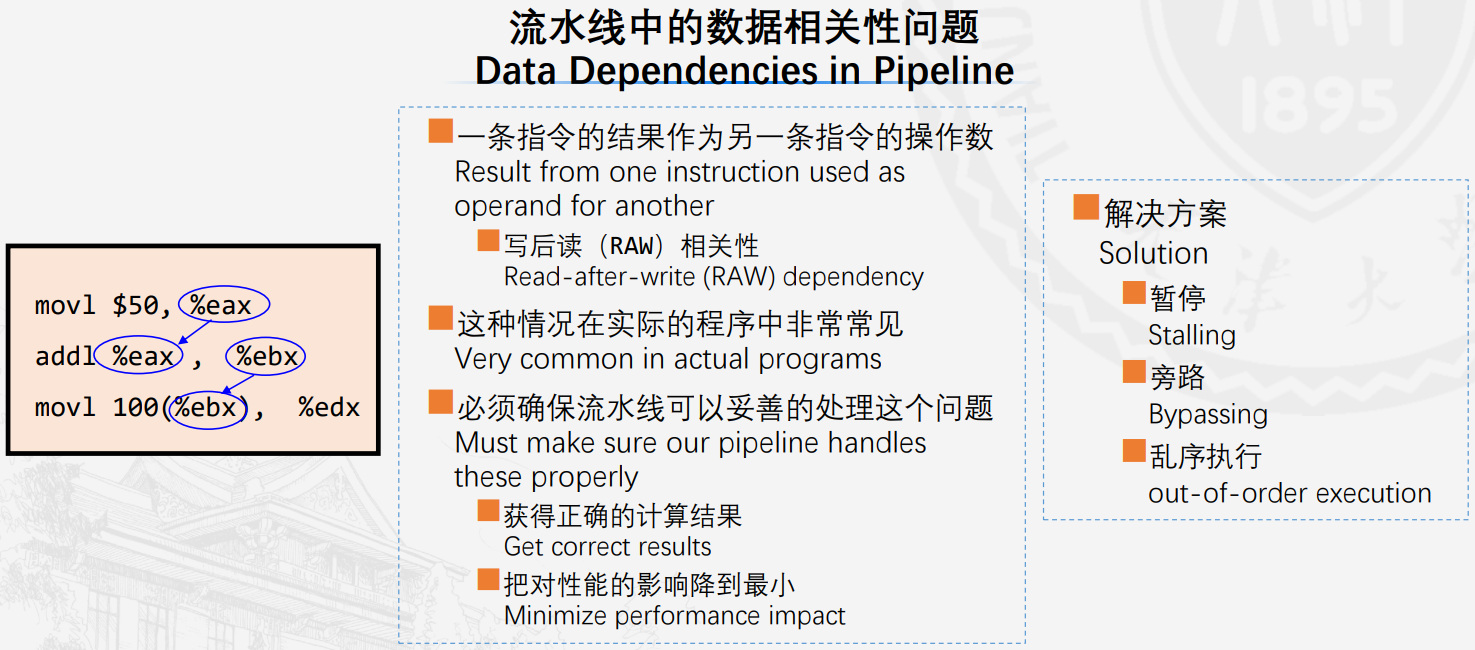

1. 数据相关

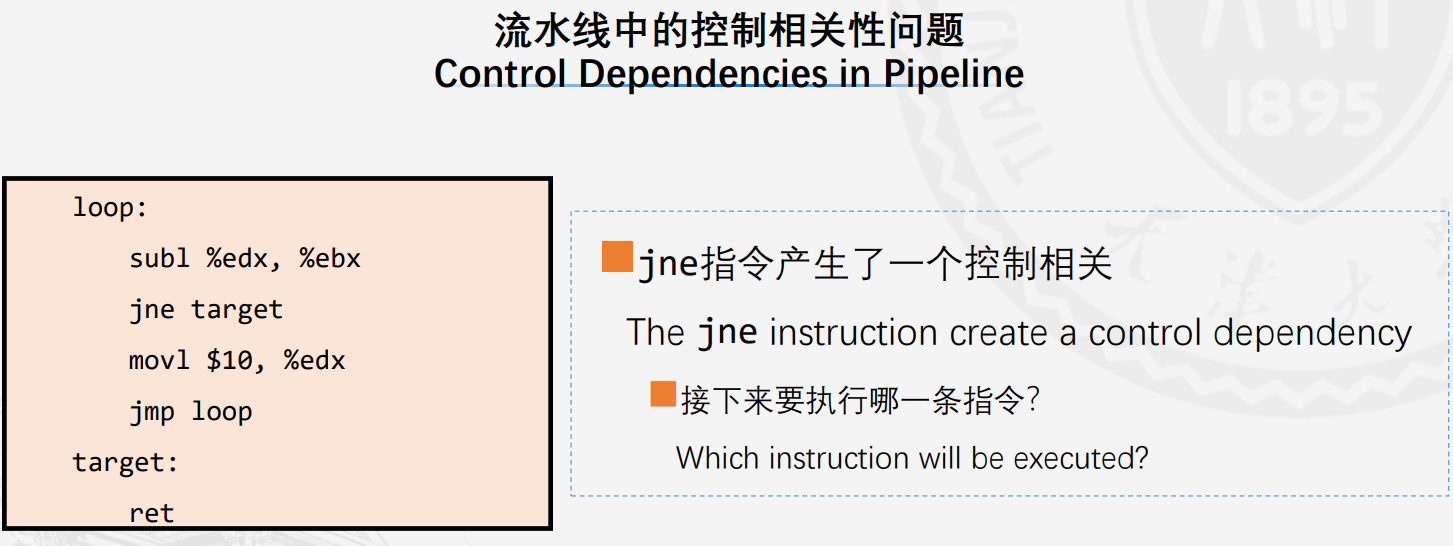

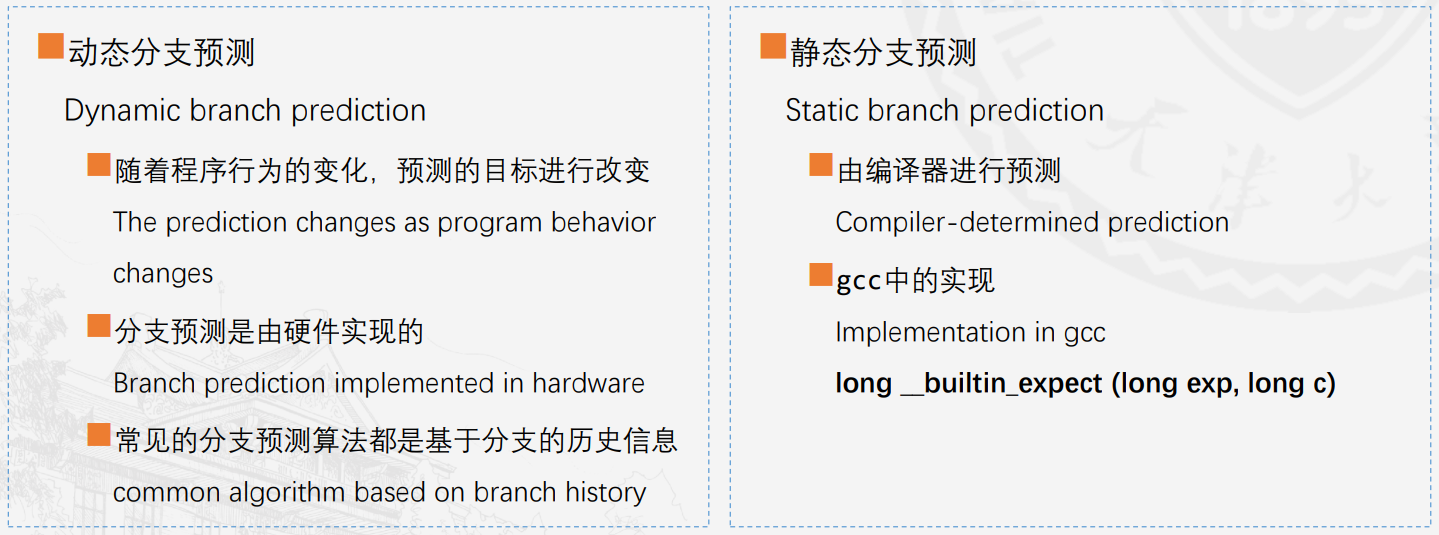

2. 控制相关

4.5 Y86-64的流水线实现

4.5.2 插入流水线寄存器

五阶段流水线:IF(包含更新PC)-ID-EXE-MEM-WB。

浙公网安备 33010602011771号

浙公网安备 33010602011771号