Vivado寄存器初始值问题

前言

本复位只针对Vivado中的寄存器复位。

什么时候需要复位?到底要不要复位?怎么复位?复位有什么卵用?

该复位的寄存器需要复位,复位使得寄存器恢复初始值,有的寄存器并不需要复位(数据流路径上)。

官方说法如下:具体可查看ug949。

流程

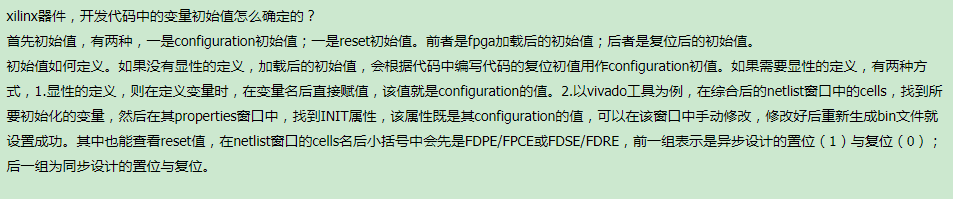

所以,问题来了,为了不使用复位信号该怎么赋初始值。

注意:reg语句中给寄存器赋初始值,在FPGA上电配置后值就为这个初始值。

如果只有复位语句中的初始值,那么上电配置(configuration )后和复位(reset)后寄存器都为此初始值。

如果reg语句给了初始值x1,且在复位语句中赋初始值x2,那么上电配置后初始值为x1,复位后寄存器初始值为x2。

代码验证:

1.如下代码,不复位也不赋初始值,vivado综合后寄存器初始值全为0。

(*DONT_TOUCH="yes"*)reg [5:0] r_cnt_1; always @(posedge i_clk) begin r_cnt_1 <= r_cnt_1 + 6'd1; end //always

2.如下代码,不复位赋初始值,vivado综合后寄存器初始值为代码中赋的初始值。

(*DONT_TOUCH="yes"*)reg [5:0] r_cnt_1 = 6'h34; always @(posedge i_clk) begin r_cnt_1 <= r_cnt_1 + 6'd1; end //always

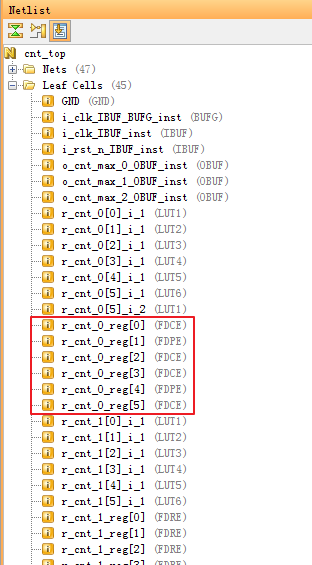

3.如下代码,使用复位但不给初始值,vivado综合后寄存器初始值为代码中复位语句中赋的初始值。(Xilinx不推荐异步复位)

(*DONT_TOUCH="yes"*)reg [5:0] r_cnt_0; always @(posedge i_clk,negedge i_rst_n) begin if (~i_rst_n) r_cnt_0 <= 6'h12; else r_cnt_0 <= r_cnt_0 + 6'd1; end //always

4.如下代码,既使用复位且给初始值,vivado综合后寄存器初始值为reg赋的初始值。

(*DONT_TOUCH="yes"*)reg [5:0] r_cnt_2 = 6'h01; always @(posedge i_clk,negedge i_rst_n) begin if (~i_rst_n) r_cnt_2 <= 6'h12; else r_cnt_2 <= r_cnt_2 + 6'd1; end //always

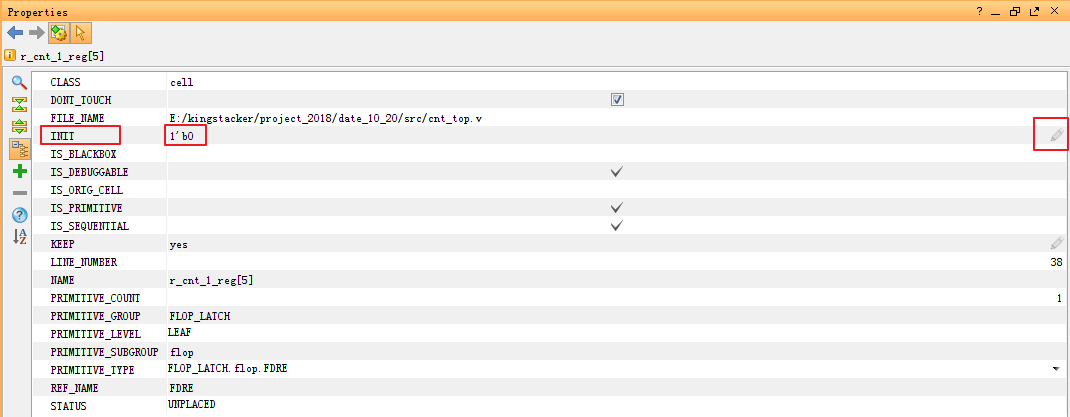

另一个问题,vivado综合寄存器初始值怎么查看?

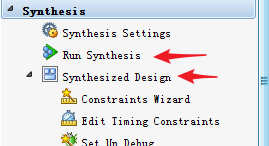

(1)打开综合后的工程。

(2)在网表中查看,不过只能单个点击查看。。。。

(3)在properties窗口中查看初始值如下,右侧可以更改初始值(没使用过。。)

以上。

浙公网安备 33010602011771号

浙公网安备 33010602011771号