FPGA功能仿真,门级仿真,后仿真的区别

前言

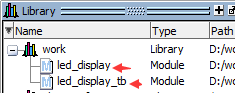

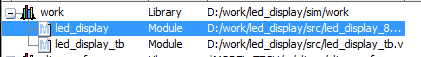

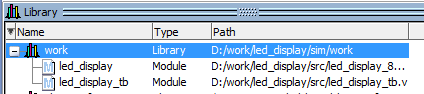

分清楚各种仿真间的关系,工具采用quartus prime16.0,仿真工具采用modelsim10 ae版;项目:led_display;

流程

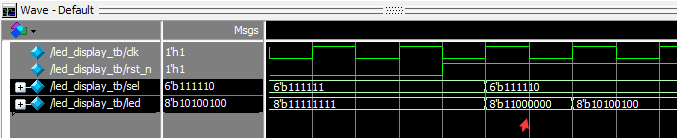

1.RTL行为级仿真:也叫功能仿真,这个阶段的仿真可以用来检查代码中的语法错误以及代码行为的正确性,其中不包括延时信息。如果没有实例化一些与器件相关的特殊底层元件的话,这个阶段的仿真也可以做到与器件无关。

需要的文件:编写的verilog源文件以及tb文件。如果用到了pll等ip核,需要挂载器件库文件。

1 #set the sim home dir ; 2 set sim_home D:/work/led_display/sim 3 #set the src code home dir; 4 set src_home D:/work/led_display/src 5 vlib ${sim_home}/work 6 vmap work ${sim_home}/work 7 vlog ${src_home}/*.v 8 vsim -novopt -t 1ns -L altera_ver -L altera_mf_ver -L cycloneive_ver -L sgate_ver -L lpm_ver work.led_display_tb 9 view wave 10 add wave * 11 run @600ns

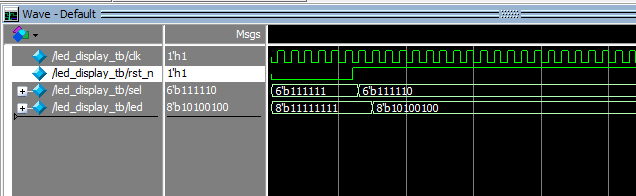

可以看到波形无延时;

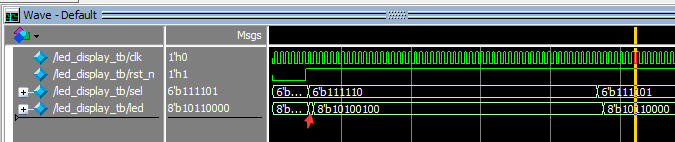

2.门级仿真:也叫综合后仿真,综合后生成的网表文件(.vo)加tb仿真;网表是与器件有关的,所以要挂载好相关器件库文件。

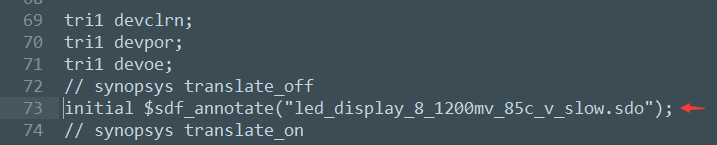

对于quartus生成的vo文件,首先要注释掉其中的挂载sdo文件语句,否则仿真是时序仿真,因为添加了sdo延时文件:

需要的文件:vo网表文件以及tb文件。需要挂载器件库文件。

1 #set the sim home dir ; 2 set sim_home D:/work/led_display/sim 3 #set the src code home dir; 4 set src_home D:/work/led_display/src 5 vlib ${sim_home}/work 6 vmap work ${sim_home}/work 7 vlog ${src_home}/led_display_8_1200mv_85c_slow.vo ${src_home}/led_display_tb.v 8 vsim -novopt -t 1ns -L altera_ver -L altera_mf_ver -L cycloneive_ver -L sgate_ver -L lpm_ver work.led_display_tb 9 view wave 10 add wave * 11 run @600ns

对于本栗子,可以看到门级仿真引入了中间态。

忽略不计。

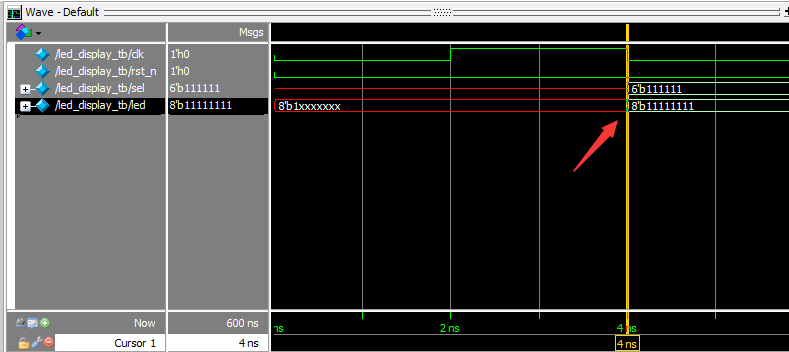

3.时序仿真:也叫后仿真。网表文件加延时,仿真中会包含延时信息。

需要的文件:vo网表文件以及tb文件以及延时文件sdo(采用脚本挂载)。需要挂载器件库文件。

1 #set the sim home dir ; 2 set sim_home D:/work/led_display/sim 3 #set the src code home dir; 4 set src_home D:/work/led_display/src 5 vlib ${sim_home}/work 6 vmap work ${sim_home}/work 7 vlog ${src_home}/led_display_8_1200mv_85c_slow.vo ${src_home}/led_display_tb.v 8 vsim -novopt -t ns -L altera_ver -L altera_mf_ver -L cycloneive_ver -L sgate_ver -L lpm_ver -sdftyp /led_display_tb/u=${src_home}/led_display_8_1200mv_85c_v_slow.sdo work.led_display_tb 9 view wave 10 add wave * 11 run @600ns

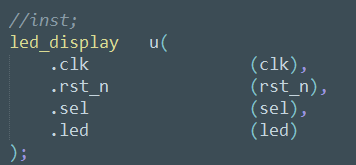

/led_display_tb/u 的意义:前面是tb名,后边是实例化led_display的名字。

如上图所示,可以看到器件延时大约4ns,包含了延时信息。

以上。

浙公网安备 33010602011771号

浙公网安备 33010602011771号