如何在SV中使用枚举enum语法

前言

enum可用于一系列常量的定义。典型是用于状态机的状态建模,使得code更为清晰。

流程

本次需要一个top层模块描述状态机和定义文件即可。

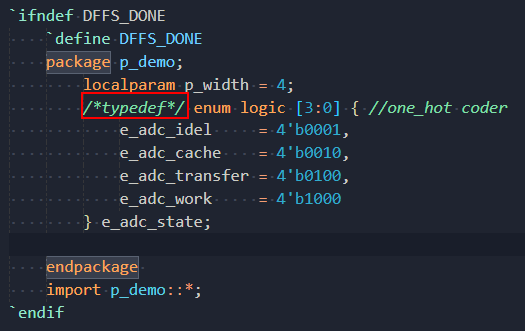

(1)definition.sv内容为:使用one_hot编码。

`ifndef DFFS_DONE

`define DFFS_DONE

package p_demo;

localparam p_width = 4;

typedef enum logic [3:0] { //one_hot coder

e_adc_idel = 4'b0001,

e_adc_cache = 4'b0010,

e_adc_transfer = 4'b0100,

e_adc_work = 4'b1000

} e_adc_state;

endpackage

import p_demo::*;

`endif

(2)demo_sv.sv内容为:随便写个状态机试试。

`include "definitions.sv"

module demo_sv (

input logic i_clk,

output logic o_b

);

e_adc_state es_state = e_adc_idel; //enum类型变量定义

logic [p_width-1:0] l_cnt = '0;

always_ff @(posedge i_clk)

begin

l_cnt <= l_cnt + 'd1;

end

always_ff @(posedge i_clk) //状态机跳转逻辑

begin

if (l_cnt == 'd0)

es_state <= e_adc_idel;

else

begin

case (es_state)

e_adc_idel: begin

if (l_cnt == 'd4)

es_state <= e_adc_cache;

end

e_adc_cache: begin

if (l_cnt == 'd15)

es_state <= e_adc_work;

end

e_adc_transfer: begin

if (l_cnt == 'd9)

es_state <= e_adc_cache;

end

e_adc_work: begin

if (l_cnt == 'd29)

es_state <= e_adc_transfer;

end

default: es_state <= e_adc_idel;

endcase

end

end

assign o_b = (es_state == e_adc_transfer) ? 1'b1 : 1'b0;

endmodule:demo_sv

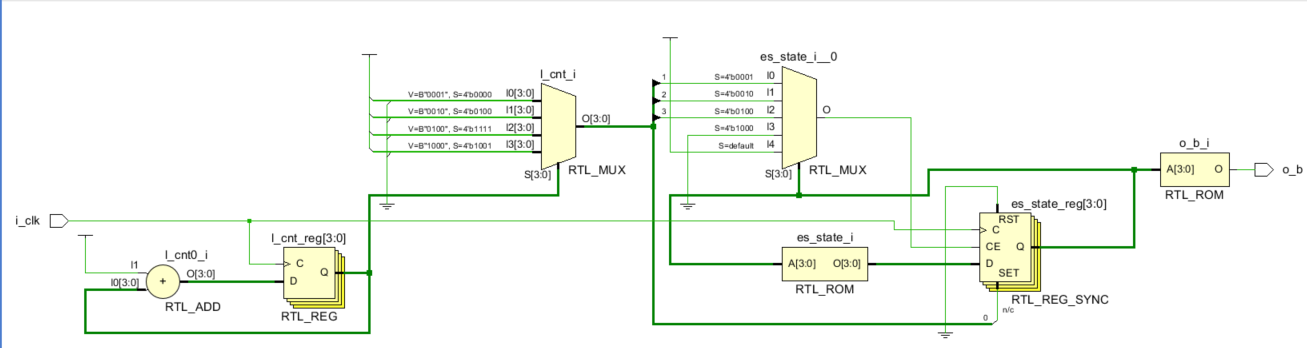

(3)使用vivado2018.3综合看看。

注意:匿名枚举是不可综合的。

以上。

浙公网安备 33010602011771号

浙公网安备 33010602011771号