ZYNQ7000 通过FPGA Manager加载比特流

https://blog.csdn.net/weixin_40604731/article/details/100690049

注意:以上参考限制了vivado的版本,应该为2018.1以上。

前言

实际项目中,往往存在PL端设计不断迭代的过程。

一种是可以不断生成新的fsbl合成BOOT.BIN文件,拷贝到SD卡,但涉及到每次需要生成BOOT.BIN插拔SD卡,比较难受。

有么有可以直接download到linux,通过linux的驱动层去更新PL端呢?

xilinx提供了FPGA manager(流程暂未验证)。

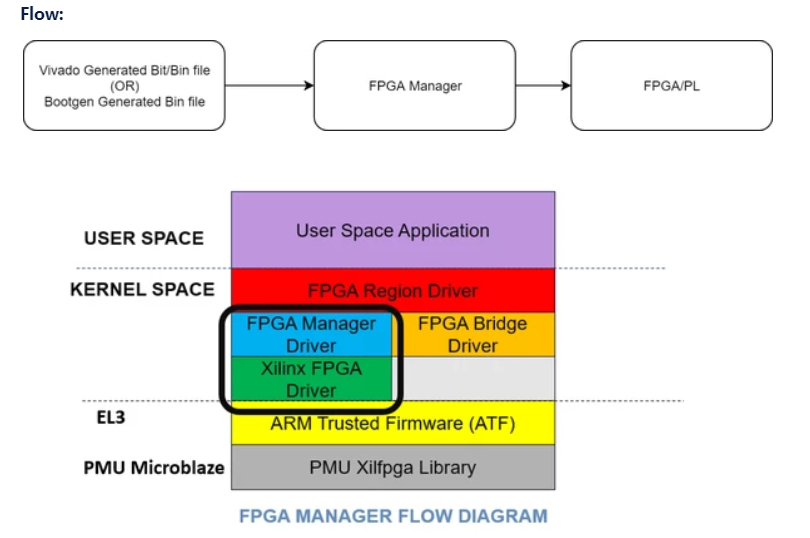

linux为啥可以更新PL,主要是有驱动管理:https://xilinx-wiki.atlassian.net/wiki/spaces/A/pages/18841847/Solution+ZynqMP+PL+Programming

流程

以下只是验证PL的更新,不包含设备树的DTO操作方法,详情见参考链接。

1.有一个正常启动的linux工程及硬件平台,不赘述。

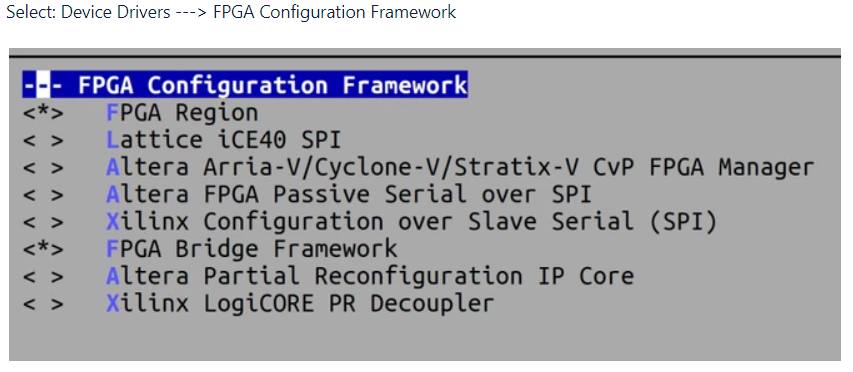

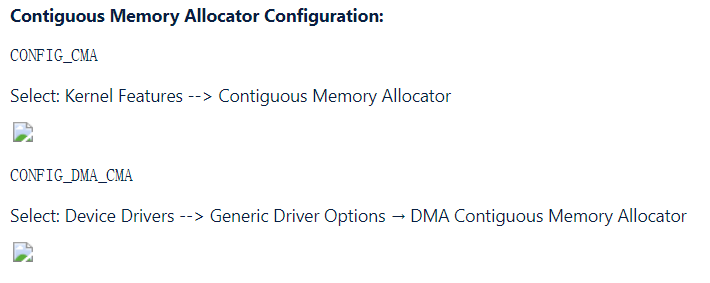

2.在内核配置中启用相关项:

(1)启用部件

(2)配置连续DMA

2.在device tree中添加:

devcfg: devcfg@f8007000 { compatible = "xlnx,zynq-devcfg-1.0"; interrupt-parent = <&&intc>; interrupts = <0 8 4>; reg = <0xf8007000 0x100>; clocks = <&&clkc 12>, <&&clkc 15>, <&&clkc 16>, <&&clkc 17>, <&&clkc 18>; clock-names = "ref_clk", "fclk0", "fclk1", "fclk2", "fclk3"; syscon = <&&slcr>; }; fpga_full: fpga-full { compatible = "fpga-region"; fpga-mgr = <&&devcfg>; #address-cells = <2>; #size-cells = <2>; };

3.使用tcl脚本自动创建bit.bin文件:我的工程在dev,tcl脚本放在dev目录即可:

############################################################## ####(1)使用tcl脚本自动生成ZYNQ PS端配置PL端所需的bit.bin文件 #### #### ############################################################## #设置bit文件名字 set bit_file_name radar_top #设置当前目录 set dev_dir [pwd] cd ${dev_dir}/project_1.runs/impl_1 #在bit文件路径下创建bif文件,w表示如果文件存在则清空文件内容,否则创建新的空文件 set f01 [open "Full_Bitstream.bif" w] #把字符串写入文件中 puts $f01 "all:\n{\n${bit_file_name}.bit\n}" #关掉文件 close $f01 #执行bootgen创建bin文件bootgen命令不是tcl命令,使用exec在命令行中执行,-w on为如果bin文件存在则强制覆盖 exec bootgen -w on -image Full_Bitstream.bif -arch zynq -process_bitstream bin #打印显示完成 puts "Bin file create finish!"

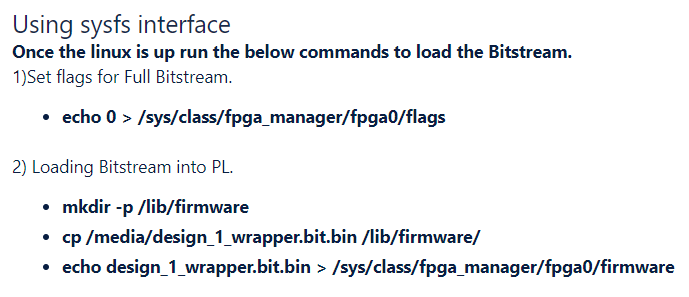

4.把bin文件放到Linux下并执行:

注意:如果使用了PS和PL端通信的DMA,在PL升级后linux下的对应驱动需要重新挂载。

以上。

浙公网安备 33010602011771号

浙公网安备 33010602011771号