去耦电容和旁路电容的区别与联系

http://www.elecfans.com/yuanqijian/dianrongqi/201910171093639.html

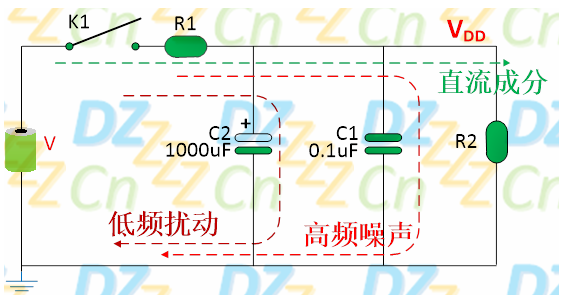

大电容滤除低频,小电容滤除高频

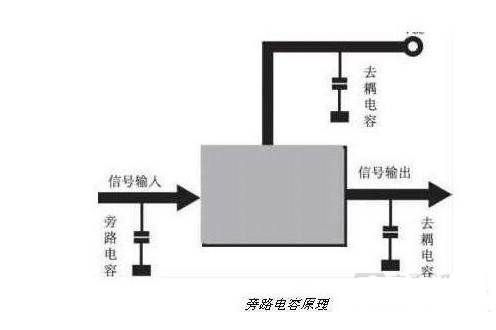

在电子电路中,去耦电容和旁路电容都是起到抗干扰的作用,电容所处的位置不同,称呼就不一样了。对于同一个电路来说,旁路(bypass)电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除,而去耦(decoupling,也称退耦)电容是把输出信号的干扰作为滤除对象。在供电电源和地之间也经常连接去耦电容,它有三个方面的作用:一是作为本集成电路的蓄能电容;二是滤除该器件产生的高频噪声,切断其通过供电回路进行传播的通路;三是防止电源携带的噪声对电路构成干扰。

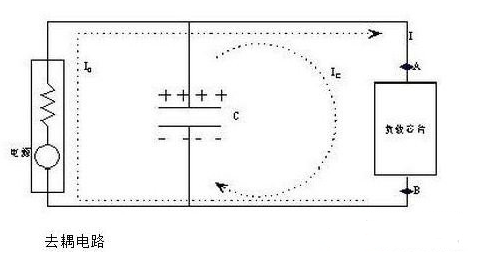

旁路电容是把输入信号中的干扰作为滤除对象,而去耦电容是把输出信号的干扰作为滤除对象,防止干扰信号返回电源。这应该是他们的本质区别。去耦电容相当于电池,避免由于电流的突变而使电压下降,相当于滤纹波。具体容值可以根据电流的大小、期望的纹波大小、作用时间的大小来计算。去耦电容一般都很大,对更高频率的噪声,基本无效。旁路电容就是针对高频来的,也就是利用了电容的频率阻抗特性。只是旁路电容一般是指高频旁路,也就是给高频的开关噪声提高一条低阻抗泄防途径。高频旁路电容一般比较小,根据谐振频率一般是0.1u,0.01u等 ,而去耦合电容一般比较大,是10u或者更大,依据电路中分布参数,以及驱动电流的变化大小来确定。

去耦电容(decoupling)也称退耦电容,是把输出信号的干扰作为滤除对象。去耦电容在集成电路电源和地之间的有两个作用:一方面是本集成电路的蓄能电容,另一方面旁路掉该器件的高频噪声(c对高频阻力小,将之泻至GND)。

http://www.elecfans.com/yuanqijian/dianrongqi/201910171093624.html

http://www.elecfans.com/yuanqijian/dianrongqi/201910171093607.html

http://www.elecfans.com/yuanqijian/dianrongqi/201910171093590.html

http://www.elecfans.com/d/729492.html

旁路电容是可将混有高频电流和低频电流的交流电中的高频成分旁路滤掉的电容。 对于同一个电路来说,旁路电容是把输入信号中的高频噪声作为滤除对象,把前级携带的高频杂波滤除,而去耦(也称退耦)电容是把输出信号的干扰作为滤除对象。

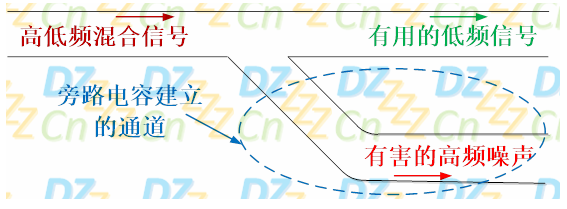

可将混有高频电流和低频电流的交流信号中的高频成分旁路滤掉的电容,称做“旁路电容”。旁路电容的主要功能是产生一个交流分路,从而消去进入易感区的那些不需要的能量,即当混有高频和低频的信号经过放大器被放大时,要求通过某一级时只允许低频信号输入到下一级,而不需要高频信号进入,则在该级的输入端加一个适当大小的接地电容,使较高频率的信号很容易通过此电容被旁路掉(这是因为电容对高频阻抗小),而低频信号由于电容对它的阻抗较大而被输送到下一级放大。

旁路电容不是理论概念,而是一个经常使用的实用方法,电子管或者晶体管是需要偏置的,就是决定工作点的直流供电条件。例如电子管的栅极相对于阴极往往要求加有负压,为了在一个直流电源下工作,就在阴极对地串接一个电阻,利用板流形成阴极的对地正电位,而栅极直流接地,这种偏置技术叫做“自偏”,但是对(交流)信号而言,这同时又是一个负反馈,为了消除这个影响,就在这个电阻上并联一个足够大的电容,这就叫旁路电容。

旁路电容(bypass capacitor)在高速数字逻辑电路中尤为常见,它的作用是在正常的通道(信号或电源,本文以电源旁路电容为例)旁边建立另外一个对高频噪声成分阻抗比较低的通路,从而将高频噪声成分从有用的信号用滤除,也因此而得名,如下图所示:

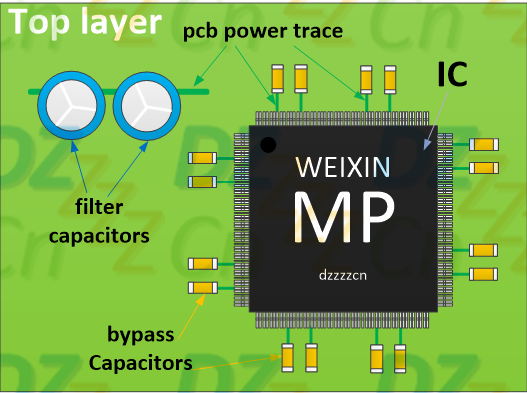

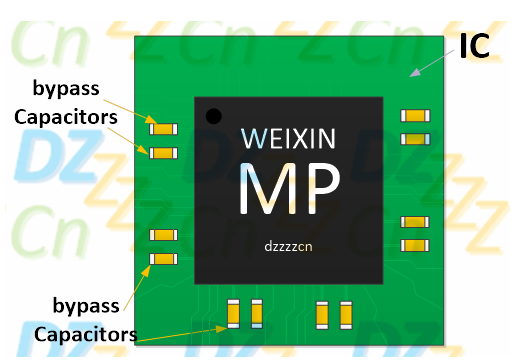

通常我们见到的旁路电容位置如下图所示:

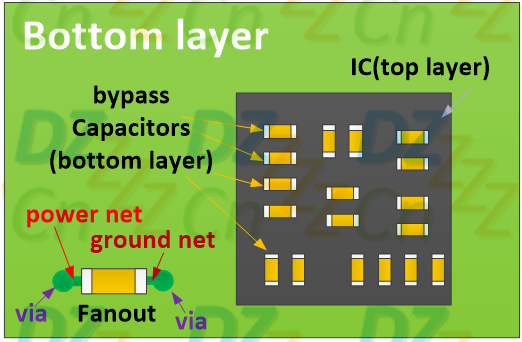

如果是高密度BGA(Ball Grid Array)封装芯片,则旁路电容通常会放在PCB底层(芯片的正下方),这些旁路电容会使用过孔扇出(Fanout)后与芯片的电源与地引脚连接,如下图所示:

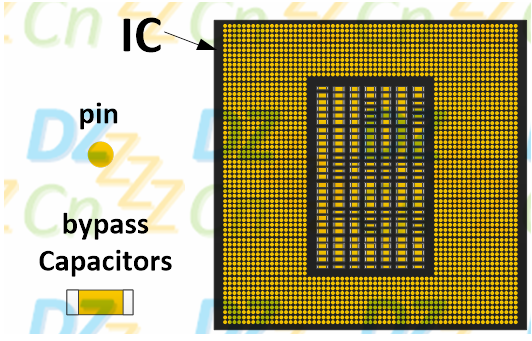

更有甚者,很多高速处理器芯片(通常也是BGA封装)在出厂时,已经将旁路电容贴在芯片上,如下图所示:

台式电脑的CPU(Central Processing Unit)一般都是用CPU插槽进行安装,很多CPU芯片的背面(是芯片的背面,而不是贴芯片的PCB板背面)也会有很多旁路电容,如下图所示:

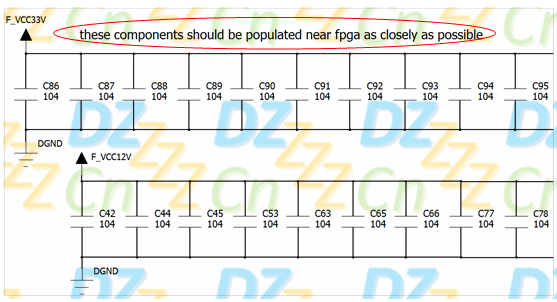

总之,旁路电容的位置总是会与主芯片越来越靠近,原理图设计工程师在进行电路设计时,也通常会将这些旁路电容的PCB LAYOUT要点标记起来,用来指导PCB布局布线工程师,如下图所示:

那么这里就有两个问题了:

(1)为什么旁路电容一定要与主芯片尽可能地靠近?

(2)为什么大多数旁路电容的值都是0.1uF(104)?这是巧合吗?

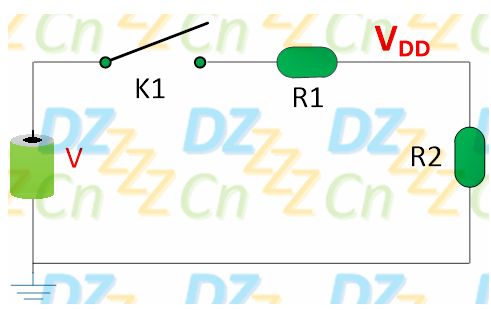

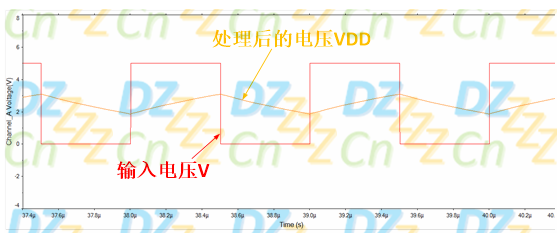

要讲清楚这两个问题,首先我们应该理解旁路电容存在的意义,很多人分不清滤波电容、旁路电容,其实本质上两者是没有任何区别,只不过在细节上对电容的要求有所不同。无论电容的应用场合名称叫什么,基本的(也是共同的)一点特性总是不会变的:储能。电容的这一特性使得外部供电电源有所波动时,与电容并联的对象两端的电压所受的影响减小,如下图所示:

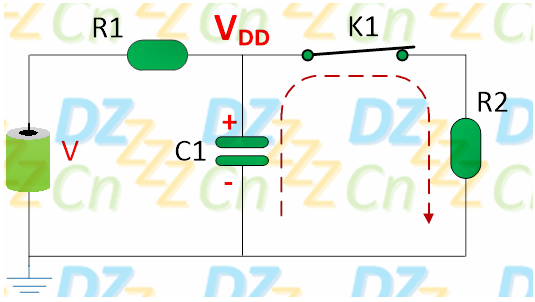

上图中,我们用开关K1来模拟扰动的来源,很明显,每一次开关K1闭合或断开时,在电阻R1与R2的分压下,电阻R2两端的电压(VDD)都是会实时跟随变化的(即波动很大),只不过电压幅度不一致而已,我们认为开关的切换动作已经产生了电源噪声。

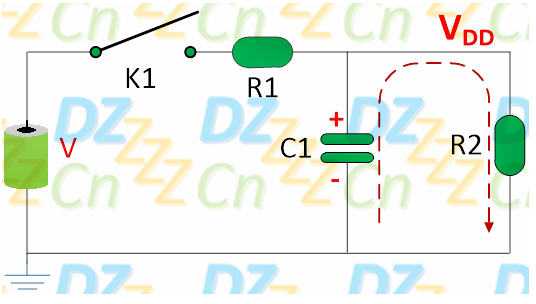

当我们在VDD节点与公共地之间并联一个电容C1后,如下图所示:

由于电容C1储能的作用,开关K1在开/关切换时,电容的充放电行为会使VDD更加平缓一些,如下图所示:

如果这个电容值比较大(一般在10uF以上,也有数千微法),我们就将其称为滤波电容,它可以将低频扰动成分滤除掉(但是对高频成分不管用),如果这个电容值比较小(一般1uF以下),我们称为旁路电容,它可以将高频成分滤除掉(对低频成分不管用),这两种电容起的都是滤除作用,如下图所示:

(本文以容值为滤波与旁路的区分仅限于数字电路,旨在说明两者区别,仅供参考,因为在模拟电路中很多容值并不小的电容也算是旁路电容,比如基本放大电路中的发射极电阻两端并联的电容,但本质都是一样的)

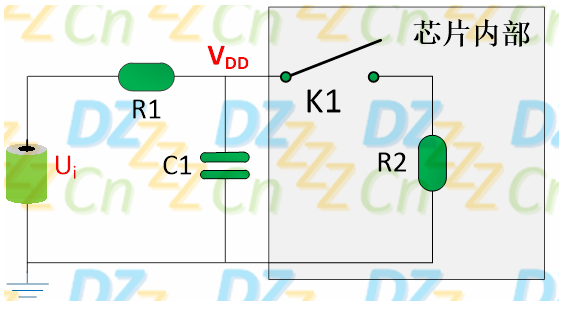

当然,我们也可以把模拟电源扰动开关K1放在如下图所示的位置,同样的道理,电容C1也可以在一定程度上削弱扰动对VDD带来的影响:

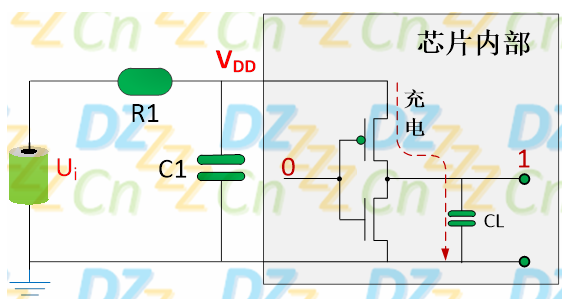

对于旁路电容的应用电路而言,开关K1与电阻R2为干扰的来源,我们可以把它们等效为芯片内部,如下图所示:

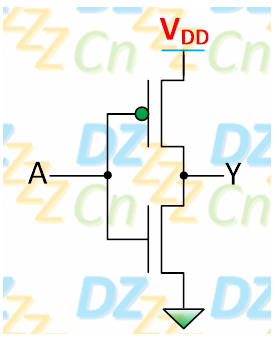

下面我们以74HC04(6反相器)芯片来分析一下,尽管电路规模很小,但原理都是一样的。我们在《逻辑门》系列文章有提到过,CMOS反相器的基本结构如下图所示:

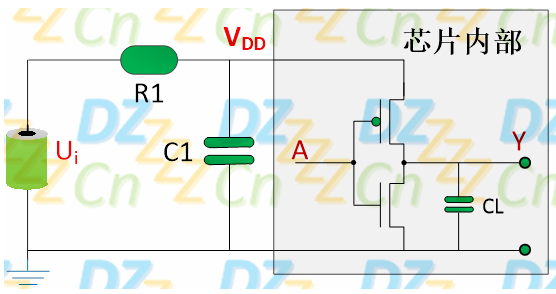

我们将这个反相器安装到上面的电路中去,则有如下图所示:

其中,电容CL为芯片内部等效负载电容,一般为几个pF,是数字集成电路中客观存在的,就算反相器输出没有连接额外的负载,芯片进行开关动作时也会消耗一定的电能(电荷)。

假设芯片逻辑输入电平由高H至低L变化(由低L至高H变换也是一样的道,本文不再赘述),PMOS(上侧带圈圈的)导通,NMOS截止,此时电流通路如下图所示:

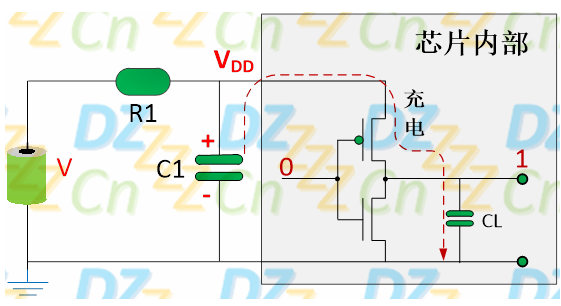

由于电容CL两端的电压不能突变,因此瞬间的充电电流(电荷)也不小,这个充电电流即来自于电源VDD,如果附近恰好有旁路电容,则由旁路电容中储存的电荷提供此消耗,如下图所示:

有人可能就说:就算旁路电容C1离芯片太远或没有,不是还有直流电源V提供VDD吗?也应该可以承担提供电能的责任呀?没错,当芯片产生的噪声成分属于低频是完全可以的,但是数字电路处于高低电平切换时情况就完全不一样了,因为开关的切换会产生谐波丰富的高频成分。

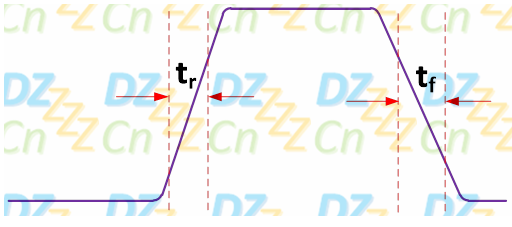

需要注意的是,这个谐波频率成分的高低不是指信号的切换频率,而取决于高低电平切换的上升或下降率,即上升时间tr(rising time)与下降时间tf(falling TIme),如下图所示:

高低电平变换时间越短,则产生的谐波(高频)成分越丰富,因此,低速开关并不意味着高频成分少,信号频率为1MHz方波存在的高频谐波成分比同频率正弦波要高得多,因为方波的高低电平切换时间非常短,而正弦波则相对非常缓慢。

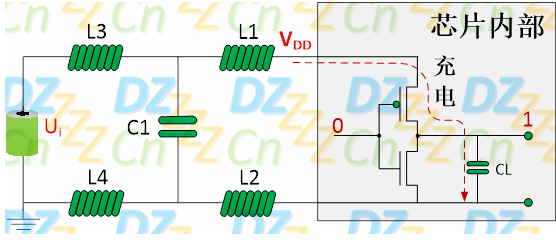

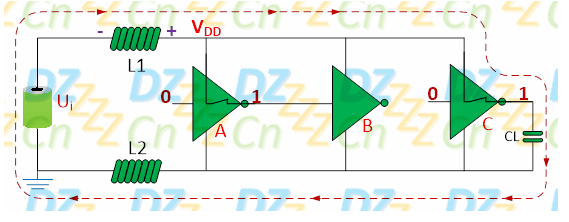

因此数字电路应使用下图所示的高频等效电路:

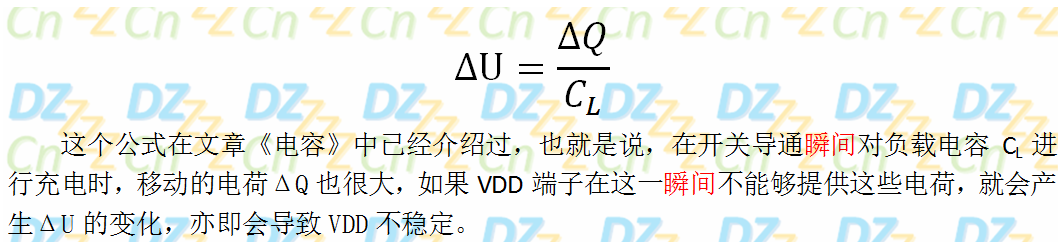

其中,L1、L2、L3、L4就是线路(包括过孔、引脚、走线)在高频下的等效电感,线路越长则等效电感越大,这些等效电感对高频信号相当于是高阻抗,这对于前级过来的高频干扰的抑制是有好处的,但同时对芯片内部(后级)开关切换带来的干扰也是有抑制作用的,这种抑制作用在旁路电容(或更远的直流电源V)与芯片之间形成了阻碍,使得VDD供电端子无法及时获取到足够电荷继而导致VDD瞬间下降(即变差),这种电压变化可以由下式来表达:

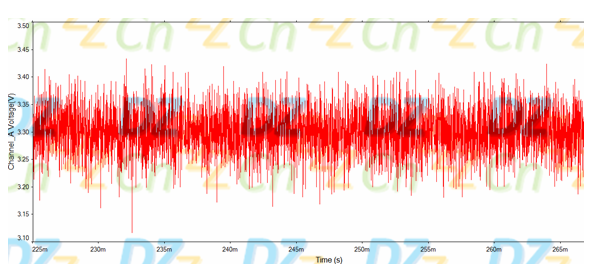

在大规模数字集成电路中会存在成千上万个等效开关同时切换,这些切换产生的瞬间电流都将使原本看似平稳的电源电压不再干净,继而使得芯片工作不再稳定,类似如下图所示:

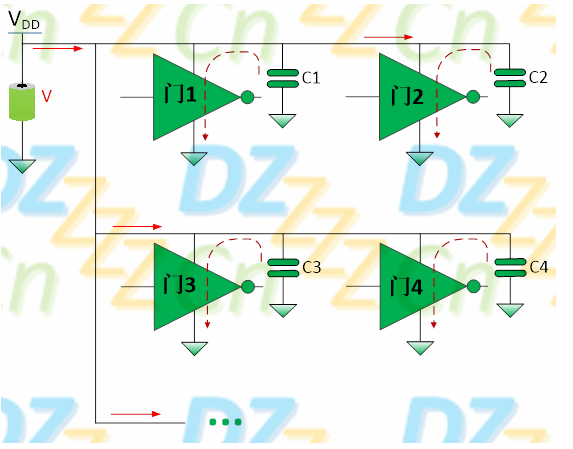

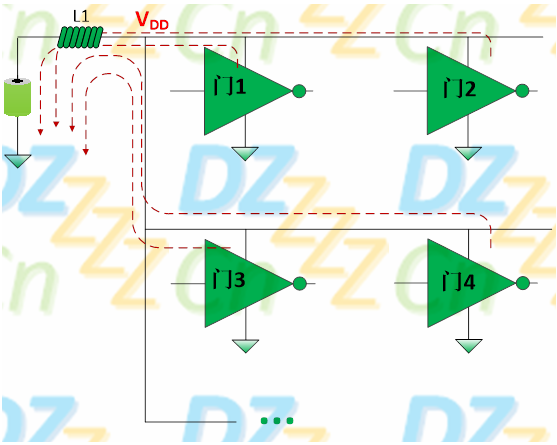

因此,通常我们会将旁路电容尽量地靠近芯片,这样使得旁路电容与芯片之间的引脚或走线的分布电感越小,从而能保证芯片能够及时获取足够的电荷。电路规模越大的芯片(如奔腾处理器),同一时间切换的逻辑会更多,因此也需要更多的电荷进行消耗电能的补充,外部需要并接的旁路电容也更多,如下图所示:

旁路电容所起的作用与现实生活中的扑灭小火灾的水龙头一样:假设家里出现了小火灾(相当于高频电源扰动),反应最快的肯定是从家里的水源处(相当于旁路电容)取水来扑灭,而不是第一时间拔打119电话。119火警扑灭火灾的能力(相当于外部电源V)肯定是最强的,它对于大火灾(相当于低频电源扰动)是最合适的,但是对于频繁出现的小火灾几乎没有什么用处,反应时间跟不上,等你赶过来时什么都烧完了(电路工作出现异常),还是家里的水龙头管用,虽然水源比较小,但对于小火灾却是足够用了。

有人可能就会说:搞那么麻烦做什么,为什么要并联这么多小电容?不就是那么些个储能电容,我在附近并联10 uF或100uF的电容不就都解决了么?以一个抵千百个,PCB布局布线更简单,么么哒!理想很丰满,现实很骨感。从单纯的储能角度来讲,是没有什么问题的!但旁路电容还有另外的重要功能:为每个高频信号提供良好的低阻抗返回路径,从而控制信号之间的串扰。

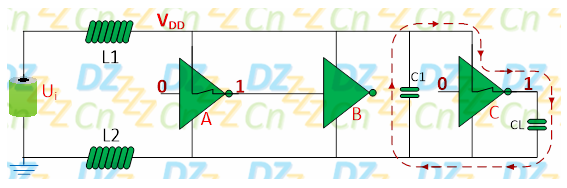

如下图所示,在门C的输出切换为高电平时,电池电源V将对负载电容CL充电,这个电流回路将产生瞬间的噪声电压(用L1、L2等效),如果同一时间门A的输出也切换为高电平,则门C产生的噪声电压将叠加在VDD上,从而影响到输出电平。

也就是说,其它门的噪声电压(也称为共路噪声)被传递到门A的输出端,同一时间逻辑切换越多则产生的共路噪声越大,一旦叠加在VDD上的共路噪声超过芯片的噪声容限,电路因无法有效地判断高低电平而导致异常,如下图所示:

为了改善这种共路噪声带来的影响,我们可以在每个芯片附近放置合适容值的旁路电容,由旁路电容建立电源与地之间的低阻抗回路,这样高频噪声就不会影响到其它门的正常工作,如下图所示:

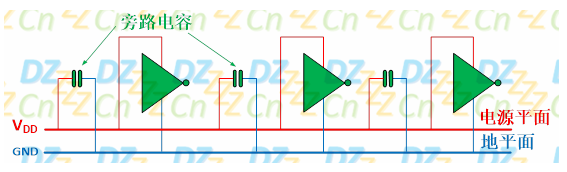

在实际应用中,我们会使用电源平面与地平面(减小分布电感,这些属于高速PCB设计内容,我们将在系列专栏文章中进行详细讲解),并配合旁路电容来为每一个芯片提供良好的低阻抗回路,如下图所示:

但我们在文章《电容》已经介绍过,实际的电容都有其自谐振频率,电容在高于自谐振频率时等效为一个电感,亦即不再是个电容了。我们也计算过10uF贴片陶瓷电容的自谐振频率约为1.6MHz,假设我们的芯片工作在10MHz(谐波频率成分甚至会达100MHz以上),此时并联10uF的电容相当于是不存在的(对于高频噪声成分相当于是开路的),因此,旁路电容的容量过大将起不到高频旁路的作用,另外,并联多个小电容的也可以在达到前述两个功能的前提下提升总电容的自谐振频率,这一点可以参考文章《电容》

作为旁路电容的容值一般不会大于1uF(以文章《电容》中所示1nH ESL计算其自谐振频率约为5MHZ,同类型电容的容量越小则自谐振频率越高),那旁路电容应该至少需要多少呢?我们下一节结合数据手册定量计算一下0.1uF容值的由来。

浙公网安备 33010602011771号

浙公网安备 33010602011771号