CMOS门电路

参考:https://wenku.baidu.com/view/8582501e964bcf84b9d57bd3.html

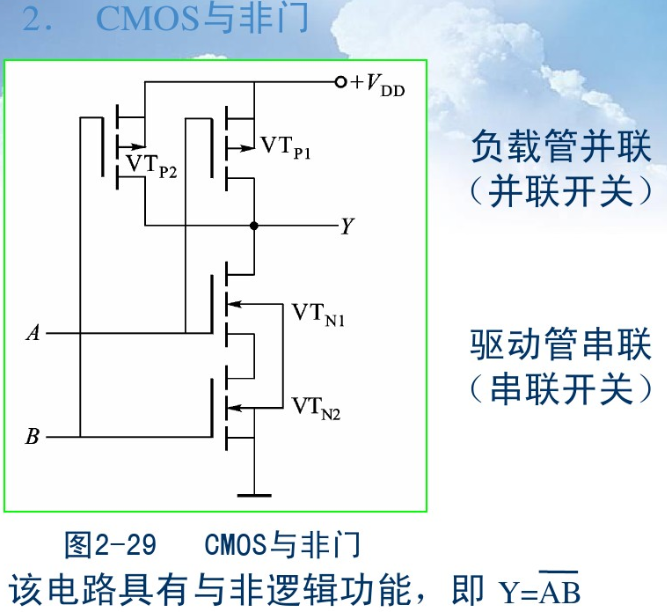

1. CMOS与非门(P并N串)

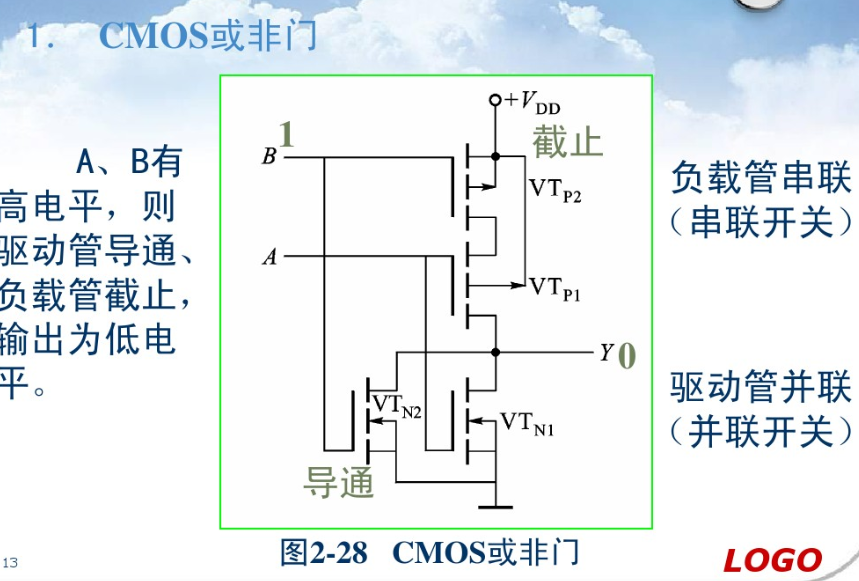

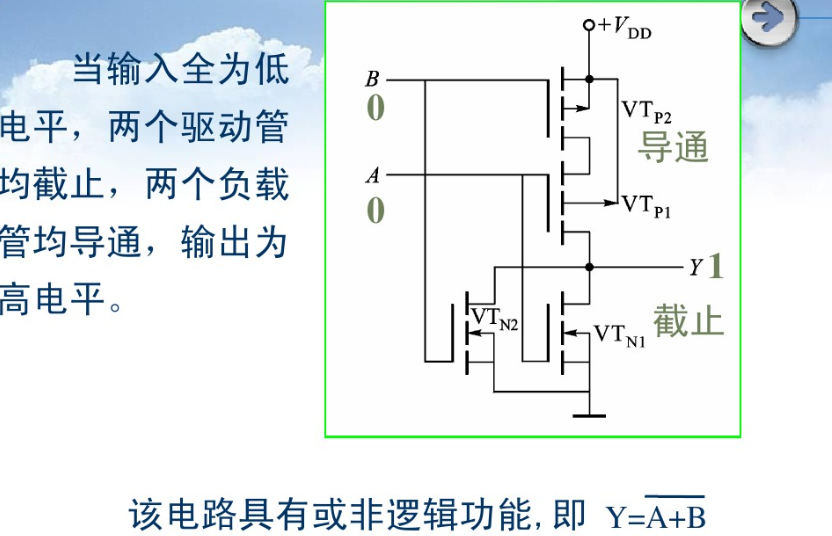

2. CMOS或非门(N并P串)

3. 在输入、输出级加反相器

4.MOS传输门和双向模拟开关

因为上面是P沟道,开启电压为负;下面是N沟道,开启电压是正。

1)当C接低电平,C'接高电平时,两者等效的电阻非常大,传输门断开。

2)当C接高电平,C'接低电平时,或者T(P)导通,或者T(N)导通,或者同时导通,此时传输门导通。

3)CMOS传输门特点:当传输门导通时,当一管导通电阻减小,则另一管导通电阻就增加,由于两管并联运行,可近似认为开关的导通电阻近似为一个常数,约几百欧,后接运放等输入阻抗较大的器件时可忽略不计。

4)CMOS传输门应用——CMOS模拟开关

当传输门导通的时候,可以直接传输模拟信号,作模拟开关使用,可广泛用于采样-保持、数模/模数转换、斩波电路中

5)利用CMOS传输门和CMOS反相器可以组合成各种复杂的逻辑电路,如异或门、数据选择器、寄存器、计数器等。

三、CMOS集成门电路的特点

1. 静态功耗低

例如:电源电压V(DD)=5V时,MSI电路的静态功耗<100mW,比较适合LSI电路

2. 电源电压范围宽

例如:CMOS4000系列V(DD)为3~18V

3. 输入阻抗高

例:正常工作的CMOS集成电路工作频率较低时,直流输入阻抗>100MΩ

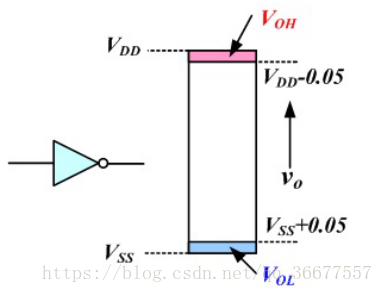

4. 逻辑摆幅大

例:空载时输出高电平V(OH)=(VDD-0.05V)~VDD;输出低电平V(OL)=VSS~(VSS+0.05)

5. 噪声容限大,抗干扰能力强

噪声容限是指在保证逻辑功能的前提下,对于输入信号(前级输出的标准电平)来说,在此输入信号电平基础上允许叠加的噪声(或干扰)电压的值。

CMOS集成电路的输入电压噪声容限可达电源电压的45%,而且高低电平噪声容限基本相等。

一般,VDD越高,噪声容限越大。

6. 扇出能力强

扇出系数是指门电路输出最多能带同类门的个数,ta反映了门电路最大带负载的能力。

例:低频工作时,一个CMOS门电路输出端可驱动50个以上的CMOS器件的输入端。

7. 温度稳定性好,且有较强的抗辐射能力;

集成度高,成本低;

8. CMOS集成电路的不足

4000系列的工作速度一般比TTL电路低;

功耗随频率升高而显著增大。

浙公网安备 33010602011771号

浙公网安备 33010602011771号