【FPGA】全局复位是否有必要?

在FPGA设计中,用户逻辑功能最终在芯片的实体资源上实现,所以逻辑写法不同最终影响两点:

1) 路径延迟; 2) 资源占用;

下面的例子对比非常明显,异步reset与同步reset。

(一) 同步复位

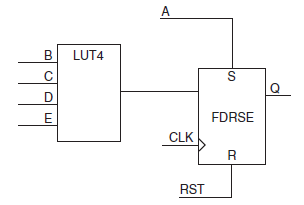

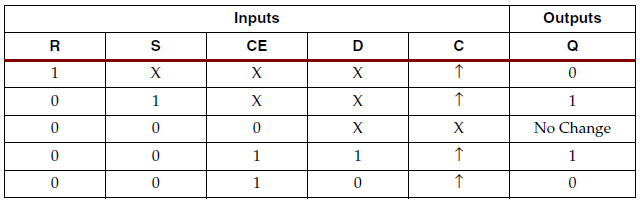

在always block中的所有输入信号都是同步的,A-E & RESET。因为优先级R>S>D,所以根据实际逻辑代码级层,充分利用了Reset、Set、Data同步输入引脚。

充分利用了资源管脚,同时只有LUT-FF两级延迟。

(二)异步复位

敏感列表中的RST是异步输入信号,使用的是Asynchronous Flip-Flop FDCE,RST连接到Clear异步脚。

那A-E五个同步信号就只能占用2xLUT4来实现,导致多一个LUT占用,同时延迟路径也多一级。

在实际设计中,一般由于clk时钟都很高,建议都用同步复位,还可以避免异步竞争冒险。

(三)没有复位

芯片中像 reg & sram 这样具有storage能力的触发器都具有初始值,完全可以不用Reset信号。

reg [7:0] data = 8'b11111111;// reg变量或者fsm状态机初始化定义,bram上电复位后全是00

如果代码中没有Reset,那么R脚完全可以接一个取非后的与逻辑输入信号。

优秀的代码结构完全可以带来量级的优化结果。

以上分析是针对Xilinx结构分析的,暂未分析Altera家,但两家都是基于sram型的FPGA,理应一致。

浙公网安备 33010602011771号

浙公网安备 33010602011771号