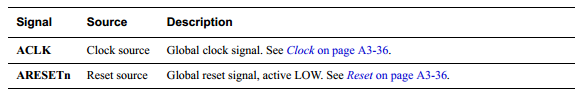

【vivado】AXI4接口verilog代码分析

用vivado创建new AXI4 IP,配置:AXI4-Full,Master。分析内部关于AXI4接口自动产生的代码。

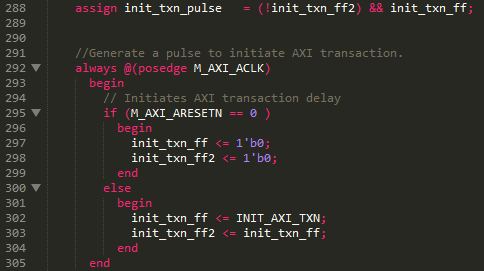

1、在 M_AXI_ACLK 同步时钟下,抓取 INIT_AXI_TXN 由低变高,让 init_txn_pulse 产生个pulse信号;

2、输入信号 INIT_AXI_TXN 是这个ip的一个输入信号,是由用户在PL或PS侧控制,下有说明;

3、产生信号 init_txn_pulse 负责在运行中初始化接口的关键控制信号,如同 M_AXI_ARESETN 下的初始化;

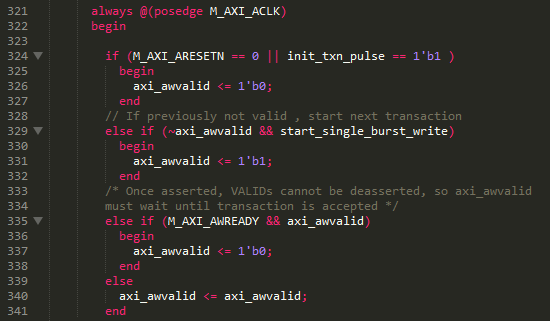

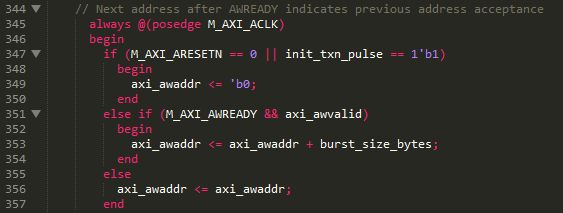

Write Address Channel

1、大部分接口都是固定值设置;awburst=01,地址设置成INCR递增模式;

2、首先协议要求,复位时master侧的arvalid、awvalid、wvalid必须low;

3、从代码判断,初始时ready=0(axi4协议推荐1),start一次burst是16*4B,一次burst结束后slave侧ready=1,master侧valid=0,addr+size;

4、从这里可以看出 init_txn_pulse 可以让地址回到起始,准备下次覆盖;

5 、可以看出axi总线的地址是按照byte为单位,而不是width;

burst_size_bytes = C_M_AXI_BURST_LEN * C_M_AXI_DATA_WIDTH/8 = 16* 32/8 = 64 Byte;

Write Data Channel

1、wlast=1的条件,C_M_AXI_BURST_LEN是对burst的区别,这里是16,只考虑(write_index == 16 - 2) && wnext

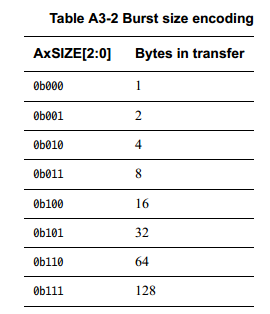

1、clogb函数功能是把 len / width,转换成AxSIZE的匹配mode。规范的代码都是按照一定的规则来定义对应关系的。

附录:

amba_axi_protocol_spec.pdf

浙公网安备 33010602011771号

浙公网安备 33010602011771号