【电路】JTAG下载器研究

这是一款Xilinx FPGA的下载器。

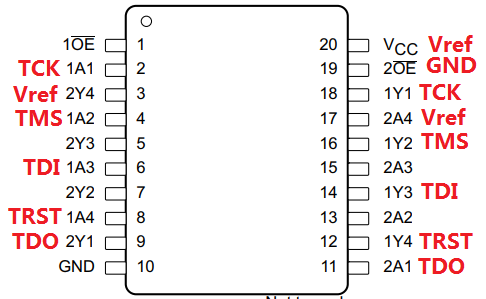

左侧USB接口经过Cypress的usb控制器CY7C68013A-100AXC做接口转换,然后跟Lattice的LFXP2-17E-6FTN256I通信,这个小FPGA用来实现jtag协议,最后经过SN74LVC244A buffer后输出到jtag接口。

Vref来自目标单板的jtag供电;

2OE接地,所以2A->2Y通道是默认打开的。Vref供电经过2A4送入FPGA,一旦检测到有电,将下载器的绿灯点亮;

1OE受FPGA控制,有个20k上拉,检测到Vref后1OE会打开一段时间,通过jtag查询链路是否有器件;

输出信号TCK/TMS/TDI/TRST,在左侧有20k上拉到+3.3V,在右侧也有20k上拉到Vref,然后经过33欧电阻,再挂上ESD管;

假如Vref=+2.5v(非3.3v),

那么1A侧的输入电平是3.3v的,1Y侧的输出电平是2.5v的;而2A侧的输入电平是2.5V,2Y侧的输入电平也是2.5v到FPGA。

实测是可以工作的,符合FPGA侧bank电压3.3v的LVCMOS输入标准。

例如2A4的Vref输入2.5v,测2Y4上的电压2.5v,VIH>2v,正确识别高电平。

浙公网安备 33010602011771号

浙公网安备 33010602011771号