【电路】差分接口互连(二)

- LVDS接口类型

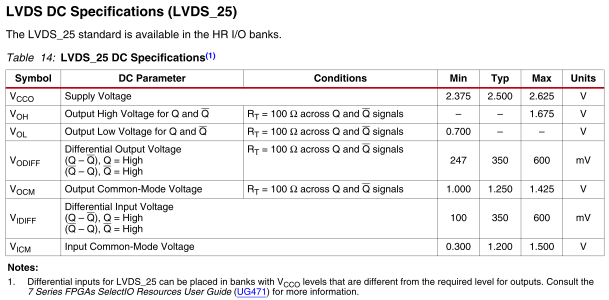

一种是HR bank的LVDS_25,Vcco=2.5V,也就是通常说的LVDS接口。

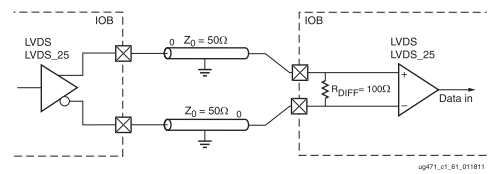

The LVDS_25 I/O standard is only available in the HR I/O banks. It requires a VCCO to be powered at 2.5V for outputs and for inputs when the optional internal differential termination is implemented (DIFF_TERM = TRUE).

一种是HP bank的LVDS,Vcco=1.8V

The LVDS I/O standard is only available in the HP I/O banks. It requires a VCCO to be powered at 1.8V for outputs and for inputs when the optional internal differential termination is implemented (DIFF_TERM = TRUE).

这句话的意思是,作为LVDS的输出或者作为输入且选择了内部终端电阻,那么VCCO的电压必须设置成1.8V(或者HR的2.5V)。

It is acceptable to have differential inputs such as LVDS and LVDS_25 in I/O banks that are powered at voltage levels other than the nominal voltages required for the outputs of those standards (1.8V for LVDS outputs, and 2.5V for LVDS_25 outputs).

However, these criteria must be met:(ug471_7Series_SelectIO, P92)

• The optional internal differential termination is not used (DIFF_TERM = FALSE, which is the default value).

• The differential signals at the input pins meet the VIN requirements in the Recommended Operating Conditions table of the specific device family data sheet

• The differential signals at the input pins meet the VIDIFF (min) requirements in the corresponding LVDS or LVDS_25 DC specifications tables of the specific device family data sheet

• For HR I/O banks in bidirectional configuration, internal differential termination is always used.

但是,如果只作为输入则不受Vcco=1.8V/2.5V限制,因为输入信号并不关心Vcco输出电压,只参考VREF电压(可选VREF_pin或者原语的 Internal_VREF)。

一般上级2.5V LVDS输出到1.5V bank是可以直连的,DC可以满足要求。但是想输入到DDR3L 1.35V的bank就需要注意些:

1、内部终端电阻不能选,必须外接;2、前级输出的DC特性要满足1.35V输入要求。

但是每个bank都有对应的VREF(外接电阻或者内部原语),可以将输入偏置在Vcco/2,所以作为输入也是没有问题的。

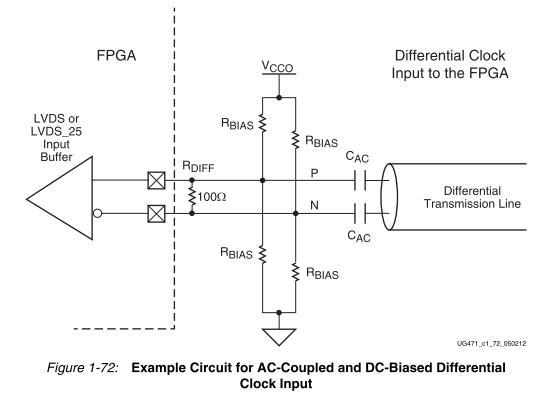

- AC-couples and DC-biases the input signals

最保险的做法是采用上面的AC耦合电路,不用关心前级的直流量,只有交流信号通过,然后在输出端配置一个VCCO/2偏置电压。

总结,通常说的LVDS是2.5V的供电接口,但HP也提供1.8V的供电接口,因为DC参数完全满足。在2.5V/1.8V的bank中,可以任意配置Lvds Ourput Input,但是在其他Vcco供电bank中,就只能谨慎有条件的配置成Lvds Input,不能作为Lvds Output。

浙公网安备 33010602011771号

浙公网安备 33010602011771号