System Verilog(1)logic 和 bit, byte, shortint, int, longint

零基础转验证程序媛

- 自学数电,verilog,刷完HDL bits

- 看完了启芯关于SV的系列课程

- 接下来做一些代码练习,写blog记录一下

学习资源

http:// www.chipverify.com 上的一些实例, 启芯课程, 绿皮书

仿真工具

EDA playground

SV语法(1) data_type

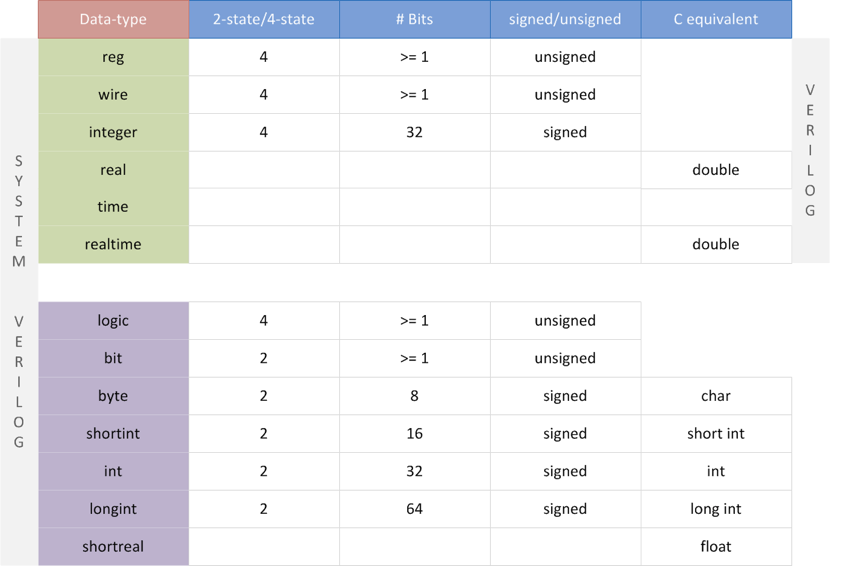

Verilog 的数据类型主要是线网和变量,即 wire, reg, integer,都是四值逻辑(0、1、x、z)

在verilog基础上,SV增加了二值逻辑(0、1)变量来简化运算, 包含 bit, byte, shortint, int, longint 变量。

SV中logic与verilog中的reg变量对应,为四值逻辑的无符号数;bit为二值逻辑的无符号数;

byte, int, shortint, longint 均为二值逻辑有符号数,注意区分。

// 二值逻辑在验证平台上可以简化计算,但用在RTL逻辑综合时容易出现问题

下面做一些实例,以熟悉各数据类型和相应变量的声明语法

1. logic 变量的连续赋值和过程赋值

// logic 变量默认值为x

module tb;

logic [3:0] my_data; // declare a 4-bit logic type variable;

logic en; // declare a 1-bit logic type variable;

// logic变量既可以在过程语句中被赋值,也可以被连续赋值(用assign赋值)

initial begin

$display ("my_data = 0x%0h en = %0b", my_data, en);

// 以最小十六进制打印 my_data, 以最小十进制打印 en(默认值)

my_data = 4'hB;

// 过程语句中给logic变量赋值

$display ("my_data = 0x%0h en = %0b", my_data, en);

// 赋值同时打印两个logic变量

#1;

// 延时1个时间单位

$display ("my_data= 0x%0h en = %0b",my_data,en);

// 延时后再打印两个logic 变量

end

assign en = my_data[0]; // 连续赋值en

endmodule // tb

编译结果

# Loading sv_std.std

# Loading work.tb(fast)

# vsim -voptargs=+acc=npr

# run -all

# my_data = 0xx en = x

# my_data = 0xb en = x

# my_data= 0xb en = 1

# exit

# End time: 06:43:28 on Mar 29,2022, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

Done

2. bit 变量的赋值

1 module tb; 2 bit var_a ; 3 bit [3:0] var_b ; 4 5 logic [3:0] x_val ; 6 7 initial begin 8 9 $display("initial value var_a = %0b, var_b = 0x%0h", var_a, var_b) ; 10 11 // 查看bit类型变量默认值,默认值都是0. var_a = 0, var_b = 0x0 12 13 var_a= 1; 14 15 var_b= 4'hb; 16 17 $display("first value value var_a = %0b, var_b = 0x%0h", var_a, var_b) ; 18 19 var_b= 16'h481a; 20 21 $display("tructuated value: var_b= 0x%0h", var_b) ; 22 23 // 如果赋值超过位宽会怎么样呢? 只有最右边的a被赋值到b变量里了 var_b = 0xa 24 25 var_b=4'h01zx; 26 27 $display("var_b = %b", var_b) ; 28 29 // 四值逻辑在转化为二值逻辑时,未知状态x以及高阻态z都会被强制转化为0,var_b = 0000 30 31 // logic和bit类型都是可综合的,但bit类型多用于testbench中 32 33 end 34 35 endmodule

编译结果

# Loading sv_std.std

# Loading work.tb(fast)

#

# vsim -voptargs=+acc=npr

# run -all

# initial value var_a = 0, var_b = 0x0

# first value value var_a = 1, var_b = 0xb

# tructuated value: var_b= 0xa

# var_b = 0000

# exit

# End time: 06:51:49 on Mar 29,2022, Elapsed time: 0:00:01

# Errors: 0, Warnings: 0

Done

3. 有符号数 byte, int, shortint, longint 的赋值

1 // 有符号数据类型: byte, shortint, int, longint 2 3 4 module tb ; 5 6 shortint var_a; // 16 bits 7 8 int var_b; // 32 bits 9 10 longint var_c; // 64 bits 11 12 byte var_d; // 8 bits -128~127 13 14 byte unsigned var_u; // 8 bits unsigned 0~255 15 16 17 18 initial begin 19 20 $display("sizes var_a=%0d, var_b=%0d , var_c=%0d", $bits(var_a), $bits(var_b), $bits(var_c)); 21 22 #1 23 24 $display("default values var_a=%0h, var_b=%0h, var_c=%0h",var_a, var_b, var_c); 25 26 #1 27 28 var_a = 'h7FFF ; 29 30 var_b = 'h7FFF_FFFF ; 31 32 var_c = 'h7FFF_FFFF_FFFF_FFFF ; 33 34 var_d = 'h7F ; // 127 35 36 var_u = 'h7F ; // 127 37 38 $display("new values var_a=%0h, var_b=%0h, var_c=%0h, var_d=%0h, var_u=%0h",var_a, var_b, var_c, var_d, var_u); 39 40 #1 41 42 var_a += 1 ; 43 44 var_b += 1 ; 45 46 var_c += 1 ; 47 48 var_d += 1 ; // -128 49 50 var_u += 1 ; // 128 51 52 53 54 55 end // initial 56 57 58 59 initial begin 60 61 $monitor("monitoring [%0t ns] var_a=%0d var_b=%0d var_c=%0d var_d=%0d var_u=%0d ", $time, var_a, var_b, var_c, var_d, var_u); 62 63 end 64 65 66 67 endmodule // tb

编译结果

# Loading sv_std.std

# Loading work.tb(fast)

#

# vsim -voptargs=+acc=npr

# run -all

# sizes var_a=16, var_b=32 , var_c=64

# monitoring [0 ns] var_a=0 var_b=0 var_c=0 var_d=0 var_u=0

# default values var_a=0, var_b=0, var_c=0

# new values var_a=7fff, var_b=7fffffff, var_c=7fffffffffffffff, var_d=7f, var_u=7f

# monitoring [2 ns] var_a=32767 var_b=2147483647 var_c=9223372036854775807 var_d=127 var_u=127

# monitoring [3 ns] var_a=-32768 var_b=-2147483648 var_c=-9223372036854775808 var_d=-128 var_u=128

# exit

# End time: 07:05:14 on Mar 29,2022, Elapsed time: 0:00:02

# Errors: 0, Warnings: 0

Done

浙公网安备 33010602011771号

浙公网安备 33010602011771号