MAC和PHY关系

以太网MAC是什么

MAC即 Media Access Control,即 媒体访问控制子协议。该协议位于OSI七层协议中数据链路层的下半部分, 主要负责控制与连接物理层的物理介质。

在发送数据的时候,MAC协议可以事先判断是否可以发送数据,如果可以发送将给数据加上一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;

在接收数据的时候,MAC协议首先判断输入的信息并是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。

该层协议是以太网MAC由IEEE-802.3以太网标准定义。最新的MAC同时支持10Mbps和100Mbps两种速率。

以太网数据链路层其实包含MAC(介质访问控制)子层和LLC(逻辑链路控制)子层.一块以太网卡MAC芯片的作用不但要实现MAC子层和LLC子层的功能,还要提供符合规范的PCI界面以实现和主机的数据交换.

什么是MII

MII即媒体独立接口,它是IEEE-802.3定义的以太网行业标准. "媒体独立"表明在不对MAC硬件重新设计或替换的情况下,任何类型的PHY设备都可以正常工作.

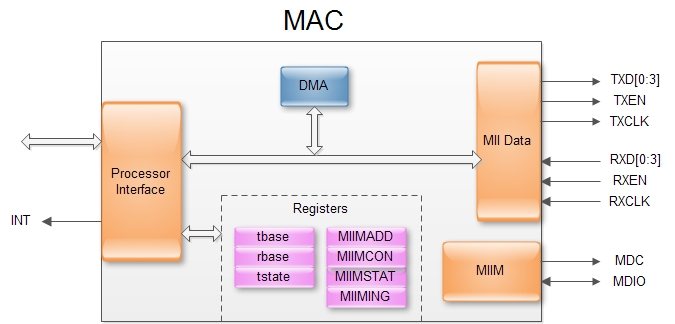

它包括一个数据接口,以及一个MAC和PHY之间的管理接口.

- 数据接口包括分别用于发送器和接收器的两条独立信道.每条信道都有自己的数据,时钟和控制信号.

MII数据接口总共需要16个信号,包括

![]()

MII以4位半字节方式传送数据双向传输,时钟速率25MHz.其工作速率可达100Mb/s;

- MII管理接口是个双信号接口,一个是时钟信号,另一个是数据信号.通过管理接口,上层能监视和控制PHY.

其管理是使用SMI(Serial Management Interface)总线通过读写PHY的寄存器来完成的.

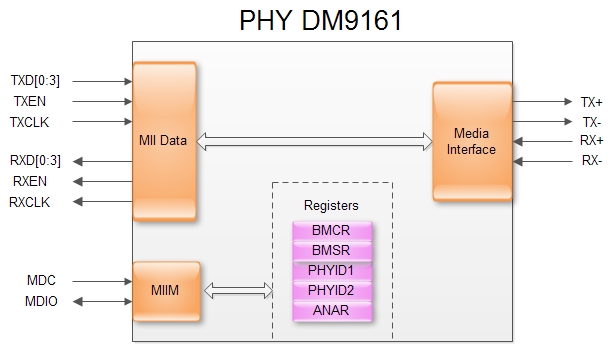

PHY里面的部分寄存器是IEEE定义的,这样PHY把自己的目前的状态反映到寄存器里面,MAC通过SMI总线不断的读取PHY的状态寄存器以得知目前PHY的状态,

例如连接速度,双工的能力等.当然也可以通过SMI设置PHY的寄存器达到控制的目的,例如流控的打开关闭,自协商模式还是强制模式等.不论是物理连接的MII总线和SMI总线还是PHY的状态寄存器和控制寄存器都是有IEEE的规范的,因此不同公司的MAC和PHY一样可以协调工作.当然为了配合不同公司的PHY的自己特有的一些功能,驱动需要做相应的修改.

MII支持10Mbps和100Mbps的操作,一个接口由14根线组成,它的支持还是比较灵活的,但是有一个缺点是因为它一个端口用的信号线太多,

如果一个8端口的交换机要用到112根线,16端口就要用到224根线,到32端口的话就要用到448根线,一般按照这个接口做交换机,是不太现实的,所以现代的交换机的制作都会用到其它的一些从MII简化出来的标准,比如RMII,SMII,GMII等.

RMII是简化的MII接口,在数据的收发上它比MII接口少了一倍的信号线,所以它一般要求是50MHz的总线时钟.

RMII一般用在多端口的交换机,它不是每个端口安排收,发两个时钟,而是所有的数据端口公用一个时钟用于所有端口的收发,这里就节省了不少的端口数目.RMII的一个端口要求7个数据线,比MII少了一倍,所以交换机能够接入多一倍数据的端口.

和MII一样,RMII支持10Mbps和100Mbps的总线接口速度.

SMII是由思科提出的一种媒体接口,它有比RMII更少的信号线数目,S表示串行的意思.

因为它只用一根信号线传送发送数据,一根信号线传输接受数据,所以为了满足100Mbps的总线接口速度的需求,它的时钟频率就达到了125MHz,

为什么用125MHz,是因为数据线里面会传送一些控制信息.SMII一个端口仅用4根信号线完成100Mbps的传输,比起RMII差不多又少了一倍的信号线.

SMII在工业界的支持力度是很高的.同理,所有端口的数据收发都公用同一个外部的125MHz时钟.

GMII(Gigabit MII)是千兆网的MII接口,这个也有相应的RGMII接口,表示简化了的GMII接口.

GMII采用8位接口数据,工作时钟125MHz,因此传输速率可达1000Mbps.同时兼容MII所规定的10/100 Mbps工作方式.

GMII接口数据结构符合IEEE以太网标准.该接口定义见IEEE 802.3-2000.

以太网PHY是什么?

PHY是物理接口收发器,它实现物理层.IEEE-802.3标准定义了以太网PHY.包括MII/GMII(介质独立接口)子层,PCS(物理编码子层),PMA(物理介质附加)子层,PMD(物理介质相关)子层,MDI子层.

它符合IEEE-802.3k中用于10BaseT(第14条)和100BaseTX(第24条和第25条)的规范.

PHY在发送数据的时候,收到MAC过来的数据(对PHY来说,没有帧的概念,对它来说,都是数据而不管什么地址,数据还是CRC.

对于100BaseTX因为使用4B/5B编码,每4bit就增加1bit的检错码),然后把并行数据转化为串行流数据,再按照物理层的编码规则把数据编码,再变为模拟信号把数据送出去.收数据时的流程反之.

PHY还有个重要的功能就是实现CSMA/CD的部分功能.它可以检测到网络上是否有数据在传送,如果有数据在传送中就等待,一旦检测到网络空闲,再等待一个随机时间后将送数据出去.如果两个碰巧同时送出了数据,那样必将造成冲突,这时候,冲突检测机构可以检测到冲突,然后各等待一个随机的时间重新发送数据.

这个随机时间很有讲究的,并不是一个常数,在不同的时刻计算出来的随机时间都是不同的,而且有多重算法来应付出现概率很低的同两台主机之间的第二次冲突.

除此之外PHY还提供了和对端设备连接的重要功能并通过LED灯显示出自己目前的连接的状态和工作状态让我们知道.

当我们给网卡接入网线的时候,PHY不断发出的脉冲信号检测到对端有设备,它们通过标准的”语言”交流,互相协商并却定连接速度、双工模式、是否采用流控等.

通常情况下,协商的结果是两个设备中能同时支持的最大速度和最好的双工模式.这个技术被称为AutoNegotiation或者NWAY,它们是一个意思–自动协商.

具体传输过程为,发送数据时,网卡首先侦听介质上是否有载波(载波由电压指示),如果有,则认为其他站点正在传送信息,继续侦听介质.

一旦通信介质在一定时间段内(称为帧间缝隙IFG=9.6微秒)是安静的,即没有被其他站点占用,则开始进行帧数据发送,同时继续侦听通信介质,以检测冲突.

在发送数据期间,如果检测到冲突,则立即停止该次发送,并向介质发送一个“阻塞”信号,告知其他站点已经发生冲突,从而丢弃那些可能一直在接收的受到损坏的帧数据,并等待一段随机时间(CSMA/CD确定等待时间的算法是二进制指数退避算法).

在等待一段随机时间后,再进行新的发送.如果重传多次后(大于16次)仍发生冲突,就放弃发送.接收时,网卡浏览介质上传输的每个帧,如果其长度小于64字节,则认为是冲突碎片.

如果接收到的帧不是冲突碎片且目的地址是本地地址,则对帧进行完整性校验,如果帧长度大于1518字节(称为超长帧,可能由错误的LAN驱动程序或干扰造成)或未能通过CRC校验,则认为该帧发生了畸变.

通过校验的帧被认为是有效的,网卡将它接收下来进行本地处理.

造成以太网MAC和PHY单片整合难度高的原因是什么?

PHY整合了大量模拟硬件,而MAC是典型的全数字器件.芯片面积及模拟/数字混合架构是为什么先将MAC集成进微控制器而将PHY留在片外的原因.

更灵活、密度更高的芯片技术已经可以实现MAC和PHY的单芯片整合.

10BaseT和100BaseTX PHY实现方式不同的原因何在?

两种实现的分组描述本质上是一样的,但两者的信令机制完全不同.其目的是阻止一种硬件实现容易地处理两种速度.

- 10BaseT采用曼彻斯特编码

- 100BaseTX采用4B/5B编码

网卡的MAC和PHY间的关系?

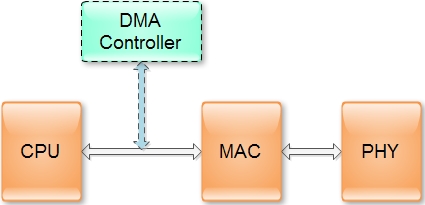

下图是网口结构简图.网口由CPU、MAC和PHY三部分组成.DMA控制器通常属于CPU的一部分,用虚线放在这里是为了表示DMA控制器可能会参与到网口数据传输中.

网卡工作在osi的最后两层,物理层和数据链路层,物理层定义了数据传送与接收所需要的电与光信号、线路状态、时钟基准、数据编码和电路等,并向数据链路层设备提供标准接口.

物理层的芯片称之为PHY.数据链路层则提供寻址机构、数据帧的构建、数据差错检查、传送控制、向网络层提供标准的数据接口等功能.

以太网卡中数据链路层的芯片称之为MAC控制器.很多网卡的这两个部分是做到一起的.他们之间的关系是pci总线接mac总线,mac接phy,phy接网线(当然也不是直接接上的,还有一个变压装置).

PHY和MAC之间是如何传送数据和相互沟通的.通过IEEE定义的标准的MII/GigaMII(Media Independed Interfade,介质独立界面)界面连接MAC和PHY.

这个界面是IEEE定义的.MII界面传递了网络的所有数据和数据的控制.ETHERNET的接口实质是MAC通过MII总线控制PHY的过程.

Good Good Study! Day Day Up!

浙公网安备 33010602011771号

浙公网安备 33010602011771号