题目网站

参考的CSDN网站

module top_module (

input clk,

input resetn, // active-low synchronous reset

input x,

input y,

output f,

output g

);

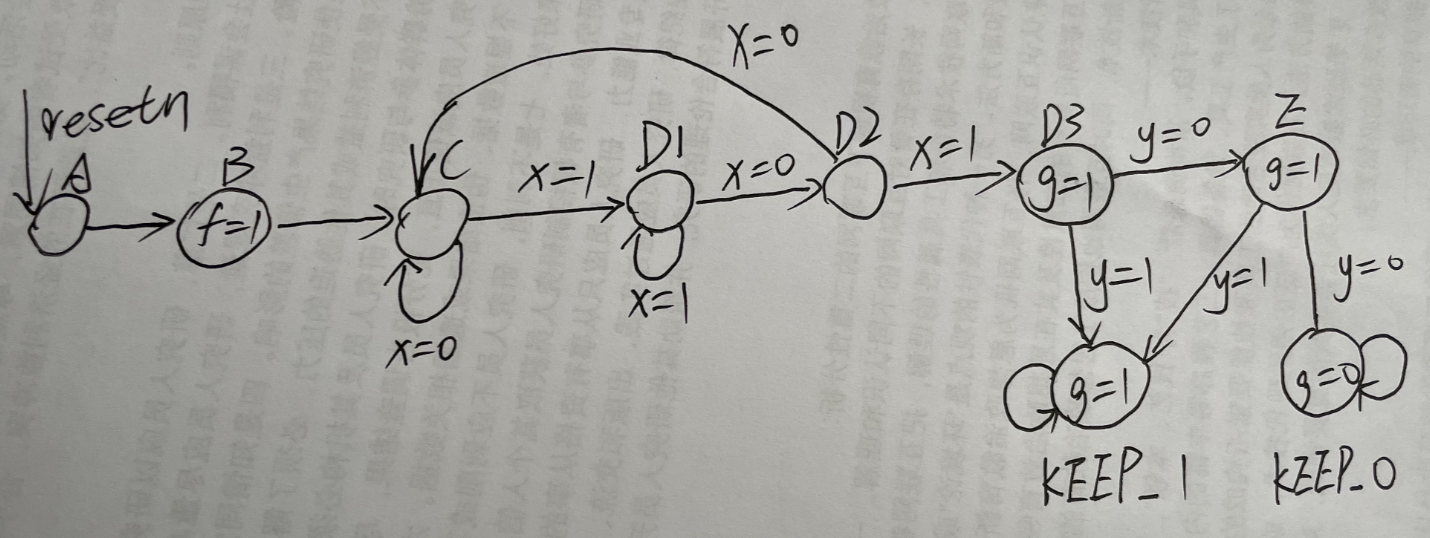

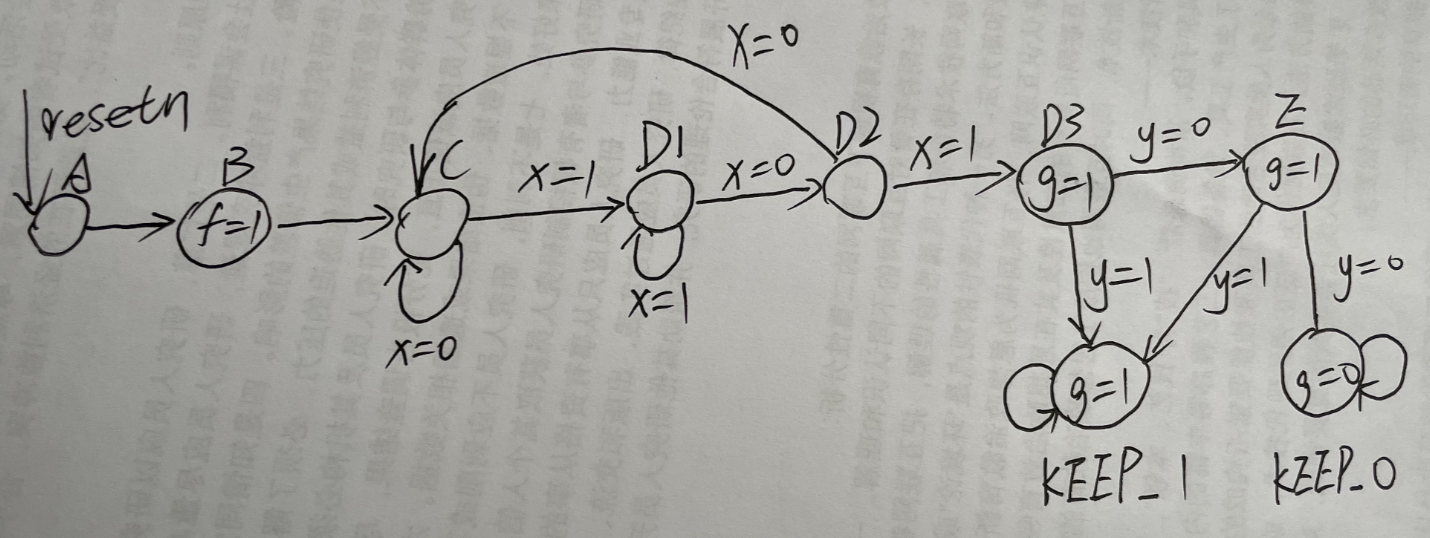

parameter A=0, B=1, C=2, D1=3, D2=4, D3=5, E=6, KEEP_1=7, KEEP_0=8;

reg [3:0] state, next_state;

always @(*) begin

case(state)

A: next_state = B;

B: next_state = C;

C: next_state = x ? D1:C;

D1: next_state = x ? D1:D2;

D2: next_state = x ? D3:C;

D3: next_state = y ? KEEP_1:E;

E: next_state = y ? KEEP_1:KEEP_0;

KEEP_1: next_state = KEEP_1;

KEEP_0: next_state = KEEP_0;

default: next_state = A;

endcase

end

always @(posedge clk) begin

if(~resetn) state <= A;

else state <= next_state;

end

assign f = (state==B);

assign g = (state==D3) || (state==E) || (state==KEEP_1);

endmodule

浙公网安备 33010602011771号

浙公网安备 33010602011771号