Q3a:FSM

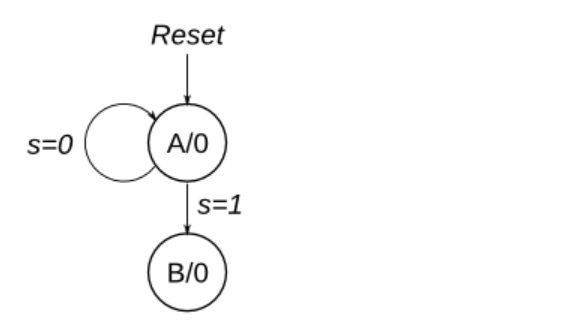

Consider a finite state machine with inputs s and w. Assume that the FSM begins in a reset state called A, as depicted below. The FSM remains in state A as long as s = 0, and it moves to state B when s = 1. Once in state B the FSM examines the value of the input w in the next three clock cycles. If w = 1 in exactly two of these clock cycles, then the FSM has to set an output z to 1 in the following clock cycle. Otherwise z has to be 0. The FSM continues checking w for the next three clock cycles, and so on. The timing diagram below illustrates the required values of z for different values of w.

Use as few states as possible. Note that the s input is used only in state A, so you need to consider just the w input.

考虑一个具有输入 s 和 w 的有限状态机。假设 FSM 以名为 A 的复位状态开始, 如下图所示。只要 s = 0,FSM 就会保持在状态 A,当 s = 1 时,它会移动到状态 B。一旦进入状态 B,FSM 就会在接下来的三个状态中检查输入 w 的值 时钟周期。如果 w = 1 恰好是其中两个时钟周期,则 FSM 必须在下一个时钟周期中将输出 z 设置为 1。否则,z 必须为 0。FSM 继续检查 w 接下来的三个时钟周期,依此类推。下面的时序图说明了所需的值 的 z 表示不同的 w 值。

使用尽可能少的状态。请注意,s 输入仅在状态 A 中使用,因此您只需要考虑 w 输入。

题目网站

module top_module (

input clk,

input reset, // Synchronous reset

input s,

input w,

output z

);

parameter A=2'b00,B=2'b01,C=2'b10,D=2'b11;

reg [1:0] state,next,count;

always@(*)

begin

case(state)

A:next = s ? B : A;

B:next = C;

C:next = D;

D:next = B;

endcase

end

always@(posedge clk)

begin

if(reset)

state = A;

else

begin

if(state == A)

count = 2'b0;

else if(state == B)

count = w;

else

count = count + w;

state = next;

end

end

always@(*)

begin

z = (state == B && count == 2);

end

endmodule

自己写的在波形图不匹配,问题在于,希望在B状态进行复杂描述,反而出错。这里参考了CSDN上的一个写法。

CSDN网站

if(state == A)

count = 2'b0;

else if(state == B)

count = w;

else

count = count + w;

state = next;

这里的处理方法挺好的,是自己没有想到的,我是想用卡诺图实现,但没能成功。

浙公网安备 33010602011771号

浙公网安备 33010602011771号