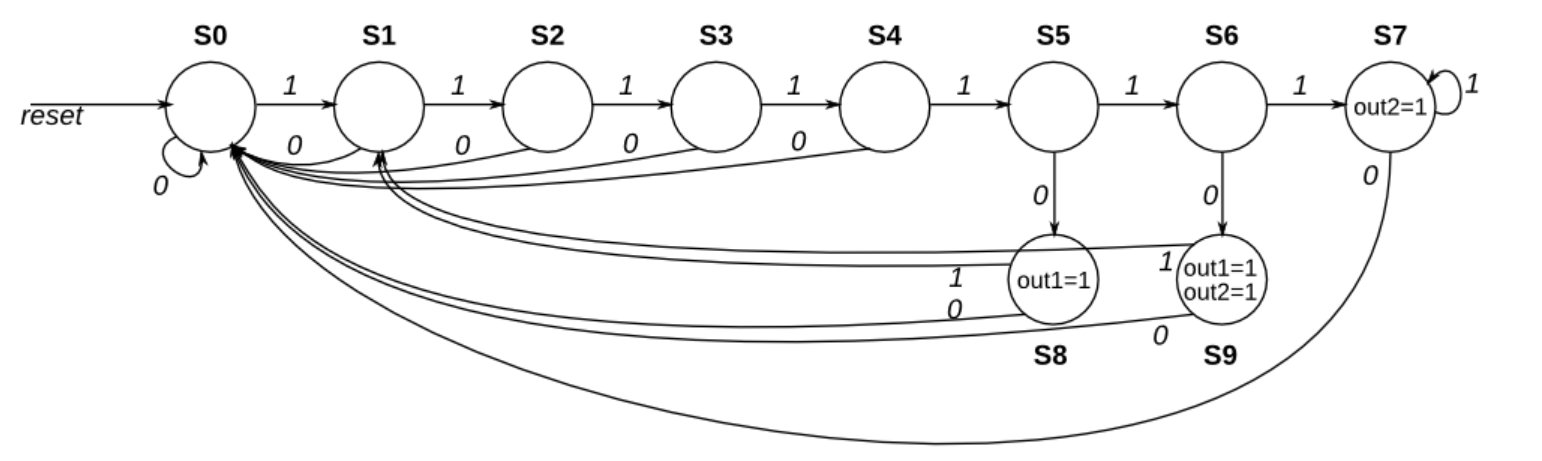

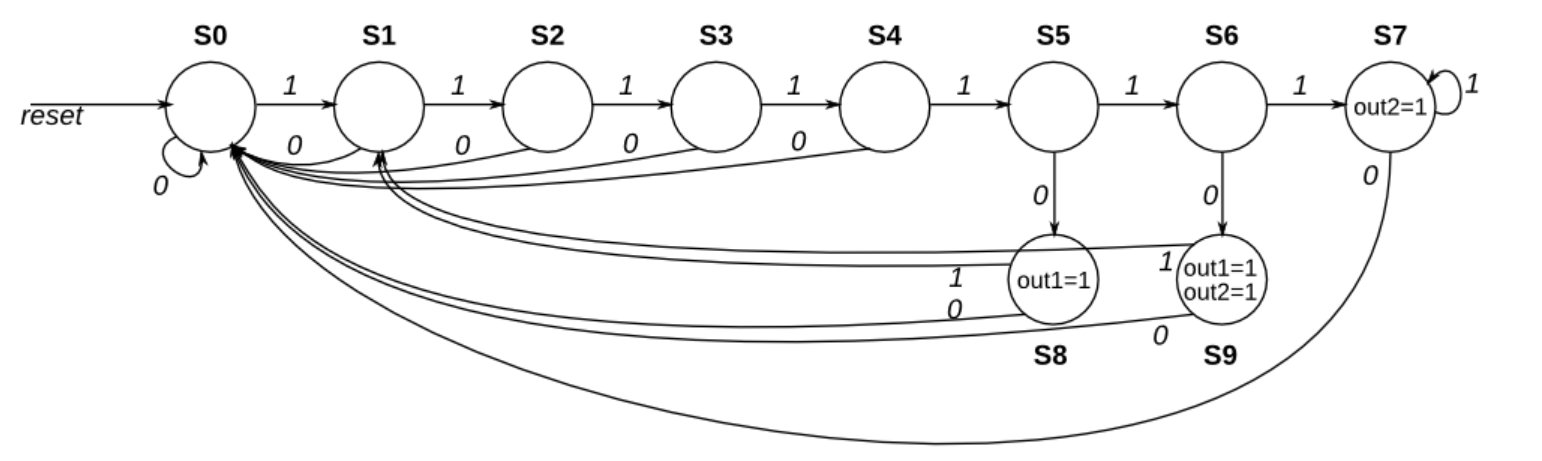

Given the following state machine with 1 input and 2 outputs:

题目网站

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

parameter s0=10'b00000_00001,

s1=10'b00000_00010,

s2=10'b00000_00100,

s3=10'b00000_01000,

s4=10'b00000_10000,

s5=10'b00001_00000,

s6=10'b00010_00000,

s7=10'b00100_00000,

s8=10'b01000_00000,

s9=10'b10000_00000;

always@(*)begin

case(state)

s0:next_state=in?s1:s0;

s1:next_state=in?s2:s0;

s2:next_state=in?s3:s0;

s3:next_state=in?s4:s0;

s4:next_state=in?s5:s0;

s5:next_state=in?s6:s8;

s6:next_state=in?s7:s9;

s7:next_state=in?s7:s0;

s8:next_state=in?s1:s0;

s9:next_state=in?s1:s0;

default:next_state=0;

endcase

end

assign out1=(state==s8||state==s9);

assign out2=(state==s9||state==s7);

endmodule

module top_module(

input in,

input [9:0] state,

output [9:0] next_state,

output out1,

output out2);

assign next_state[0]=~in&(state[0]|state[1]|state[2]|state[3]|state[4]|state[8]|state[9]|state[7]);

assign next_state[1]=in&(state[0]|state[8]|state[9]);

assign next_state[2]=in&state[1];

assign next_state[3]=in&state[2];

assign next_state[4]=in&state[3];

assign next_state[5]=in&state[4];

assign next_state[6]=in&state[5];

assign next_state[7]=in&(state[6]|state[7]);

assign next_state[8]=~in&state[5];

assign next_state[9]=~in&state[6];

assign out1=state[8]|state[9];

assign out2=state[9]|state[7];

endmodule