Counter 1-12

Design a 1-12 counter with the following inputs and outputs:

Reset Synchronous active-high reset that forces the counter to 1

Enable Set high for the counter to run

Clk Positive edge-triggered clock input

Q[3:0] The output of the counter

c_enable, c_load, c_d[3:0] Control signals going to the provided 4-bit counter, so correct operation can be verified.

You have the following components available:

the 4-bit binary counter (count4) below, which has Enable and synchronous parallel-load inputs (load has higher priority than enable). The count4 module is provided to you. Instantiate it in your circuit.

logic gates

module count4(

input clk,

input enable,

input load,

input [3:0] d,

output reg [3:0] Q

);

The c_enable, c_load, and c_d outputs are the signals that go to the internal counter's enable, load, and d inputs, respectively. Their purpose is to allow these signals to be checked for correctness.

1 module top_module (

2 input clk,

3 input reset,

4 input enable,

5 output [3:0] Q,

6 output c_enable,

7 output c_load,

8 output [3:0] c_d

9 ); //

10 assign c_enable = enable;

11 assign c_load = reset | ((Q == 4'd12) && (enable == 1'b1));

12 assign c_d = c_load ? 4'd1 : 4'd0;

13

14 count4 the_counter (clk, c_enable, c_load, c_d , Q);

15

16 //count4 the_counter (clk, c_enable, c_load, c_d /*, ... */ );

17

18 endmodule

再写:

题目翻译过来就是用一个提供的4位的二进制加法计数器,完成一个1-12的12位加法计数器

总模块与引用的二进制计数器,在端口上的关系如下:

-

使能端共用,故assign c_enable = enable;

-

(通过设置高位保持计数器运行的)c_load段,受三个的控制,第一种情况还是reset,一旦高位reset出现,c_load置零,意味停止此次计数;第二种情况是已经计数到了12,也即Q==4'd12,且使能端继续高位,将要继续计数,那么这时意味将要结束这一轮的计数,准备开始下一轮计数,故c_load置零

-

c_d的定义

很有意思的一点在于,c_d在我打错的情况下,写作assign c_d = c_load ? 4'd1 : 4'd1;,也是能够运行且不报错的。

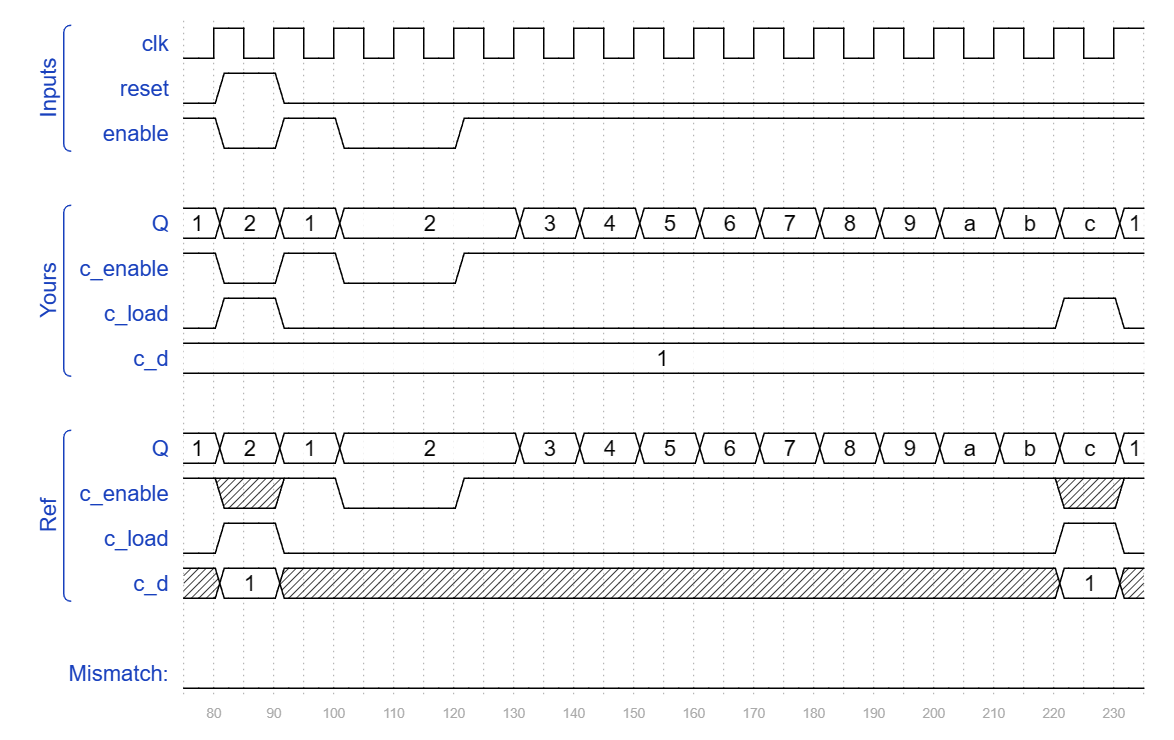

这里的不报错也仅仅是指在Hdlbits的仿真平台不报错,但是观察波形图即可发现是存在问题的,如下:

在Hdlbits平台运行最后提示Warning (13024): Output pins are stuck at VCC or GND

也就是assign c_d = c_load ? 4'd1 : 4'd1;这个语句是有问题的

自己的疑问&解答:

-

为什么定义输出的c_d,用输入的d来实例化,即

count4 the_counter (clk, c_enable, c_load, c_d , Q);?

答:当时自己没有理解,实际上是对于count4这个模块的进一步复杂,是将count4 (clk,enable,load,d,Q)中的c_load和c_d复杂,而具体怎么复杂,就是代码中的assign部分。

-

c_d有什么作用?

答:个人认为c_d作为检测信号的设置在更复杂的题目要求时有更好的用处,只不过这道题需要检测的状态比较简单,只要考虑c_load==1即可,所以代码中看起来显得有点多余。

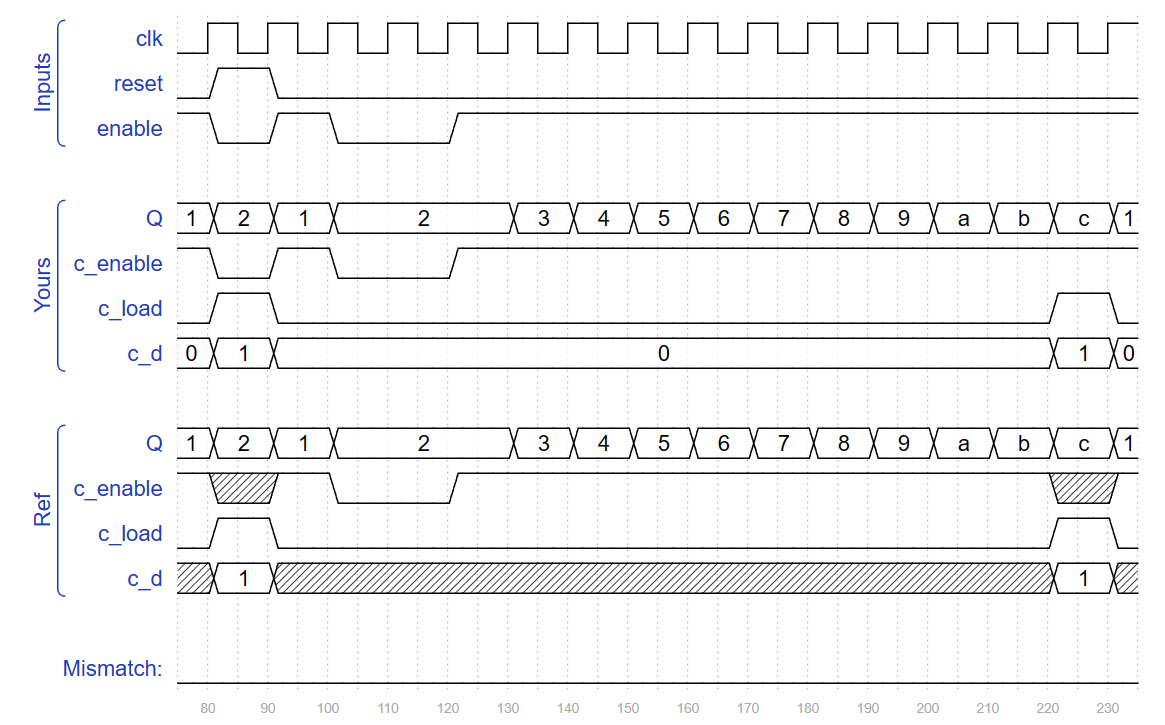

针对这道题,直接写assign c_d = c_load;都可以成功运行,波形图如下:

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理