基于SparkRoad的Hdlbits学习(4)

这篇开始More Verilog Features的学习,也是Verilog Language的最后一节。

学习:

module top_module (

input [7:0] a, b, c, d,

output [7:0] min);//

wire [7:0]m1;

wire [7:0]m2;

assign m1=(a>b)?b:a;

assign m2=(m1>c)?c:m1;

assign min=(m2>d)?d:m2;

// assign intermediate_result1 = compare? true: false;

endmodule

注意在命名m1、m2时,注意需要将其命名为[7:0],否则会报错。

ternary 三元的,三重进制的

module top_module (

input [7:0] in,

output parity);

assign parity=in[7]^in[6]^in[5]^in[4]^in[3]^in[2]^in[1]^in[0];

//assign even_bit = ^indata; 这种写法也是可以

endmodule

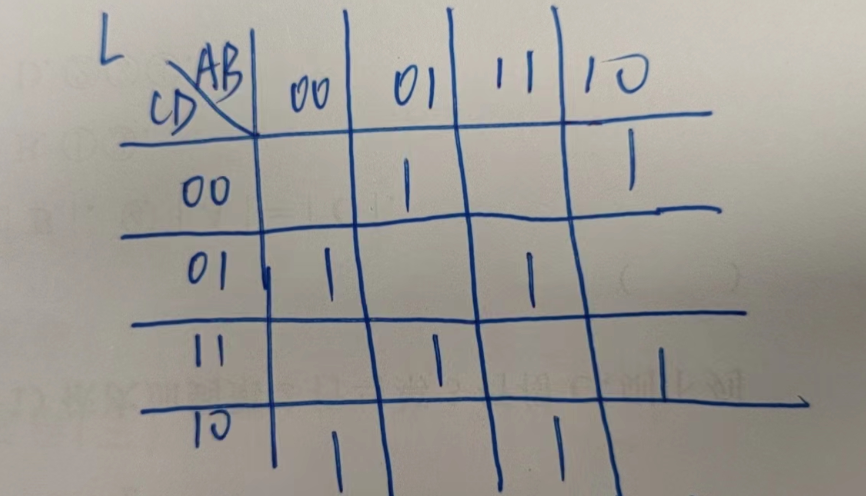

真值表如上图,这是一个很经典的真值表图。

Parity (尤指薪金或地位)平等,相同;(两个不同国家的货币单位的)平价,等价;(数字)奇偶性;(物理)宇称;(物理)宇称性;(计算机)奇偶校验;(医)经产(状况);已产子女数

Parity checking 奇偶校验

module top_module(

input [99:0] in,

output out_and,

output out_or,

output out_xor

);

assign out_and=∈

assign out_or=|in;

assign out_xor=^in;

endmodule

一种写法记住即可!非常好的写法,同上一题。

Combinational for-loop:Vector reversal 2

module top_module(

input [99:0] in,

output [99:0] out

);

integer i;

always@* begin

for(i=0;i<100;i=i+1) begin //有意思的是i++也是可以的

out[i]=in[99-i];

end

end

endmodule

这里的for循环有困惑,见《夏宇闻Verilog》P62,for语句的书写规则是:for(循环变量赋初值;循环结束条件;循环变量增量) ,那为什么循环结束条件在此题中写的是i<100?不应该是大于吗,但是写作i>99时,运行错误。所以自己理解的是,夏书再次表达的意思是for的运行适用范围。

且integer对于i的命名很重要!是很常用的。

另外,菜鸟教程中这里写的i++语法在Verilog中不成立,尝试了一下,是可以运行的。

菜鸟教程for循环

Combinational for-loop:255-bit population count

module top_module(

input [254:0] in,

output [7:0] out );

integer i;

always@*begin

out=8'b00000000;

for(i=0;i<255;i++)begin

if(in[i]==1'b1)begin

out++;

end

else

out=out;

end

end

endmodule

CSDN上别人的代码如下,对这个代码其实也有疑惑,设置这个temp是用来做什么呢?“[David说]:注意,这里会产生锁存器,做题可以,实际运用需斟酌。”另外,在CSDN作者网站上说到会产生锁存器的问题,对这个并不理解。

提出一个问题:Verilog代码什么情况下会产生锁存器?以及如何避免?

Verilog中锁存器的产生与危害

module top_module(

input [254:0] in,

output [7:0] out );

integer i;

integer temp;

always @(*) begin

out = 8'd0;

for(i=0;i<255;i++) begin

out = out + in[i];

end

end

endmodule

Generate for-loop:100-bit binary adder2

module top_module(

input [99:0] a, b,

input cin,

output [99:0] cout,

output [99:0] sum );

genvar i;

generate

for(i=0;i<100;i++)

begin:adder

if(i==0)

assign{cout[0],sum[0]}=a[0]+b[0]+cin;

else

assign{cout[i],sum[i]}=a[i]+b[i]+cout[i-1];

end

endgenerate

endmodule

通过这一题,发现自己对于“生成块”的知识掌握不牢,详见《夏宇闻Verilog》P67。虽然说这个题相对而言更好理解,待补充:生成块的进一步练习!

Generate for-loop:100-digit BCD adder2

module top_module(

input [399:0] a, b,

input cin,

output cout,

output [399:0] sum );

wire [99:0] cout_temp;

genvar i;

generate

for(i=0;i<100;i++) begin:bcd_fadd

if(i == 0)

bcd_fadd bcd_inst(a[3:0],b[3:0],cin,cout_temp[0],sum[3:0]);

else

bcd_fadd bcd_inst(a[4*i+3:4*i],b[4*i+3:4*i],cout_temp[i-1],cout_temp[i],sum[4*i+3:4*i]);

end

assign cout=cout_temp[99];

endgenerate

endmodule

这题和上一题分别涉及到具体的加法器。

CSDN上好的解释