基于SparkRoad的FPGA小程序实现(1)

题目来源:《搭建你的数字积木——数字电路与逻辑设计》第三章 3.7练习题

题目:

1.格雷码转换

实现八位二进制到格雷码的数制转换。利用FPGA验证。

实现:

module geleima_zhuanhuan(

input [7:0]erjinzhi,

output [7:0]geleima);

assign geleima[0]=erjinzhi[1]^erjinzhi[0];

assign geleima[1]=erjinzhi[2]^erjinzhi[1];

assign geleima[2]=erjinzhi[3]^erjinzhi[2];

assign geleima[3]=erjinzhi[4]^erjinzhi[3];

assign geleima[4]=erjinzhi[5]^erjinzhi[4];

assign geleima[5]=erjinzhi[6]^erjinzhi[5];

assign geleima[6]=erjinzhi[7]^erjinzhi[6];

assign geleima[7]=erjinzhi[7]; //不得不承认我这个写的有一点呆

//思考:能不能设置一个输入位数i,对于不同的i可以实现不同输入位数可以分别实现相应的转换

endmodule

引脚代码:

set_pin_assignment { erjinzhi[0] } { LOCATION = P8; }

set_pin_assignment { erjinzhi[1] } { LOCATION = N6; }

set_pin_assignment { erjinzhi[2] } { LOCATION = P6; }

set_pin_assignment { erjinzhi[3] } { LOCATION = M6; }

set_pin_assignment { erjinzhi[4] } { LOCATION = T6; }

set_pin_assignment { erjinzhi[5] } { LOCATION = T5; }

set_pin_assignment { erjinzhi[6] } { LOCATION = R5; }

set_pin_assignment { erjinzhi[7] } { LOCATION = T4; }

set_pin_assignment { geleima[0] } { LOCATION = P5; }

set_pin_assignment { geleima[1] } { LOCATION = N5; }

set_pin_assignment { geleima[2] } { LOCATION = P4; }

set_pin_assignment { geleima[3] } { LOCATION = M5; }

set_pin_assignment { geleima[4] } { LOCATION = N4; }

set_pin_assignment { geleima[5] } { LOCATION = N3; }

set_pin_assignment { geleima[6] } { LOCATION = M4; }

set_pin_assignment { geleima[7] } { LOCATION = M3; }

验证:

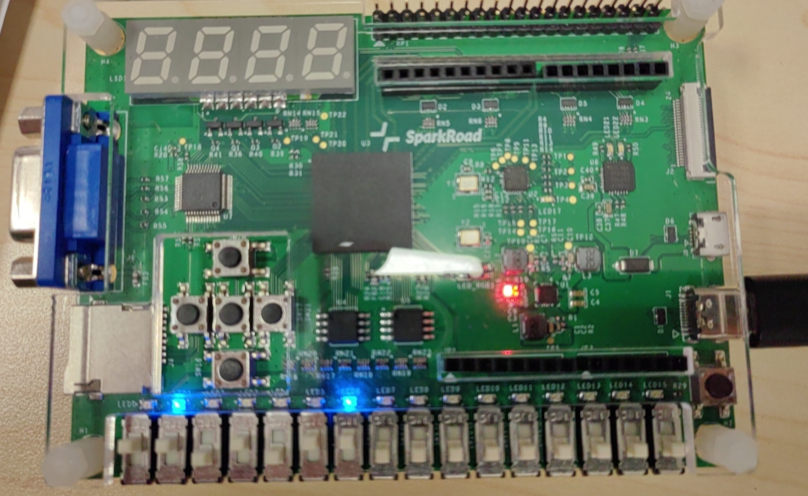

输入八位二进制11010110,输出格雷码10111101(设置中LED亮灯为0,灭灯为1)

2.双优先编码器

双优先编码器返回最高优先级和次最高优先级请求代码,输入时16位req请求信号和2位最高优先级编码信号,输出是两组4位二进制代码,分别是4位最高优先级代码请求和4位次最高优先级代码请求。

分析:

重点是理解双优选编码器的功能:

普通的优先编码器就是只对最高的输入响应,最高位无输入才对次高位进行响应,最高位、次高位都无输入才对第三高位进行响应,依次类推。。。

而双优先编码器是对输入中最高的两位进行响应,例如输入是[7:0]=01011010,第7位无输入,第6位有输入,第5位无输入……那么输出最高位为6,输出次高位为4。

考虑到输入只有1位的情况,那么该位作为最高位,次高位输出为7(在输入≥2位的情况下,次高位不可能为7)。

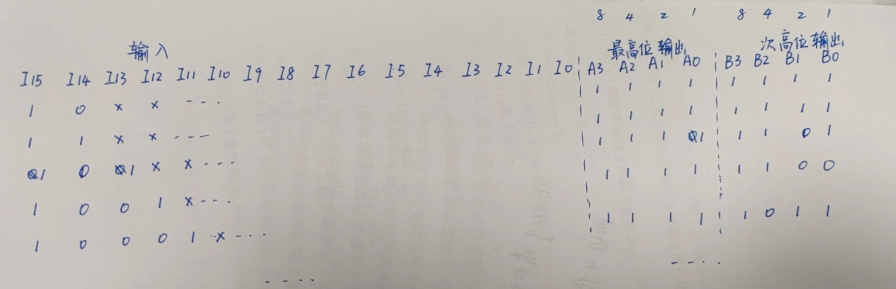

低位的双优选编码器介绍

真值表:

实现:

这一题的实现有涉及到always模块的一些写法,还需要再学习一下,待补充。

4.比较电路

使用case替换if-else语句,写出2位比较大小电路。

实现:

module bijiao(

input [1:0]bijiao_1,

input [1:0]bijiao_2,

output reg dayu,

output reg dengyu,

output reg xiaoyu

);

always@*

case ({bijiao_1,bijiao_2})

4'b0001,4'b0010,4'b0011,4'b0110,4'b0111,4'b1011:xiaoyu=1'b1;

4'b0100,4'b1000,4'b1001,4'b1100,4'b1101,4'b1110:dayu=1'b1;

4'b0000,4'b0101,4'b1010,4'b1111:dengyu=1'b1;

endcase

endmodule

引脚代码:

set_pin_assignment { bijiao_1[0] } { LOCATION = R5; }

set_pin_assignment { bijiao_1[1] } { LOCATION = T4; }

set_pin_assignment { bijiao_2[0] } { LOCATION = T6; }

set_pin_assignment { bijiao_2[1] } { LOCATION = T5; }

set_pin_assignment { dayu } { LOCATION = M3; }

set_pin_assignment { dengyu } { LOCATION = M4; }

set_pin_assignment { xiaoyu } { LOCATION = N3; }

实物验证比较简单了,就不附图了。

总结与反思:

1.对于Testbench还有一些疑惑,并没有提供tb测试文件,马上补上。

2.双优先编码器的代码,在实现部分还有不理解的地方,马上结合《夏宇闻Verilog》学习并完成。

浙公网安备 33010602011771号

浙公网安备 33010602011771号