adder

Exams/m2014 q4j - HDLBits (01xz.net)

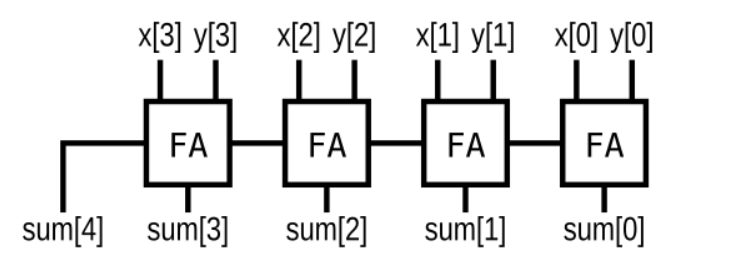

1 module top_module ( 2 input [3:0] x, 3 input [3:0] y, 4 output [4:0] sum); 5 wire [2:0] cout; //定义一个wire,即用即无,是程序内部出现的值,在之前的程序中也有这样的使用 6 assign {cout[0],sum[0]} = x[0] + y[0]; 7 assign {cout[1],sum[1]} = x[1] + y[1] + cout[0]; 8 assign {cout[2],sum[2]} = x[2] + y[2] + cout[1]; 9 assign {sum[4],sum[3]} = x[3] + y[3] + cout[2]; 10 11 endmodule

************************

2025.1.6增加

确实,Verilog 中的 `assign` 语句在某种程度上可以被视为一种较为基础和直接的赋值方式,它在概念上类似于电路中的连线。这种直接赋值的方式在硬件描述语言中是必要的,因为它直接对应于硬件电路的行为。以下是 `assign` 语句的一些特点和它在 Verilog 中的作用:

1. **连续赋值**:`assign` 用于连续赋值(continuous assignment),这意味着它会在仿真的整个过程中不断地对目标信号进行赋值。这与过程赋值(如在 `always` 块中的赋值)不同,后者只在特定条件下执行。

2. **组合逻辑**:`assign` 通常用于描述组合逻辑,即那些不依赖于时钟信号,只基于当前输入的逻辑。这与时序逻辑(sequential logic)相对,后者依赖于时钟信号和之前的状态。

3. **硬件对应**:在硬件实现中,`assign` 语句对应于无存储元素的连线或简单的逻辑门。这与需要存储元素(如触发器)的时序逻辑不同。

4. **优化潜力**:在某些情况下,`assign` 语句可以被综合工具优化掉,因为它们描述的是直接的连线或逻辑门,这在硬件中不占用额外的资源。

5. **可读性**:`assign` 语句提供了一种清晰直接的方式来描述信号之间的关系,这在阅读和理解电路设计时很有帮助。

6. **限制**:`assign` 语句不能包含条件语句或循环,这意味着它们不能用于实现复杂的逻辑或状态机。对于这些情况,需要使用 `always` 块或其他结构。

在高级编程语言中,赋值和逻辑可能被抽象化,隐藏了底层的硬件实现细节。而在 Verilog 中,`assign` 语句保留了这种硬件实现的直接性,使得设计者能够精确控制硬件的行为。这种直接性是 Verilog 作为硬件描述语言的核心特性之一,它允许设计者以一种非常接近硬件的方式描述电路。

**********

当然,让我们更详细地探讨 Verilog 中 `assign` 语句的特点:

1. **连续赋值(Continuous Assignment)**:

- `assign` 语句用于创建连续赋值,这意味着赋值操作会在仿真的整个过程中持续进行。如果输入信号发生变化,`assign` 语句会立即更新输出信号。

2. **组合逻辑(Combinational Logic)**:

- `assign` 通常用于实现组合逻辑,即输出仅依赖于当前输入的逻辑。这种逻辑不依赖于时钟信号,可以是并行或串行的,如与门、或门、非门等。

3. **硬件对应(Hardware Correspondence)**:

- 在硬件综合(synthesis)过程中,`assign` 语句通常被映射到简单的逻辑门或连线。这与时序逻辑不同,后者可能需要触发器(flip-flops)来存储状态。

4. **优化潜力(Optimization Potential)**:

- 由于 `assign` 语句描述的是直接的逻辑关系,综合工具可能会优化掉这些逻辑,如果它们在硬件中不需要额外的资源。例如,如果 `assign` 语句描述的逻辑可以通过其他逻辑门的输出直接驱动,则可能不需要额外的逻辑门。

5. **可读性(Readability)**:

- `assign` 语句提供了一种清晰和直观的方式来描述信号之间的逻辑关系。这使得代码更易于阅读和理解,尤其是在复杂的设计中,它可以帮助其他设计者或未来的你快速把握设计意图。

6. **限制(Limitations)**:

- `assign` 语句不支持条件语句(如 `if-else`)或循环结构(如 `for` 或 `while`)。这些语句用于实现更复杂的逻辑,包括状态机和时序逻辑。在这些情况下,你需要使用 `always` 块或其他 Verilog 构造来描述行为。

例如,一个简单的 `assign` 语句可能看起来像这样:

```verilog

assign output = input1 & input2; // 逻辑与操作

```

而一个使用 `always` 块的时序逻辑可能像这样:

```verilog

always @(posedge clk) begin

state <= next_state; // 在时钟上升沿更新状态

end

```

在 Verilog 中,`assign` 语句是描述组合逻辑的基础,而 `always` 块用于描述时序逻辑。这两种构造共同构成了 Verilog 编程的基础,使得设计者能够灵活地描述从简单到复杂的数字电路。

******************

非阻塞赋值(Non-blocking Assignment)在 Verilog 中是一种特殊的赋值方式,它允许在 `always` 块中并行地更新多个寄存器(`reg`)类型的变量,而不会相互干扰。这种赋值方式在模拟时序逻辑时非常重要,因为它能够更准确地反映硬件中触发器(flip-flops)的行为。

形象化地理解非阻塞赋值,可以将其类比为电子工程中的触发器,特别是 D 触发器(D flip-flop)。以下是非阻塞赋值与 D 触发器的类比:

1. **并行更新**:在时钟的上升沿,D 触发器会并行更新其输出,而不是顺序执行。这与非阻塞赋值在 `always` 块中的执行方式相似,所有非阻塞赋值在时钟边沿触发时同时计算。

2. **寄存器行为**:在数字电路中,触发器用于存储状态信息。非阻塞赋值模拟了这种寄存器行为,其中状态(输出)在时钟边沿更新,而不是立即更新。

3. **时钟驱动**:D 触发器由时钟信号驱动,其输出在时钟的特定边沿(如上升沿或下降沿)改变。非阻塞赋值同样依赖于时钟边沿来同步更新变量。

4. **数据保持**:在时钟边沿到来之前,D 触发器的输出保持不变。非阻塞赋值在 `always` 块中也保持这种特性,即在时钟边沿到来之前,赋值表达式被计算,但实际的赋值操作在边沿同步执行。

例如,非阻塞赋值可以这样使用:

```verilog

always @(posedge clk) begin

reg1 <= expression1; // 非阻塞赋值

reg2 <= expression2; // 非阻塞赋值

end

```

在这个例子中,`reg1` 和 `reg2` 的值会在时钟 `clk` 的上升沿同时更新,这与 D 触发器的行为相似,后者在时钟边沿捕获输入 D 的值,并在下一个时钟周期将其输出到 Q。

总的来说,非阻塞赋值在 Verilog 中用于模拟时序逻辑,它的行为与硬件中的触发器非常相似,这些触发器是构成时序电路的基本存储单元。

*******************

触发器(Flip-Flop)和寄存器(Register)是数字电路和计算机硬件中的基本概念,它们在存储和处理数据方面起着关键作用。让我们形象化地解释这两个概念:

1. **触发器(Flip-Flop)**:

- 触发器是一种具有两个稳定状态的电路,可以被视为一个单比特(bit)的存储单元。这两个状态通常被称为“1”和“0”。

- 形象化地理解,触发器就像是一个开关,可以处于两种状态之一:开(1)或关(0)。

- 触发器由一个或多个逻辑门组成,这些逻辑门控制开关的状态。在数字电路中,触发器通常由时钟信号控制,这意味着它们的状态变化与时钟信号的边沿(上升沿或下降沿)同步。

- 触发器是构成更复杂存储设备的基本单元,如寄存器和计数器。

2. **寄存器(Register)**:

- 寄存器是由多个触发器组成的,用于存储一定数量的比特。例如,一个8位寄存器可以存储一个8位二进制数。

- 形象化地理解,寄存器就像一排开关,每个开关代表一个比特。这排开关可以同时被打开或关闭,从而存储一个数值或数据字。

- 寄存器通常包含额外的控制逻辑,用于决定何时读取或写入数据。这可能包括使能(enable)信号,它控制寄存器是否应该更新其状态。

- 寄存器在计算机中用于存储指令、数据和处理过程中的中间结果。它们是CPU、内存和其他数字系统中不可或缺的部分。

**形象化的比喻**:

- 将触发器比作一个简单的开关,它可以通过时钟信号来控制开或关。

- 将寄存器比作一排可以同时操作的开关,每个开关代表一个比特,整个排可以存储一个数字或字符。

在实际的硬件实现中,触发器和寄存器由晶体管和其他电子元件构成,它们的状态由电压水平表示,而不是物理的“开”或“关”。触发器和寄存器的设计允许它们在没有电源的情况下保持状态,这是静态随机存取存储器(SRAM)的一个关键特性。对于动态随机存取存储器(DRAM),需要周期性地刷新电荷以保持数据,因为电荷会随时间泄漏。

浙公网安备 33010602011771号

浙公网安备 33010602011771号