Ethernet 介绍与TI CPSW debug

Overview

-

Atchiteccutre

![]()

-

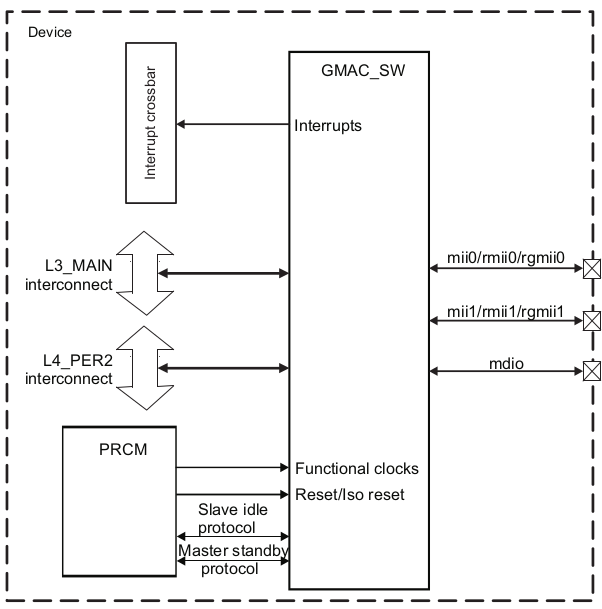

GMAC Overview

![]()

-

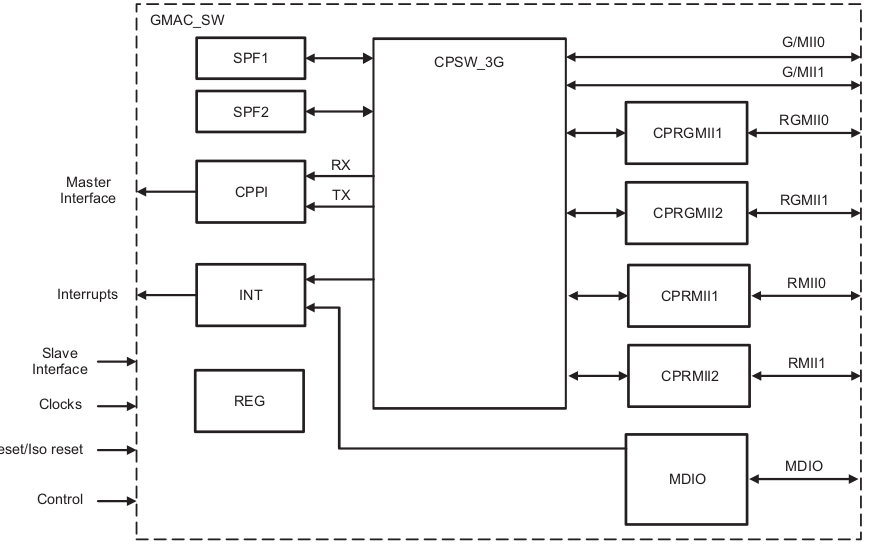

GMAC top level block diagram

![]()

-

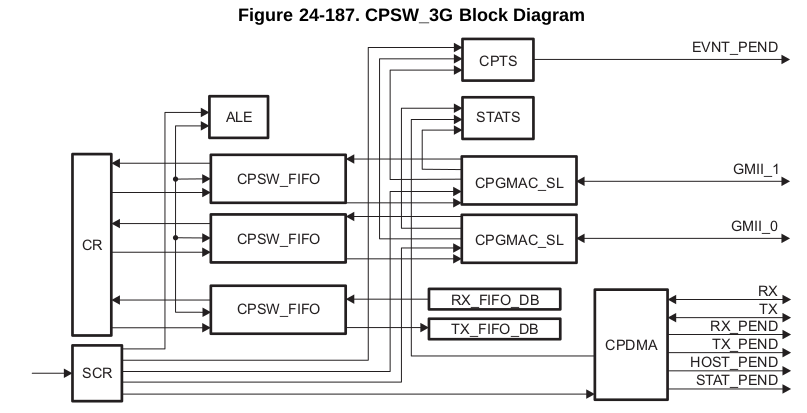

CPSW 3G

![]()

Feature:

- Two thernet ports(Port0 and port1)

- QOS support (Quality of Service)

- CPPI 3.1 compliant DMA controllers

- Support for Audio/Video Briding

- Flow Control support

- ADDress loopup engine(ALE)

- VLAN support

- 8k (2048 × 32) internal CPPI buffer descriptor memory

- Management Data Input/Output (MDIO) module for PHY Management

The GMAC_SW subsystem consists of:

- CPSW_3G which contains two G/MII interfaces

- Two RGMII interface modules

- Two RMII interface modules

- One MDIO interface module

- One Interrupt Controller module

- One CPPI interface

- Local CPPI memory of size 8 KiB

- Two Static Packet Filter

The CPSW subsystem consists of:

- CPGMAC_SL interfaces (ports 1 and 2)

- one CPPI interface Host Port (port0)

- Common Platform Time Sync (CPTS)

- ALE Engine

- CPDMA

CPSW

introduction

3口的以太网子系统。它提供以太网包通信,并且可以配置成以太网交换机,提供GMII,RGMII,RMII,MDIO物理接口。这个设备包含一个3口的千兆以太网交换机子系统CPSW_3GSS_RG,它提供两个外部的以太网接口port1和port2,和一个内部的支持IEEE 1588v2 and 802.1ae的接口port0。

接收Packet完成脉冲中断RX_PULSE

- 八通道,RX_PEND [7:0] interrupts.置一相应的位RX_INTMASK_SET,Cn_RX_EN,被屏蔽的可以从Cn_RX_STAT得到中断通过子系统写packet的最后一个buffer描述符地址到通道队列的接收完成指针地址。

- 中断接收到后,cpu需要写自己处理的最后一个buffer描述符到通道队列的接收完成指针地址RXn_CP来应答中断。软件需要做如下操作。读RX_STAT寄存器,确定那个通道发的中断。

- 处理接收到的packets。写3PSW completion pointer(s) (RXn_CP).软件写的值会和子系统写的值相比较,如果不相等,则意味着,软件没有把所有的buffer处理完,这个中断会一直保持触发状态。通过读RXn_CP,可以知道子系统写的值。

- CPDMA_EOI_VECTOR寄存器写1.

取消中断如下:写一到RX_INTMASK_CLEAR,RX_EN清零

发送Packet完成脉冲中断TX_PULSE

与接收类似

cpsw_3g

它包含两个

- CPGMAC_SL 接口(ports 1 and 2),

- 一个CPPI 3.0接口(port 0),

- 通用平台时间对时cpts

- ale engine(adress lookup engine)

- cpdma

CPDMA RX and TX 接口

CPDMA 子模块是cppi3.0协议的dma packets传输控制器,他是port0。主控写 STATERAM块里面的 发送通道头描述符指针地址 来初始化发送操作。这样发送dma控制器会从packet链里面取出packet发送到外部的发送fifo里面去,64字节最大一次。

接收差不多

-

CPPI Buffer 描述符: 描述符用来描述一个buffer的信息,并且描述符是链表形式连接在一起的。

8K的cppi ram 地址从0x4a102000到0x4a103FFF。

-

TX Buffer 描述符: Next Descriptor Pointer下一描述符指针,标识下一个描述符的地址。主控设置,emac不会设置。一旦加入了发送queue,不要改,除非这个值为NULL,并且有新的描述符要添加到它的后面。如果在添加之前,emc就已经处理完了NULL的描述符(读EOQ标识),则需要重新启动发送。

-

to_port:发送到哪个port上去,sop有效 但是ale查询会执行 用来确定没有标签的出口 在VLAN_AWARE模式

-

TO_PORT_ENABLE: sop 有效,只送往一个port

-

PACKET LENGTH: 所有的packet 的有效长度,SOP有效,如果长度不对会触发错误中断。

-

RX Buffer Descriptors: rx_vlan_encap 置一表明,这个packet有32bit的vlan头。被CPSW control register rx_vlan_encap bit控制

VLAN Aware Mode

CPSW Control register的 vlan_aware bit 置一。

port0从cpsw_3g接收的packets也许是或者不是vlan封装的,决定于CPSW Control register的 rx_vlan_encap bit.

port0接收的数据不会更改。vlan封装数据有个32位的头加在包的数据上。从packet描述符中的 rx_vlan_encap判断。

port0不能发送vlan封装的包。

这种模式下,发送packet的数据会根据头改变。

Address loopup Engine(ALE)

- 判据: 接收port/目的地址/源地址/长度和类型/vlan信息。

- 使能:ale_enable bit in ale_control寄存器, 不使能,所用packet都会丢弃。正常情况下,cpgmac_sl会把异常数据packet丢弃,除非设置了cef, csf, or cmf,这样只送往port0.

- 学习: 基于源地址,查找基于目的地址。

- 在bypass模式下,ale_bypass bit in the ALE_Control寄存器。cpgmac_sl接收的数据只会送往port0,CPDMA_Rx_Ch_Map register.使得packet从不同通道发送。

- port0 在发送的时候需要制定发送port号。

- 在oui禁止模式,enable_oui_deny bit in the ALE_Control寄存器。oui源地址不匹配,packet被丢弃,除非目的地址匹配广播条目且super bit置位。单播地址 地址有条目且block 和 secure bit置位,以上是所谓Supervisory packets。

Debug

-

confirm the MDIO hardware connecting and clk

-

check the alive register

-

check the link state

浙公网安备 33010602011771号

浙公网安备 33010602011771号