SystemVerilog 语言部分(二)

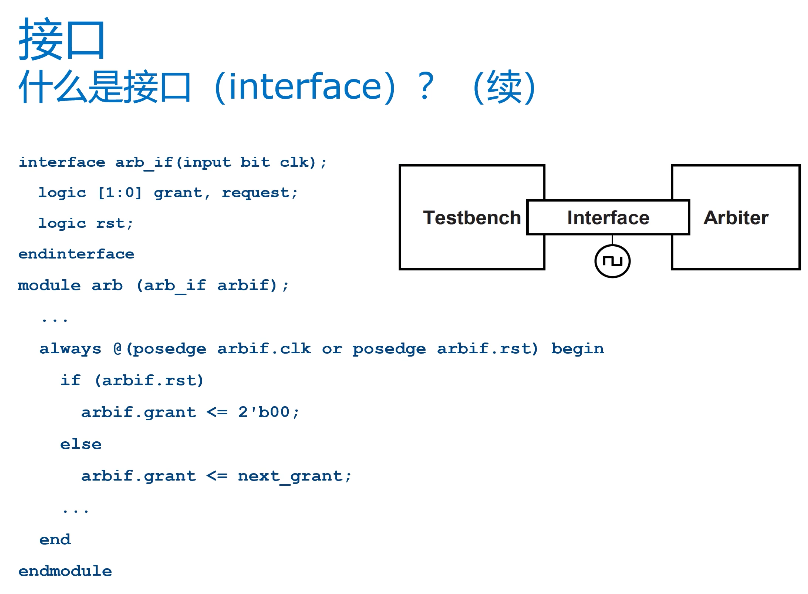

接口interface:

既可以设计,也可以用来验证。

验证环境:interface使得连接变得简单不容易出错。

interface可以定义端口,单双向信号,内控部使用initial always task function

interface 可以在硬件环境和软件环境中传递。也可以作为软件方法的形式参数

可以把interface看做“插排”。

testbench<--->interface<----->arbiter

通过interface name+ . +logic

通过$finish在testbench结束仿真。

在interface的端口列表之中只需要定义:时钟,复位等公共信号,或者不定义任何端口信号,转而在变量列表中定义哥哥需要跟DUT和TB连接的logic的变量。为了简单易用,推荐使用logic的定义变量。

interface也可以进行参数化

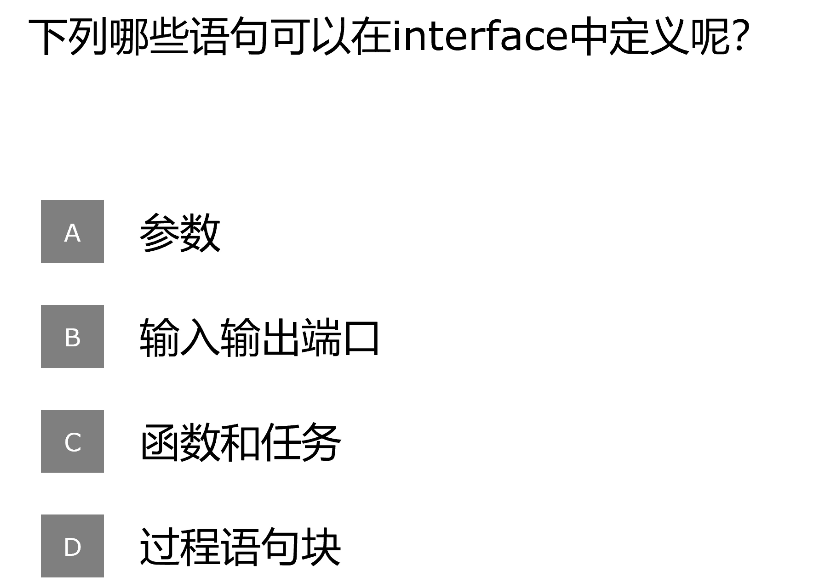

习题:

答案:ABCD

module中可以例化module,interface

interface可以例化interface,但是不能例化module。

2.采样和数据驱动

RTL的竞争解决方法:

1.使用非阻塞赋值语句

2.信号进行延迟来解决同步的问题

阻塞赋值,在上例中 a 被设计为4个寄存器,但是 b = a 在同一拍子中b被设计成导线的形式,不是寄存器的形式。

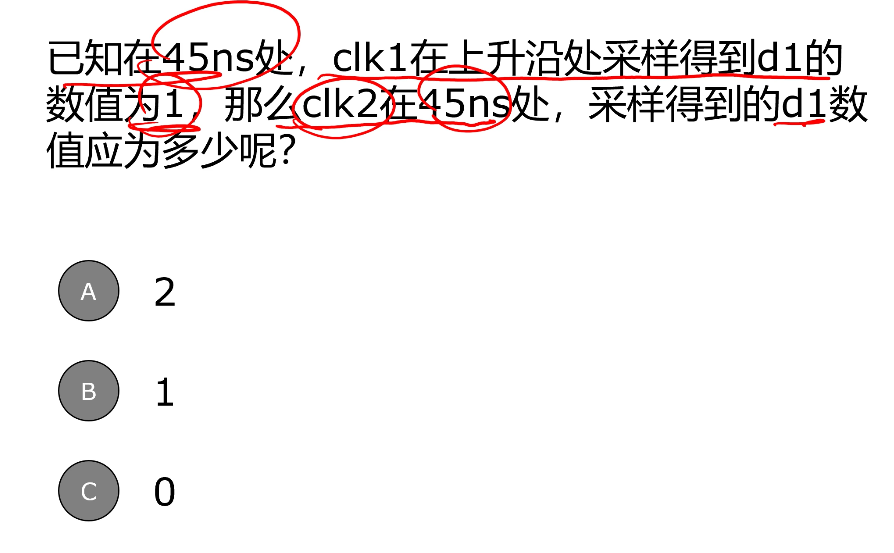

在进行仿真时候为了避免时序电路中时钟和驱动信号的时序竞争问题,我们需要给出尽量明确的驱动时序和采样时序。

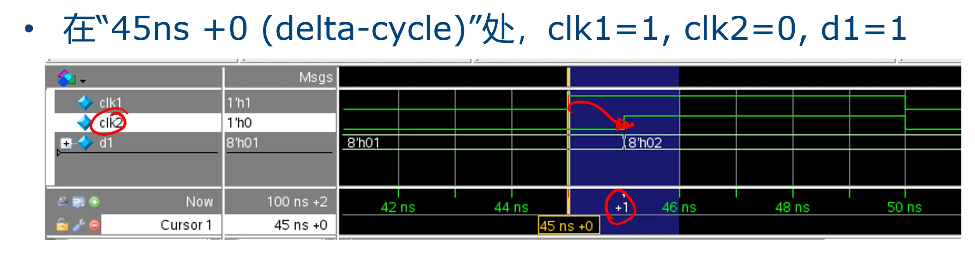

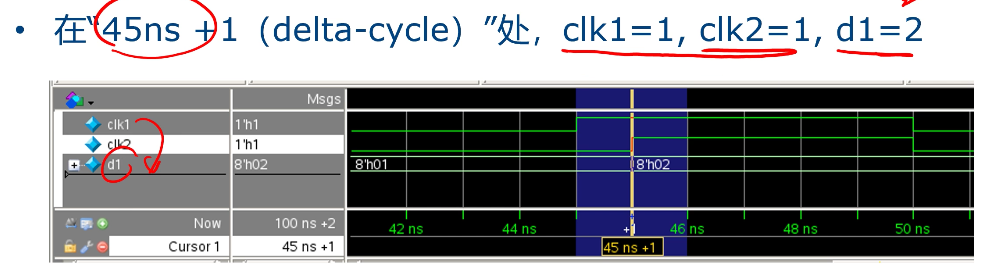

默认情况下时钟对于组合电路的 驱动会添加一个无限小的delta-cycle,而且该延迟无法用绝对实践单位衡量,它要比最小的时间单位精度还小。

一个时间片:time-slot 可以发生很多事

在仿真时候run0,让仿真器跑一个delta-cycle的时间。

竞争的问题:

timescale 1ns/1ns

module race1;

bit clk1,clk2;

bit rstn;

logic[7:0] d1;

initial begin//generate clk1

forever #5 clk1< = ~clk1;

end

//clk2 generate

always@(clk1)

clk2<=clk1;//即使clk2与1完全同步,但是也有delt-delay

initial begin

#10 rstn <=0;

#20 rstn<=1;

end

//mini counter

always@(posedge clk1,negedge rstn)begin

if(!rstn)

d1<=0;

else

d1<=d1+1;

end

//clk1,2POSedge print data d1

always@(posedge clk1)

$display("%0t ns d1 value is 0x%0x",$time,d1);

always@(posedge clk2)

$display("%0t ns d1 value is 0x%0x",$time ,d1);

endmodule

NB的题,这里应该是A.2

使用打印的数据比用仿真观察波形得到的数据要准确。

如何避免采样的竞争问题?

(1)在驱动时,添加相应的人为延迟。模拟真实的延迟

同时加大clk与变量之间的延迟,提高DUT使用信号时的准确度和TB

采样信号时的可靠性。

(2)在采样时间前的某时段中进行采样。