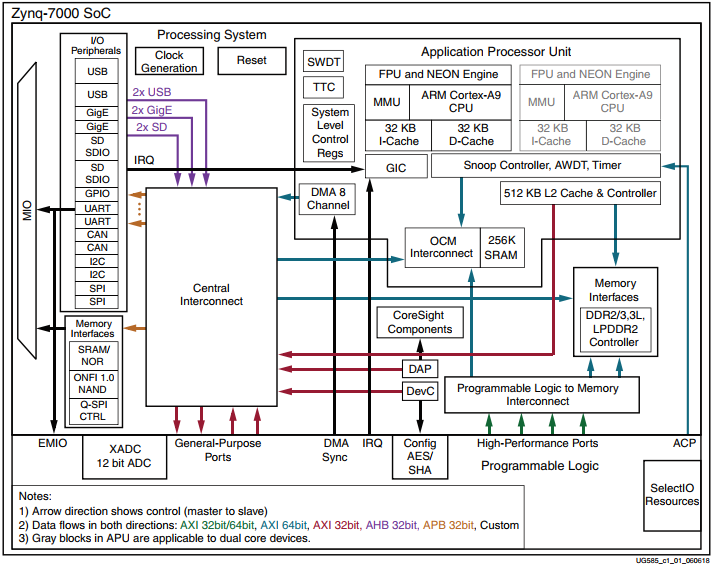

Xilinx ZYNQ-7000系列PSOC芯片分析

Xilinx创造性地将PS(Process System)和PL(Programable Logic)集成到一块芯片中,推出ZYNQ-7000系列可编程SoC,它们使用相同的PS核,区别在于PL部分的硬件资源。官方推荐使用ISE开发工具。

PS和PL各自使用独立的电源,PS-PL之间的内部互联采用CoreLink Network Interconnect(NIC-301)技术。

PL源自Xilinx 7系列FPGA,如Artix-7和Kintex-7,集成了不同的硬件资源:

UG474: Configurable Logic Blocks(CLBs)

UG473: Port and Width Configurable Block RAM(BRAM)

UG479: DSP slices with a 25x18 multiplier, 48bit accumulator and pre-adder(DSP48E1)

UG480: User Configurable analog to digital convertor(XADC)

UG472: Clock Mgmt tiles(CMT)

Configurable Block with 256b AES for decryption and SHA for authentication

UG471: Configurable SelectIO technology

UG482 & UG476: Optionally GTP or GTX multi-gigabit transceivers

PG054: PCIe Block

PS特性

| 资源 | 全称 | 说明 |

| SLCRs | System-Level Control Registers | 配置PS行为 |

| SCU | Snoop Control Unit | 保持L1和L2的Cache一致性 |

| ACP | Accelerator Coherency Port |

PL(master) to PS(slave) 64b AXI slave port 可以访问L2和OCM |

| OCM | On-Chip Memory |

256KB, Dual Ported 可以被CPUs, PL和中央互联单元访问 |

| DMA | Direct Memory Access | PS使用4个通道,PL使用4个通道 |

| GIC | General Interrupt Controller | 20 from the PL |

| PS MIO I/Os |

分属两个电源域: PIN[15:0]属于Bank 0 Voltage PIN[53:16]属于Bank 1 Voltage |

PS-PL互联

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· winform 绘制太阳,地球,月球 运作规律

· 震惊!C++程序真的从main开始吗?99%的程序员都答错了

· AI与.NET技术实操系列(五):向量存储与相似性搜索在 .NET 中的实现

· 【硬核科普】Trae如何「偷看」你的代码?零基础破解AI编程运行原理

· 超详细:普通电脑也行Windows部署deepseek R1训练数据并当服务器共享给他人