10GbE以太网MAC和PHY

10GbE以太网MAC和PHY

概述

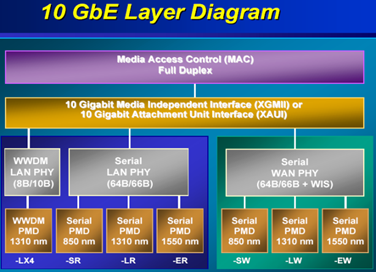

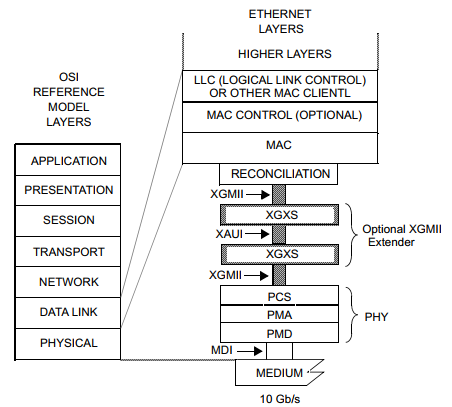

10GbE以太网遵循IEEE 802.3ae规范,其物理传输介质只支持光纤。

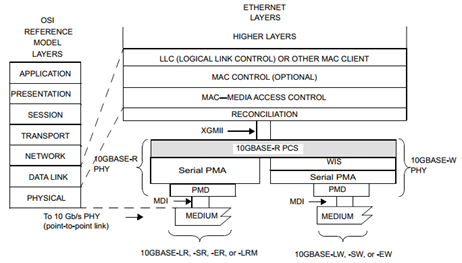

10GbE以太网主要分为串行的10GBase-S/L/E-R/W与并行(4路并行WDM波分复用)的10GBase-LX4两类。

10GBase-S/L/E-R/W中,S/L/E表示波长,S表示850nm短波,L表示1310nm长波,E表示1550nm超长波,不同波长有效传输距离不一样;R/W表示PHY类型,R表示LAN PHY,即局域网物理层,码率为10.3125Gb/s,W表示WAN PHY,即广域网物理层,码率为9.95328Gb/s。

串行10GBase-R/W使用64B/66B编码,而并行10GBase-LX4沿用千兆以太网的8B/10B编码。通过64B/66B编码,10Gb/s会变成10.3125Gb/s,所以10GBase-R的码率为10.3125Gb/s。但是10GBase-W要与SONET/SDH无缝兼容,所以在10GBase-W的物理层增加了WIS(WAN Interface Sublayer)子层,其主要功能是将10GbE LAN应用中的Idle码去掉,使速率降到9.95328Gb/s,与SDH VC-4-64c和STS-192c兼容。

名词解释

MAC Media Access Controller 媒介访问控制器

PHY Physical 物理层

PCS Physical Coding Sublayer 物理编码子层

PMA Physical Media Attach 物理附加子层

PMD Physical Media Dependent 物理依赖子层

XGXS XGMII Extender Sublayer XGMII扩展子层

XAUI 10 Gigabit Attachment Unit Interface 一种10G以太网接口

CDR Clock Data Recovery 数据时钟恢复

pre-emphasis 预加重技术

offset cancellation 失调消除技术

MII Media Independent Interface

RS Reconciliation Sublayer 协调子层

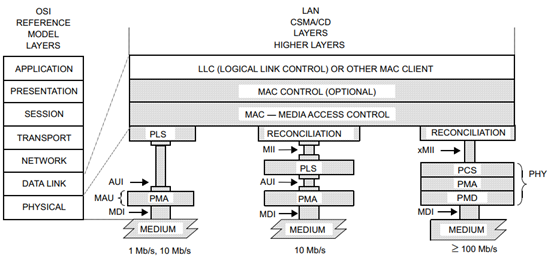

MAC

数据链路层包括LLC子层、MAC Control子层(可选)、MAC子层和RS子层。MAC层主要负责控制与连接物理层的物理介质。在发送数据时,MAC协议事先判断是否可以发送数据,如果可以发送,将给数据添加一些控制信息,最终将数据以及控制信息以规定的格式发送到物理层;在接收数据时,MAC协议首先判断输入的信息是否发生传输错误,如果没有错误,则去掉控制信息发送至LLC层。

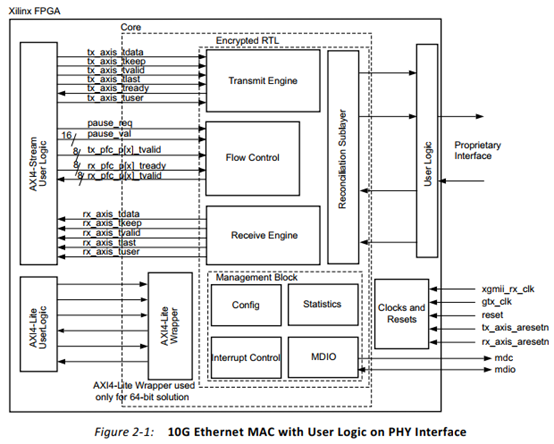

上图是10GE MAC的内部实现框图,主要包括Transmit Engine、Receive Engine、Flow Control、RS、管理模块和时钟&复位模块。其中Transmit Engine和Receive Engine主要是两个FIFO缓冲区,用来缓存发送和接收的数据。Flow Control指流控制,因为实际通信过程中,双方的处理速度不一致,这样可能出现MAC接收缓冲区满的情况,如果此时继续接收报文,则接收到的报文会被直接丢弃,Flow Control就是针对这种情况,当接收缓冲区报文达到阈值时,发送PAUSE帧或者PFC帧,告知对端MAC停止发送报文。Statistics模块则进行报文统计。

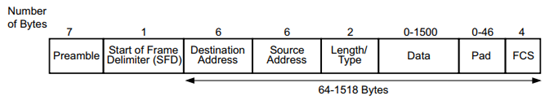

以太网帧

标准数据帧

802.1Q数据帧

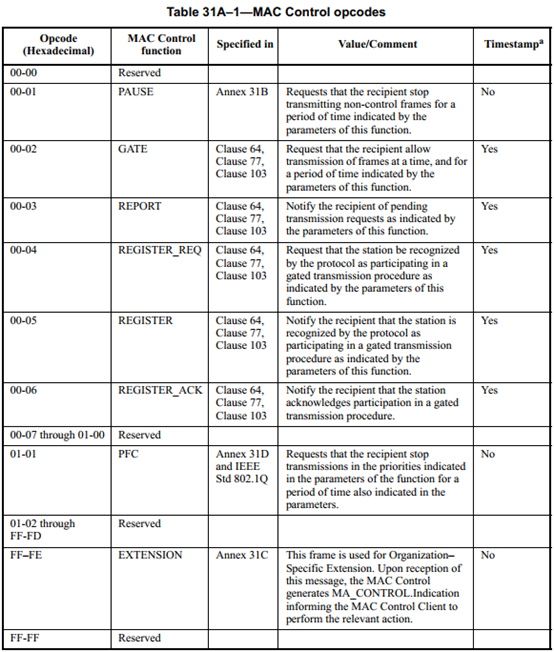

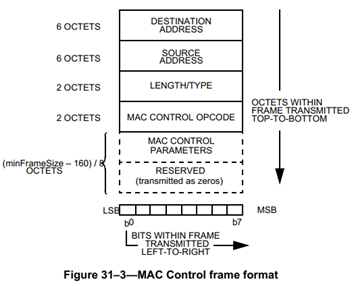

MAC Control

MAC Control帧格式如上图,其中,目的MAC是一个特定的地址,Type字段为0x8808,MAC Control Opcode决定了MAC Control帧的类型。

PAUSE帧和PFC帧是MAC层Flow Control的基础。

PAUSE帧的目的MAC固定为01-80-C2-00-00-01,它的作用是当接收FIFO达到阈值时,告诉对端MAC停止发送报文。PAUSE帧的参数表示停止发送报文的时间间隙,当对端MAC接收到PAUSE帧之后,会在时间间隙结束之后继续发送报文;如果在时间间隙结束之前接收到参数为0的PAUSE帧,则表示可以立即发送报文。

PFC(Priority-based Flow Control)帧则是根据802.1Q VLAN TAG的COS值,依据优先级进行流控。PFC帧的目的MAC也是01-80-C2-00-00-01。

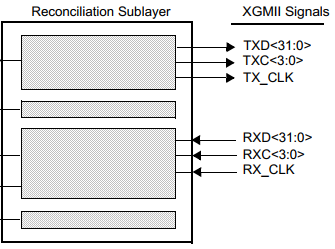

RS

协调子层主要是使不同物理介质对MAC子层透明,即把各种MII接口的数据,以统一的方式和MAC层传输。

MII

MII接口是MAC和PHY之间的接口,有MII/RMII/SMII/SSMII/GMII/SGMII/XGMII等,由MII接口转换而来的以太网背板接口有XAUI/10G-KR4等。

XGMII

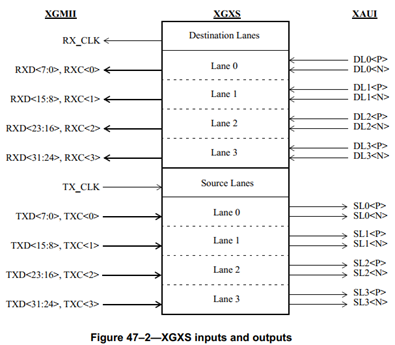

XGMII总线(IEEE 802.3 Clause 46)有发送和接收两个相互独立的通道,每个通道有一根参考时钟信号、4根数据同步信号(每个同步信号控制1个Lane的数据同步)、32根数据传输信号(分为4个Lane),一共74根信号线。

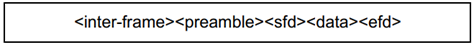

XGMII码流格式如上图,由帧间隙(IFG)、帧前导码(Preamble)、帧开始定界符(SFD)、帧数据(DATA)和帧结束定界符(EFD)构成。

帧间隙从Terminate控制符开始,到Start控制符结束,帧间隙过程中传输Idle控制帧。帧间隙的时长以字节为单位,帧间隙最小值根据双方MAC实现确定,10GBASE-R应用场景,最小帧间隙(IPG)为5个字节。

帧前导码是7个连续的0xAA。

帧开始定界符必须通过XGMII Lane 0传输,一个字节0xAB。(此处与下表中的Start控制符不一致,待商榷)

帧结束定界符,可以出现在XGMII的任意Lane,其值不详。

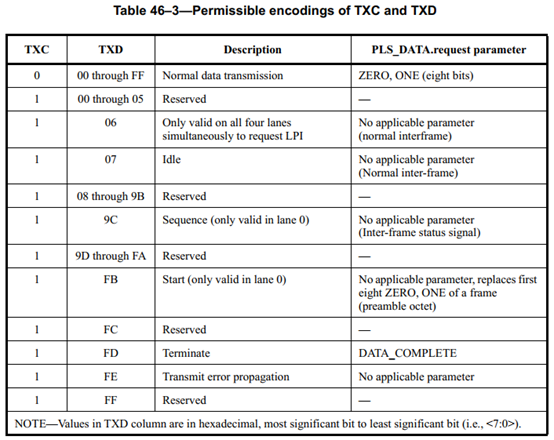

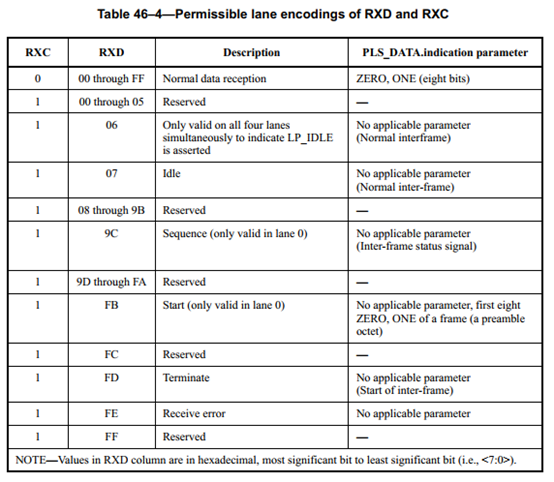

TXC为低电平时,表示传输数据帧;TXC为高电平时,表示传输控制帧。

RXC为低电平时,表示传输数据帧;RXC为高电平时,表示传输控制帧。

XGXS & XAUI

XGXS包括位于RS侧的DTE XGXS和PHY侧的PHY XGXS两部分。XGXS子层(IEEE 802.3 Clause 47)的出现有两个原因:

1) XGMII接口是并行接口,一共有74根信号线,XGXS将XGMII接口转为XAUI接口,串行化(4 Lane共16根信号线);

2) XGMII接口总线的布线长度小于7cm,无法支持二层以太网交换机跨板(通过背板)通信,经过XGXS转换的XAUI接口则支持最长50cm的布线长度;

发送方向,XGXS接收XGMII的数据,将XGMII数据帧和控制帧转换成XAUI码流(code-groups),编码之后传输。接收方向,首先解码XAUI码流,补偿时钟和相位,转换成XGMII数据帧和控制帧,然后传输。

PHY

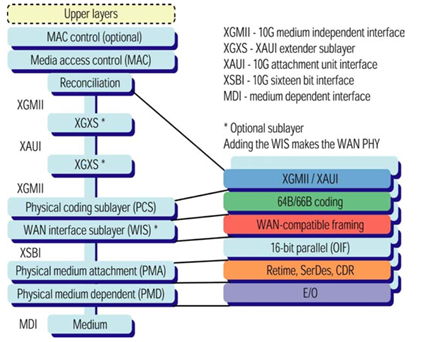

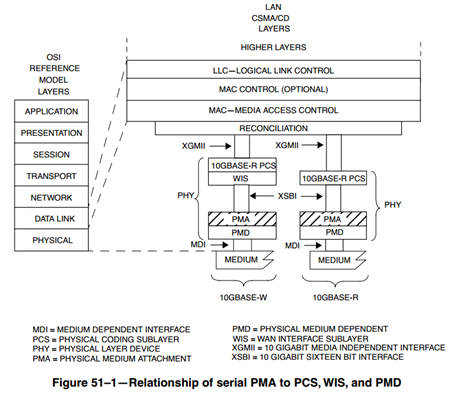

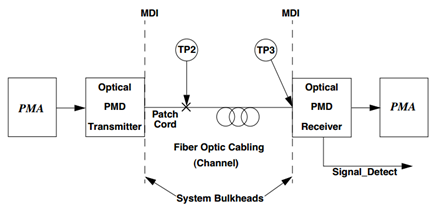

PHY层包括PCS子层、PMA子层和PMD子层。

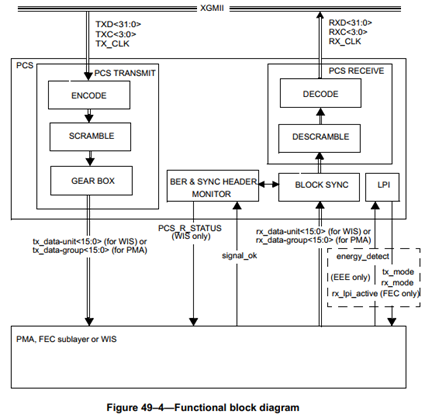

PCS

PCS层面向的业务接口是XGMII, XGMII是所有10Gb/s PHY针对RS层或者XGXS层提供的统一接口。

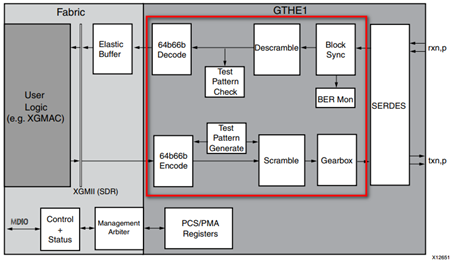

上图是一个典型的10GBase-R PHY的IP核内部结构体,红色框图部分是PCS实现。其中,64B/66B Encode/Decode负责编解码、Test Pattern Generate/Test Pattern Check负责发送和校验测试报文(PHY硬件自检)、Scramble/Descramble负责加解扰、Gearbox(变速箱)和Block Sync负责速率匹配和时钟、相位补偿、字对齐等功能、BER Mon(Bit Error Rate Monitor)负责监控误码率。

加解扰技术是一种调制技术,其原理是将扰码与原始信号相乘,从而得到新的信号,与原始信号相比,新信号在时间和频率上被打散。

PCS层发送方向和接收方向都可以工作在正常模式(Normal mode)和测试模式(Test-Pattern mode)。当处于测试模式时,Test Pattern Generate/Check使能。

PCS层Gearbox模块负责将发送方向的数据分组成16位一组的数据单元,通过XSBI接口发送给PMA层。

编解码的目的有两个:

1)避免物理传输介质上出现连续的1或者0,如64B/66B编码将64位数据编码成66位数据在传输介质上传输,从而降低信噪比;

2)区分出数据和命令。

此外,PCS层还负责PHY自协商,PHY自协商可以自动匹配工作模式、工作速率等。

64B/66B

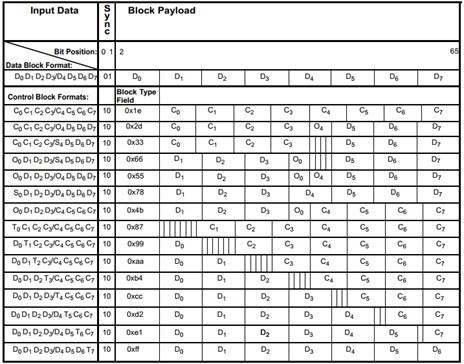

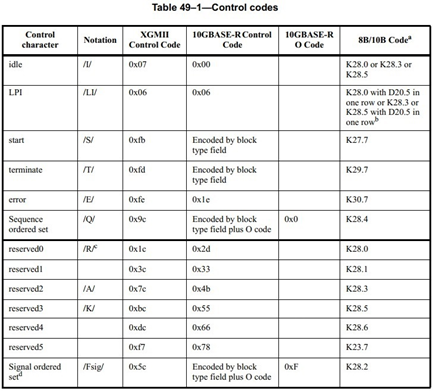

10GBase-R的PCS层使用64B/66B编码(IEEE802.3 Clause 49),支持数据帧和控制帧,同时拥有健全的错误检测机制。

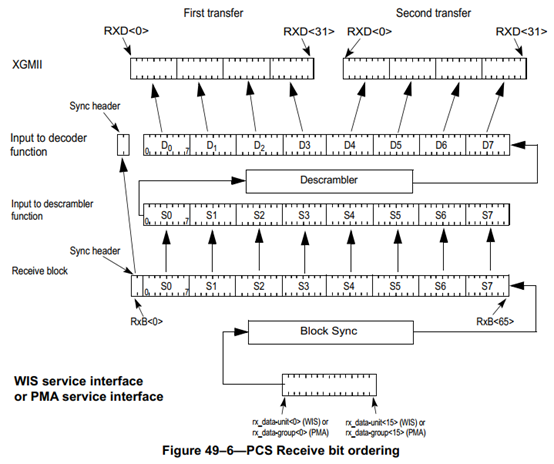

发送方向,PCS从XGMII接收两组32位数据,一共64位数据。然后添加2位同步头(根据XGMII的TXC信号决定),01表示数据帧,10表示控制帧。同步头不通过Scrambler模块加扰码,因为如果同步头被改变,就无法区分数据帧和控制帧,也无法进行帧定界。

在接收方向,PCS从接收到的66位数据块中提取出同步头,负载部分进行解扰码和64B/66B解码,然后把解码出来的数据通过XGMII接口发送给XGXS层或者RS层。

PCS层无论是对接RS层还是XGXS层,都是通过XGMII接口。XGMII接口在发送和接收方向都有32根数据线,通过TXC[3:0]和RXC[3:0]进行数据同步,每个TXC/RXC信号控制8根数据线。

64B/66B编码中,数据帧和控制帧除了同步头之外的负载部分,均包含8个字节。对于数据帧而言,负载各字节命名为D0~D7。控制帧负载的8个字节,除了Ordered Set(/O/)字符、Start(/S/)字符和Terminate(/T/)字符之外,命名为C0~C7。Ordered Set字符只能由XGMII的第一个Lane发送,因此命名为O0或者O4;Start字符同样只能由XGMII的第一个Lane发送,因此命名为S0或者S4;Terminate字符则可以出现在任意字节,因此命名为T0~T7。

对于控制帧而言,进行64B/66B之后,除同步头之外的负载部分第一个字节称为Block Type域,用来区分控制帧类型。对于包含Start字符或者Terminate字符的控制帧,Block Type域指示了它的类型。其他控制字符被编码为7位的控制码(Control Code)或者4位的O码(Ordered Set Code)。

Control Codes

Idle(/I/)

从XGMII接收到Idle控制字符(0x07)时,PCS会根据当前数据传输忙或者闲,动态地插入或者删除Idle字符,从而调整时钟频率。/I/字符的插入和删除需要4个一组,/I/字符只能出现在/I/或者/O/之后。数据接收过程中,不能插入/I/字符。删除/I/时,紧跟着/T/的四个/I/不能被删除。

LPI(/LI/)

/LI/字符的插入和删除原则同/I/字符。

Start(/S/)

Start字符表示开始发送报文。

Terminate(/T/)

Terminate字符表示发送报文结束。

Ordered Set(/O/)

/O/字符表示开始发送Ordered Set,有两种类型的Ordered Sets——Sequence Ordered Set和Signal Ordered Set(保留扩展用)。其中,/O/出现在XGMII的第一个Lane中,/Q/紧跟着/O/出现。

Ordered Sets用来发送控制和状态信息,如Remote Fault和Local Fault。Ordered Sets包含一个控制字符,紧跟着3个数据字符。10GBASE-R应用场景只有一种Ordered Set类型,即Sequence Ordered Set,它的控制字符简写为/Q/。

Error(/E/)

当从XGMII接收到/E/字符,或者接收到无效控制帧时,/E/被发送。/E/可以使PCS层或者XGXS层接收到错误信息。

一个66位数据块怎么确认是否为有效数据块呢?当出现以下情况是,被判定为无效数据块:

1) 同步头不是01或者10;

2) 如果为控制帧,Block Type域为无效类型;

3) 如果为控制帧,控制码为无效控制码;

4) 任何无效Ordered Set Code(4位),包括0xF;

5) 64位负载各字符顺序错乱;

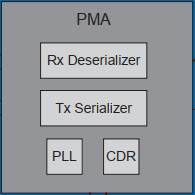

PMA

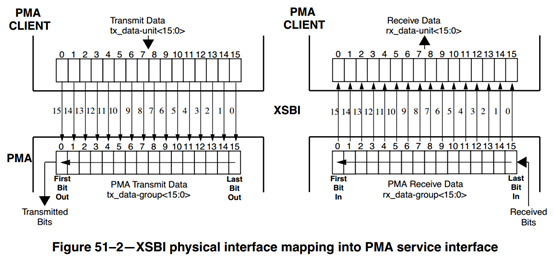

如图所示,10GBASE-R应用场景中,PMA子层介于PCS编码子层和PMD子层之间,它与PCS编码子层之间使用XSBI总线接口。

PMA主要包括TX Serializer、RX Deserializer、PLL和CDR几部分。其中CDR负责从接收的数据中恢复出时钟信号,并通过PLL输出发送数据时钟。发送方向,Tx Serializer负责将并行数据转换成串行数据。接收方向,Rx Deserializer负责将接收的串行数据转换成并行数据。

在PMA的实现中,针对发送通道可以配置预加重值和VOD值。预加重是噪声整形技术在模拟信号处理中的应用,其原理是在信号发送之前,先对模拟信号的高频分量进行适当提升;在收到信号之后,再对信号进行逆处理,即去加重,对高频分量进行适当衰减。预加重与去加重技术可以降低信号在传输过程中的高频损耗,也可以使噪声的频谱发生变化,这就是模拟降噪的原理。在接收方向,使用失调消除技术(offset cancellation)进行降噪。

接收方向

接收方向,PMA层从PMD层接收数据,然后发送到PCS层:

1) 从接收PMD的串行数据中恢复时钟,并将时钟信号传送到PCS编码层;

2) 将10Gb/s串行数据并行化,变成16bit并行数据,速率为644.53Mbps,通过XSBI(10G Sixteen Bit Interface)接口,发送到PCS编码层;

3) 提供链路状况信息;

发送方向

发送方向,PMA层从PCS层接收数据,然后发送到PMD层:

1) 提供时钟信号给PCS层;

2) 从PCS编码层接收16bit并行数据进行串行化,变成10Gb/s串行数据发送到PMD层;

PMD

10GBASE-R应用场景中,PMD子层负责光电信号转换,即光模块。

自协商

目前只有千兆PHY才支持自协商模式,如10/100/1000M自适应PHY。

PHY自协商是通过快速连接脉冲(Fast Link Pulse)信号实现,简称FLP。自协商的双方通过FLP来交互数据。

在具备自协商能力的端口没有Link的情况下,端口一直发送FLP,在FLP中包含着自己的连接能力信息,包括支持的速率能力、双工能力、流控能力等。这个连接能力是从自协商能力寄存器中得到的(Auto-Negotiation Advertisement Register ,PHY标准寄存器地址4 )。FLP依靠脉冲位置编码携带数据,一个FLP突发包含33个脉冲位置。17个奇数位置脉冲为时钟脉冲,时钟脉冲总是存在的;16个偶数位置脉冲用来表示数据:此位置有脉冲表示1,此位置没有脉冲表示0。这样1个FPL的突发就可以传输16bit的数据。自协商交互数据就这样通过物理线路被传输。

如果两端都支持自协商,则都会接收到对方的FLP,并且把FLP中的信息解码出来。得到对方的连接能力。并且把对端的自协商能力值记录在自协商对端能力寄存器中(Auto-Negotiation Link Partner Ability Register , PHY标准寄存器地址5 )。同时把状态寄存器(PHY标准寄存器地址1)的自协商完成bit(bit5)置成1。在自协商未完成的情况下,这个bit一直为0。然后各自根据自己和对方的最大连接能力,选择最好的连接方式Link。比如,如果双方都即支持10M也支持100M,则速率按照100M连接;双方都即支持全双工也支持半双工,则按照全双工连接。一定连接建立后,FLP就停止发送。直到链路中断,或者得到自协商Restart命令时,才会再次发送FLP。

Error and Fault Handling

数据帧接收过程中,通常是/S/ + /D/ … /D/ + /T/序列,如果在/C/控制字符出现在/S/和/T/之间,那么RS层应该告知MAC层发生了FrameCheckError。如果/S/出现在除了lane 0之外的lane上,RS层也会感知到错误。

数据帧发送过程中,PHY必须仔细校验保证数据不被篡改,因为一旦对端发现接收到的数据被篡改,就会发送Error控制字符。

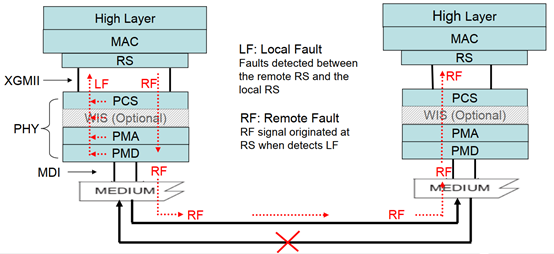

Link Fault Signaling

关于Link Fault Signaling,参考IEEE 802.3ae Clause46.3.4章节。

首先要区分两个概念,PHY层Link Up和LLC层Link Up,前者是物理链路的连接状态,后者是逻辑链路的连接状态。通常,此处,Link Fault指的是PHY层的链路连接状态。

PHY层的链路状态指Local RS层和Remote RS层之间的链路状态。

PHY层的各子层都需要具备检测链路错误的能力,检测链路错误主要分为两个方面:

1) 检测I/O信号;

2) 传输数据/控制帧解析,包括:

CODEC Synchronization;

Lane Alignment,如/S/只能出现在Lane 0等;

Link Status Report Recognized;

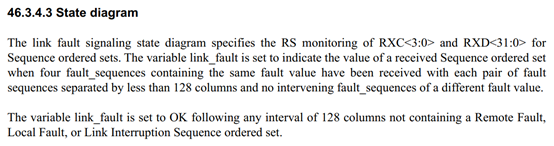

Link Status Message是一个四字节的Ordered Sets,其中Lane 0是Sequence控制字符,剩下的3个是数据部分。Local Fault帧的Sequence控制字符是0x9C,Remote Fault帧的Sequence控制字符是0x00。

任何一方,在接收过程中检测到链路错误,都会产生Local Fault, Local Fault帧会在接收方向透传PHY各子层,直到RS层。

RS层负责处理Local Fault帧,同时发送Remote Fault帧给对端RS层(只有RS层可以残生Remote Fault帧)。Remote Fault帧在RS层之间透传。RS层之所有会发送Remote Fault帧给对端,是假设只有接收链路发生链路错误,发送链路没有问题。

当RS层在128个时钟周期内接收到4个以上Local Fault帧时,它会通知本机MAC停止发送数据,并连续发送Remote Fault帧给对端RS层。当RS层在128个时钟周期内,连续接收到4个Remote Fault帧时,才会认为发送链路出现问题,它会通知本机MAC停止发送数据,并在发送链路上连续发送Idle帧。

在128个时钟周期内,没有接收到Local Fault帧或者Remote Fault帧,则表示链路状态正常。

浙公网安备 33010602011771号

浙公网安备 33010602011771号