LPC2138微控制器之时钟和PLL

第二章、时钟和PLL

LPC213x系列微控制器XTAL1引脚支持外部输入1~50MHz时钟信号,其内部时钟振荡电路支持的外部晶振范围为1~30MHz。如果PLL使能或者处于bootloader模式时,PLL的输入时钟被限制在10~25MHz。

LPC2138内部时钟振荡电路可以工作在两种模式:

1)Slave模式

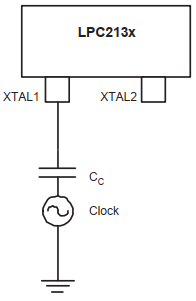

Slave模式下,内部时钟振荡电路禁用,仅通过XTAL1引脚外接时钟源,频率范围为1~50MHz。

如图所示,此模式下,外部时钟源需要结合Cc电容(100pF)一起工作,XTAL2引脚悬空即可。

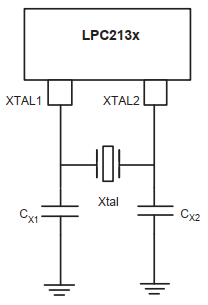

2)Oscillation模式

Oscillation模式下,内部时钟振荡电路结合外部晶振,一起提供系统时钟源,频率范围1~30MHz。

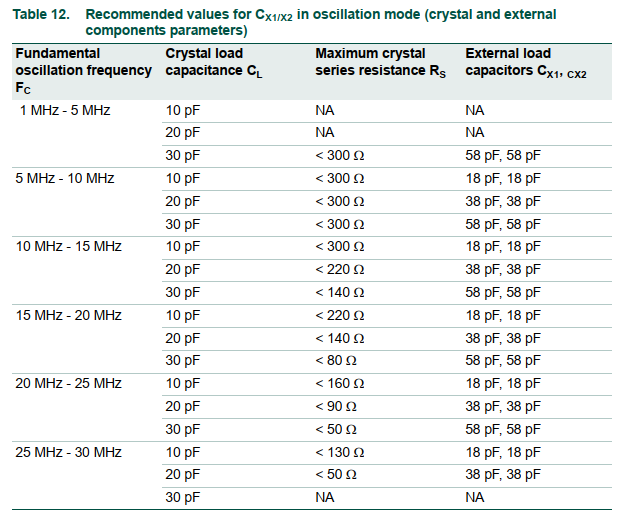

不同频率范围下,Cx1和Cx2电容值如下表。

Fosc系统时钟源

无论使用外部时钟源还是外部晶振结合内部时钟振荡电路,均输出Fosc系统时钟源,该时钟源衍生出ARM核时钟源CCLK和外设时钟源PCLK。

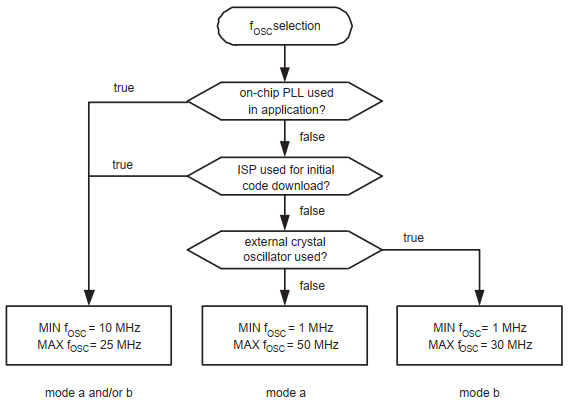

Fosc时钟源仲裁机制如下:

mode a即Slave模式,mode b即Oscillation模式。

PLL、CCLK和PCLK

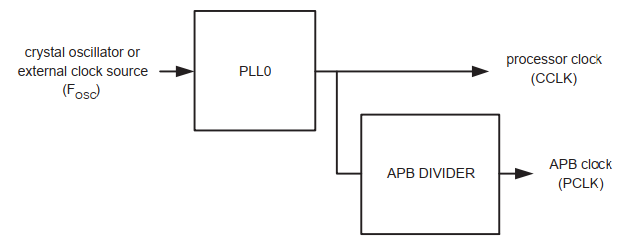

PLL介于内部时钟振荡电路和ARM核之间,其输入时钟为Fosc(此时Fosc限制在10~25MHz)。

PLL基于Fosc时钟源进行分频或者倍频产生CCLK,为ARM核提供工作时钟。

如果PLL未使能时,CCLK直接使用Fosc时钟源。

在CCLK的基础上通过APB Divider分频器进一步分频,为外设提供工作时钟PCLK。

默认情况下,PCLK为1/4 CCLK,可以通过软件配置为CCLK或者1/2 CCLK。