[Linux] CPU架构/指令集:RISC / CISC | arm | amd | X86/i386 | aarch64

1 前言

本文是解决在软件开发、软件交付过程中,常常需要找寻与服务器硬件的CPU架构适配的软件包时,开发者和交付者又时常摸不着头脑、【迷迷糊糊】地就下载了某个所谓“适配”、“兼容”的各种软件包。

那么,我们真的get到了背后的关系(CPU指令集、CPU架构、CPU处理器/芯片、Soc(芯片上的系统)、x86_64架构、arm架构等等),这一层面了吗?

正本清源,方能以更高de效率去理解、学习基于此的上层知识模块,降低开发风险、提高工作效率。

扯远啦~ 赶紧一把回来!那么,先从CPU架构所涉及的相关概念说起~

2 基本概念

2.0 CPU := 中央处理器

Central Processing Unit,中央处理器。

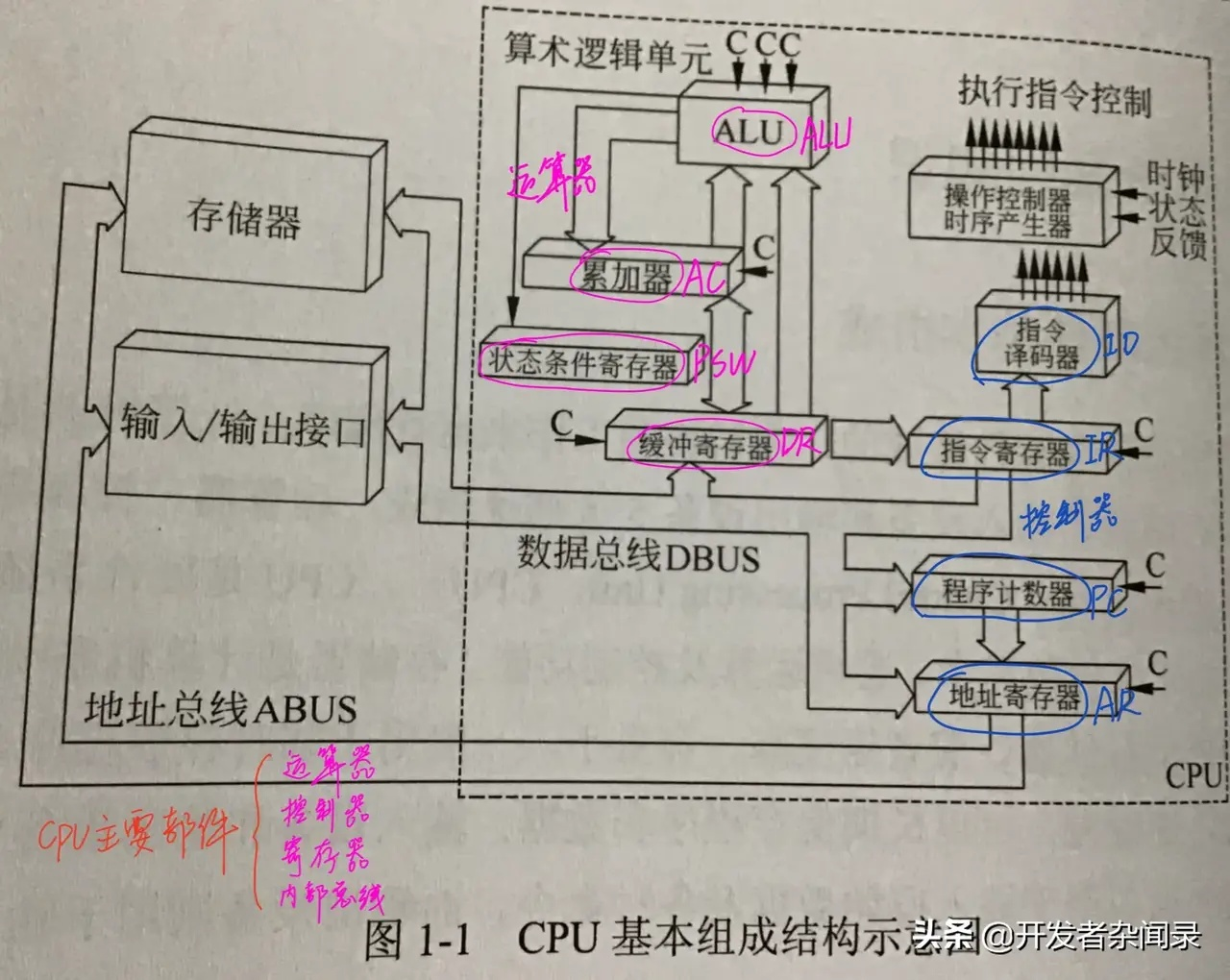

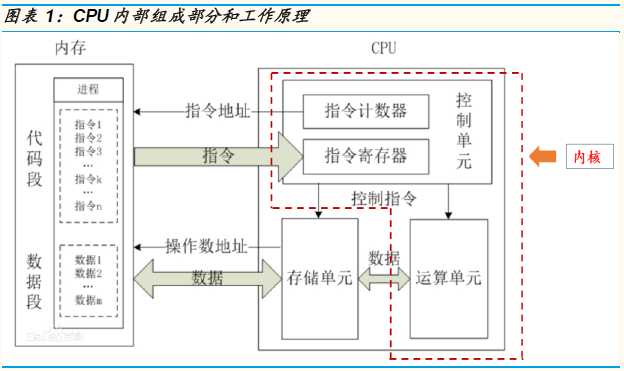

CPU是计算机系统的核心和 大脑,主要由控制器、运算器、存储器和连接总线构成。

其中,控制器和运算器组成CPU的内核,【内核】从存储器中提取数据,根据控制器中的指令集将数据解码,通过运算器中的微架构(电路)进行运算得到结果,以某种格式将执行结果写入存储器。

因此,内核的基础就是【指令集(指令集架构)】和【微架构】。

延申1: 指令集(架构)

指令集是所有指令的集合,它规定了CPU可执行的所有操作微架构是完成这些指令操作的电路设计。

相同的指令集可以有不同的微架构,如Intel 和AMD都是基于X86指令集但微架构不同。

指令集架构( Instruction Set Architecture ),又称指令集或指令集体系,是计算机体系结构中与程序设计有关的部分,包含了基本数据类型,指令集,寄存器,寻址模式,存储体系,中断,异常处理以及外部 I/O 。

指令集架构包含一系列的 opcode 即操作码(机器语言),以及由特定处理器执行的基本命令。

简单地来说,指令集一般被整合在操作系统内核最底层的硬件抽象层中,属于计算机中硬件与软件的接口,它向操作系统定义了CPU的基本功能。

2.1 程序语言 代际 | 编译型程序语言VS解释型程序语言

2.1.1 计算机程序语言的发展代际: 3代

- ①第1代: 机器语言 (二进制的机器代码/指令集集合) [20世纪中期]

Eg: 00000000

机器语言是一种指令集的体系。

这种指令集,称机器码(machine code),是电脑的CPU可直接解读的数据。

机器码有时也被称为原生码(Native Code),这个名词比较强调某种编程语言或库,它与运行平台相关的部份。

1) 【二进制 机器指令集合、机器可直接识别和执行】机器语言是用二进制代码表示的计算机能直接识别和执行的一种机器指令的集合。

2) 【灵活、执行效率高】它是计算机的设计者通过计算机的硬件结构赋予计算机的操作功能。机器语言具有灵活、直接执行和速度快等特点。

3) 【可移植性差、强硬件相关】不同型号的计算机,其机器语言是不相通的,按着一种计算机的机器指令编制的程序,不能在另一种计算机上执行。

- ②第2代: 汇编语言/符号语言 (用类人类语言描述指令集,即 非指令集, x86汇编 /8086汇编 /AT&T汇编 /Intel汇编 /ARM汇编) [20世纪50年代-60年代]

Eg: ADD / MOV(数据传送指令) A,15 / HLT(中止) / MOV AX, 2000H(将16位数据2000H传送到AX寄存器) / MOV AX, BX(将BX寄存器的16位数据传送到AX寄存器)

汇编语言是一种用于电子计算机、微处理器、微控制器或其他可编程器件的低级语言,亦称为符号语言。

在汇编语言中,用助记符(Mnemonics)代替【机器指令】的操作码,用地址符号(Symbol)或标号(Label)代替指令或操作数的地址。

汇编语言是直接面向处理器(Processor)的程序设计语言。

处理器是在指令的控制下工作的,处理器可以识别的每一条指令称为【机器指令】。

每一种处理器都有自己可以识别的一整套指令,称为【指令集】。

处理器执行指令时,根据不同的指令采取不同的动作,完成不同的功能,既可以改变自己内部的工作状态,也能控制其它外围电路的工作状态。

汇编语言和CPU息息相关,但是不能把汇编语言完全等同于CPU的机器指令。

不同架构的CPU指令并不相同,如x86,powerpc,arm各有各的指令系统;甚至同一种架构的CPU有几套指令集,典型的如arm除了有32位的指令集外,还有一套16位的thumb指令集。

但是作为开发语言的汇编,本质上是一套语法规则和助记符的集合,它可以包容不同的指令集。

如果从CPU体系来划分,常见的汇编有两种:IBM PC汇编和ARM汇编。

如果从未接触过汇编语言,建议从X86的汇编入手,硬件、软件、参考资料既多又便宜。

———— 摘自·知乎网友

- ③第3代: 高级语言 (人类化的程序语言, C++/Java/Python/C#/JavaScript等)

Eg: A=A+15

高级程序语言是高度封装了的编程语言,与低级语言相对。它是以人类的日常语言为基础的一种编程语言。

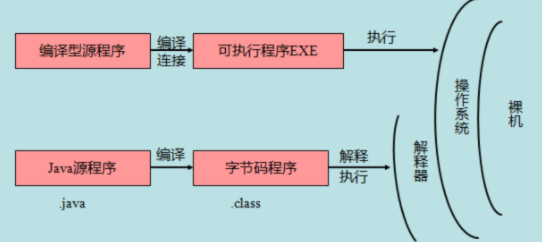

2.1.2 高级程序语言: 编译型程序语言 VS 解释型程序语言

参见:

2.2 源代码 ----> 【编译】 ----> 【指令集(集合)】

CPU执行计算任务时都需要遵从一定的规范/语言,程序(可执行的、二进制机器语言)在被执行前都需要先翻译为CPU可理解的语言。

这种规范或语言就是【指令集】(ISA,Instruction Set Architecture)。

程序(二进制执行程序)被按照某种指令集的规范翻译为CPU可识别的底层二进制代码的过程叫做【编译】(Compile)

- 编译的一般过程:

源程序分析

词法分析

语法分析

语法检查

中间代码生成

代码优化

目标代码生成

2.2.1 CPU指令

处理器是在【指令】的控制下工作的,处理器可以识别的每一条【指令】称为【机器指令】。

计算机指令就是指挥机器工作的指示和命令,程序就是一系列按一定顺序排列的指令,执行程序的过程就是计算机的工作过程。

在计算机中,指示计算机硬件执行某种运算、处理功能的命令称为指令。

指令是计算机运行的最小的功能单位,而硬件的作用是完成每条指令规定的功能。

2.2.2 CPU 指令集架构 / 指令集 / 指令系统

每一种处理器都有自己可以识别的一整套指令,称为【指令集】。

处理器执行指令时,根据不同的指令采取不同的动作,完成不同的功能,既可以改变自己内部的工作状态,也能控制其它外围电路的工作状态。

处理器【指令集】只是定义了硬件与软件(含OS)之间的接口、标准规范,而不定义处理器的实现

一台计算机上全部指令的集合,就是这台计算机的指令系统。

指令系统也称指令集,是这台计算机全部功能的体现。

而人们设计计算机首要考虑的是它拥有的功能,也就是首先要按功能档次设计指令集;然后,按指令集的要求在硬件上实现。

指令系统不仅仅是指令的集合,还包括全部指令的指令格式、寻址方式和数据形式。

- 概念

CPU指令集架构,简称指令集

CPU指令集架构

:= ISA(Instruction Set Architecture)

:= 指令集

≈ 指令系统

:= 决定/指导/规范 处理器架构

!= 微架构

- 总分类(判断依据:指令系统是否精简): RISC VS CISC

【CISC】

CISC(Complex Instruction Set Computer, 复杂指令系统计算机),除了RISC,任何全指令集计算机都使用的是复杂指令集计算(CISC)。

常见使用CISC的处理器主要有X86.

从计算机诞生以来,人们一直沿用CISC指令集方式。

早期的桌面软件是按CISC设计的,并一直沿续到现在。目前,桌面计算机流行的x86体系结构即使用CISC。

微处理器(CPU)厂商一直在走CISC的发展道路,包括Intel、AMD,还有其他一些现在已经更名的厂商,如TI(德州仪器)、IBM以及VIA(威盛)等。

在CISC微处理器中,程序的各条指令是按顺序串行执行的,每条指令中的各个操作也是按顺序串行执行的。

顺序执行的优点是控制简单,但计算机各部分的利用率不高,执行速度慢。

CISC架构的服务器主要以IA-32架构(Intel Architecture,英特尔架构)为主,而且多数为中低档服务器所采用。

【RISC】

RISC(reduced instruction set computer,精简指令集计算机)是一种执行较少类型计算机指令的微处理器。

纽约约克镇IBM研究中心的John Cocke证明,计算机中约20%的指令承担了80%的工作,他于1974年提出了RISC的概念。

目前常见使用RISC的处理器包括DEC Alpha、ARC、ARM、MIPS、PowerPC、SPARC和SuperH等。

RISC是一种执行较少类型计算机指令的微处理器,起源于80年代的MIPS主机(即RISC机),RISC机中采用的微处理器统称RISC处理器。

这样一来,它能够以更快的速度执行操作(每秒执行更多百万条指令,即MIPS)。因为计算机执行每个指令类型都需要额外的晶体管和电路元件,计算机指令集越大就会使微处理器更复杂,执行操作也会更慢。

2.2.3 处理器架构 := CPU 微架构

CPU处理器架构

:= 微架构

:= 依据 CPU指令集(架构) 规范所开发的、用硬件电路实现对应CPU指令

:= CPU指令集(架构) 的 接口

3 RISC 指令系统/指令集(架构) VS CISC 指令系统/指令集(架构)

3.1 RISC 指令集(架构) VS CISC 指令集(架构)

| 对比项 | CISC | RISC |

|---|---|---|

| 目的 | 增强原有指令的功能,设置更为复杂的新指令实现软件功能的硬化 | 减少指令种类和简化指令功能,提高指令的执行速度 |

| 指令系统 | 复杂、庞大 | 简单、精简 |

| 指令数目 | 一般大于200条 | 一般小于100条 |

| 指令字长 | 不固定 | 固定 |

| 可访存指令 | 不加限制 | 只有 LOAD/STORE指令 |

| 各指令的执行时长 | 指令间执行时长差距很大 | 绝大多数在1个周期内完成 |

| 各种指令的使用频度 | 指令间频度差距很大 | 指令都比较常用 |

| 通用寄存器数量 | 较少 | 多 |

| 中断 | 机器是在一条指令执行结束后响应中断 | 机器在一条指令执行的适当地方可响应中断 |

| 单元电路(功耗) | 包含有丰富的电路单元,因而功能强、面积大、功耗大 | 包含有较少的单元电路,因而面积小、功耗低 |

| 目标代码的执行效率 | 难以用优化编译生成高效的目标代码程序 | 采用优化的编译程序,生成代码相对较为高效 |

| 控制方式 | 绝大多数为微程序控制 | 绝大多数为组合逻辑控制 |

| 指令流水线 | 可以通过一定方式实现 | 必须实现 |

| 微处理器的设计周期 | 微处理器结构复杂,设计周期长 | 微处理器结构简单,布局紧凑,设计周期短,且易于采用最新技术 |

| 适用场景 | 适用于【通用型机器】;功能强大,易于/利于实现、处理特殊功能,因有专用指令来完成特定功能 | 适用于【专用型机器】,因RISC指令系统的确定与特定的应用领域有关;指令规整,性能容易把握,易学易用 |

| 被应用的指令集(架构) | X86指令集(架构) | MIPS、ARM、RISC-V、Power-PC[IBM]、SPARC、AArch64(基于ARMv8架构的、分离出来的64位的执行状态) 指令集(架构) |

3.2 RISC 指令集 有哪些?

| 指令集架构 | 发源于(时间、干系人) | 特点 | 具体示例 | 拓展、延申出来的架构 | 微处理器 | 是否开源 | 备注 |

|---|---|---|---|---|---|---|---|

| MIPS(Million Instructions Per Second) 指令集架构 | 1.创立于1998年; 2.创始者: 斯坦福大学教授John LeRoy Hennessy(RISC架构的开拓者) |

1.在1999年前被适用最多; 2.更成熟; |

MIPS I/II/III/IV/V/16/32/64 | (略) | 龙芯芯片 | 商业闭源 | 1.MIPS本来就没有一个较为统一的生态。因MIPS被转卖多次、很多相关专利已经被卖掉了(导致当前母公司Wave Computing 所掌握的专利本就有限)、碎片化问题非常严重 |

| ARM(Acorn/Advanced RISC Machine) 指令集架构 | 1. 创立于1985年; 2. 创始者:Acorn公司、加州大学伯克利分校Sophie Wilson(指令集开发)和Steve Furber(芯片设计)2位教授(2家单位合作推出ARM1芯片,以此作为其未来个人计算机的中枢) |

1.低功耗、低成本; 2.ARM家族占比所有32位嵌入式处理器的75%,成为占全世界最多数的32位架构; 3.广泛使用于嵌入式系统(功耗低); 4.消费性电子:可携式装置(PDA、移动端设备(占主流地位)、移动电话、多媒体播放器、掌上型电子游戏,和计算机),电脑外设(硬盘、桌上型路由器),甚至导弹的弹载计算机等军用设施 |

ARMv7a架构: ARM Cortex A8/A9 ARMv7M架构:ARM Cortex A3/A4 ARMv8架构(支持32+64位架构):ARM Cortex A32/35/53/57/72/73/77/78 |

Apple Swift/架构、Marvell的XScale架构、德州仪器的OMAP系列架构 | 高通骁龙Qualcomm 810处理器 海思麒麟950处理器 三星Exynos 4412处理器 Apple A系列处理器、Apple A6/A6X CPU处理器(基于Apple Swift 微架构[ARM指令集扩展的微架构]) |

商业闭源(IP授权模式) | 1.ARM公司的商业模式: IP(Intellectual Property,知识产权)授权模式(ARM架构授权、IP核授权、使用级授权); 2.主要业务范围: ARM指令集、ARM微架构、ARM芯片(不自己造) |

| AArch64/ARM64(ARMv8A架构的2种执行状态/执行模式之一,64位指令集架构) | 1. 概念于2011年在美国加州圣克拉拉的一场技术大会“ARM TechCon 2011”的ARM公司院士、首席架构师Richard Grisenthwaite发布 | 1.ARMv8架构基于32位的ARMv7而来,并保留了TrustZone安全执行环境、虚拟化、NEON(高级SIMD)等关键技术特性; 2.2012年宣贯 2.ARMv8架构第一个64位指令集处理器架构“ARMv8”(完全向下兼容32位ARM架构); 3.ARMv8架构在32位指令的基础上增加64位操作能力,其包括AArch64(采用ARM Cortex A64指令集)、AArch32(采用ARM Cortex A32 + T32指令集)2种主要执行状态,其中前者引入了一套新的指令集“A64”专门用于64位处理,而后者用来兼容现有的32位ARM指令集(便于现有软件的移植) 4.ARMv8架构完全向下兼容现有的32位ARMv7软件,而且运行于ARMv8上的64位操作系统也可以简单、高效地支持现有的32位软件 |

... | ... | ... | (同上) | aarch64的Apple后端称为arm64,而LLVM社区开发的后端称为aarch64(因为它是64位ISA的规范名称),后来两者合并,后端现在称为aarch64 |

| AArch32 指令集(ARMv8A架构的2种执行状态/执行模式之一,64位指令集架构) | (同上) | (同上) | (同上) | (同上) | (同上) | (同上) | (暂无) |

| Power PC(Performance Optimization With Enhanced RISC – Performance Computing, 简称:PPC) 指令集 | 1.POWER是1991年,Apple、IBM、Motorola组成的AIM联盟所发展出的微处理器架构; 2.PowerPC是整个AIM联盟平台的一部分,并且是到目前为止唯一的一部分; 3.但苹果电脑自2005年起,将旗下电脑产品转用Intel CPU; 4.该设计是从早期的RISC架构(比如IBM 801)与MIPS架构的处理器得到灵感的 |

1.强嵌入式表现: 高性能、能耗损失低、散热低 2.主要应用领域:高端服务器、嵌入式设备、星载计算机 |

(略) | (略) | 任天堂Gamecube、MPC505/821/850/860/8240/8245/8260/8560 | 现已开源 | 1.所有 PowerPC(包括 64 位实现)都使用定长的 32 位指令; 2.Power QUICC系列微处理器一般有3个功能模块组成,嵌入式PowerPC核(EMPCC),系统接口单元(SIU)以及通信处理器(CPM)模块。这3个模块内部总线都是32位 |

| SPARC(Scalable Processor Architecture可伸缩的处理器架构) 指令集 | 1987年,SUN公司与TI合作的成果 | 1.主要应用领域:星载计算机、嵌入式设备 | (略) | (略) | ERC 32(机构: 欧洲航天航空局) | 开源 | (略) |

| RISC-V / RISC-FIVE 指令集(Reduced Instruction Set Computer-V, 第5代精简指令集计算机) | 1.创始者: Keste Asanovic教授(RISC-V基金会主席)、David Pattern教授(《量化分析》作者、RISC-V概念的提出者、Turing奖获得者)、Andrew Waterman(SiFive首席工程师、Rocket处理器作者)、Yunsup Lee(SiFive的CTO、Rocket处理器作者) 2.源于2010年,当时加州大学伯克利分校(UC Berkeley)一研究团队要设计一款CPU,为该项目选架构的时候研究团队对比了当时的ARM、MIPS、SPARC和X86等,发现:不仅这些【指令集越来越复杂】,还有很多【IP法律】问题,再加上【X86授权难以获取】,【ARM授权价格昂贵】,所以该研究团队最终决定设计一套全新的指令集。 2.于是,成立了一个四人小组,仅用了3个月的时间就完成了RISC-V指令集的开发。 3.其【目标】是:新的指令集能满足从微控制器到超级计算机等各种尺寸的处理器 |

0.师出名门(名牌————UC Berkeley:先进性、开放性、可靠性); 1.生态联盟异常强大(非盈利性组织RISC-V基金会 ):高通、英伟达、NXP、三星、Microsemi、美光、中兴微电子、华为海思、联发科等半导体厂商;谷歌、阿里、IBM等IT软件公司;西部数据、希捷等硬盘数据存储大厂;SEGGER、Mentor Graphics、Express Logic等做开发工具的大厂;麻省理工学院、普林顿大学、印度理工学院、中科院计算所等世界一流科研院所. 2.【开源】+【免费】,且采用BSD许可证(Berkeley Software Distribution Protocol,商业公司最喜欢的开源许可证之一:允许使用者修改和重新发布代码,也允许使用或在BSD代码上开发商业软件发布和销 售); 3.IC设计开发者的学习、开发的难度/成本低。相对X86足足几千页的指令集手册,RISC-V是相当的简洁。 |

开源(BSD协议) |

3.2.1 MIPS 指令集

3.2.2 ARM 指令集

3.2.3 RISC-V 指令集

3.2.4 (IBM)Power-PC 指令集

3.2.5 SPARC 指令集

3.3 CISC 指令集 有哪些?

| 指令集架构 | 发源于(时间、干系人) | 特点 | 具体示例 | 拓展、延申出来的架构 | 微处理器 | 是否开源 | 备注 |

|---|---|---|---|---|---|---|---|

| X86 指令集(架构) | 创始者: Intel公司 | (略) | X86-32 / X86-64(即 AMD64 / Intel64) | (略) | Intel i8086 CPU处理器(首台X86 CPU) VIA CPU处理器 Intel Core I3/I5/I7/I9 CPU处理器 AMD CPU处理器 |

商业闭源 | (略) |

3.3.1 X86 指令集 : IA-32 / AMD64 / Intel64

厂商开发兼容某种指令集的CPU需要指令集专利持有者授权,典型的例如:Intel授权AMD,使后者可开发兼容x86指令集的CPU。

x86 指令集(架构):泛指一系列由Intel公司开发的CPU处理器的架构。最早为1978年面世的“Intel 8086”CPU。

早期的处理器均是以此格式来命名,如Intel 8086,80186,80286,80386,80486,这些架构被统称为x86。

由于数字不能被注册成为商标;因此,公司每当有新的处理器使用,均会采用可注册的名称,如: Pentium。

-

基于x86的32位架构(常被称为i386,x86),IA-32。

-

基于x86的64位架构,x86-64常称为AMD64或Intel64。

最早是由AMD公司,首先根据x86的架构生产出了64位的处理器,但是由于是竞争关系,Intel公司不愿意承认AMD64,近些年才推出了Intel64。

4 收尾:疑问解疑 & 花边故事

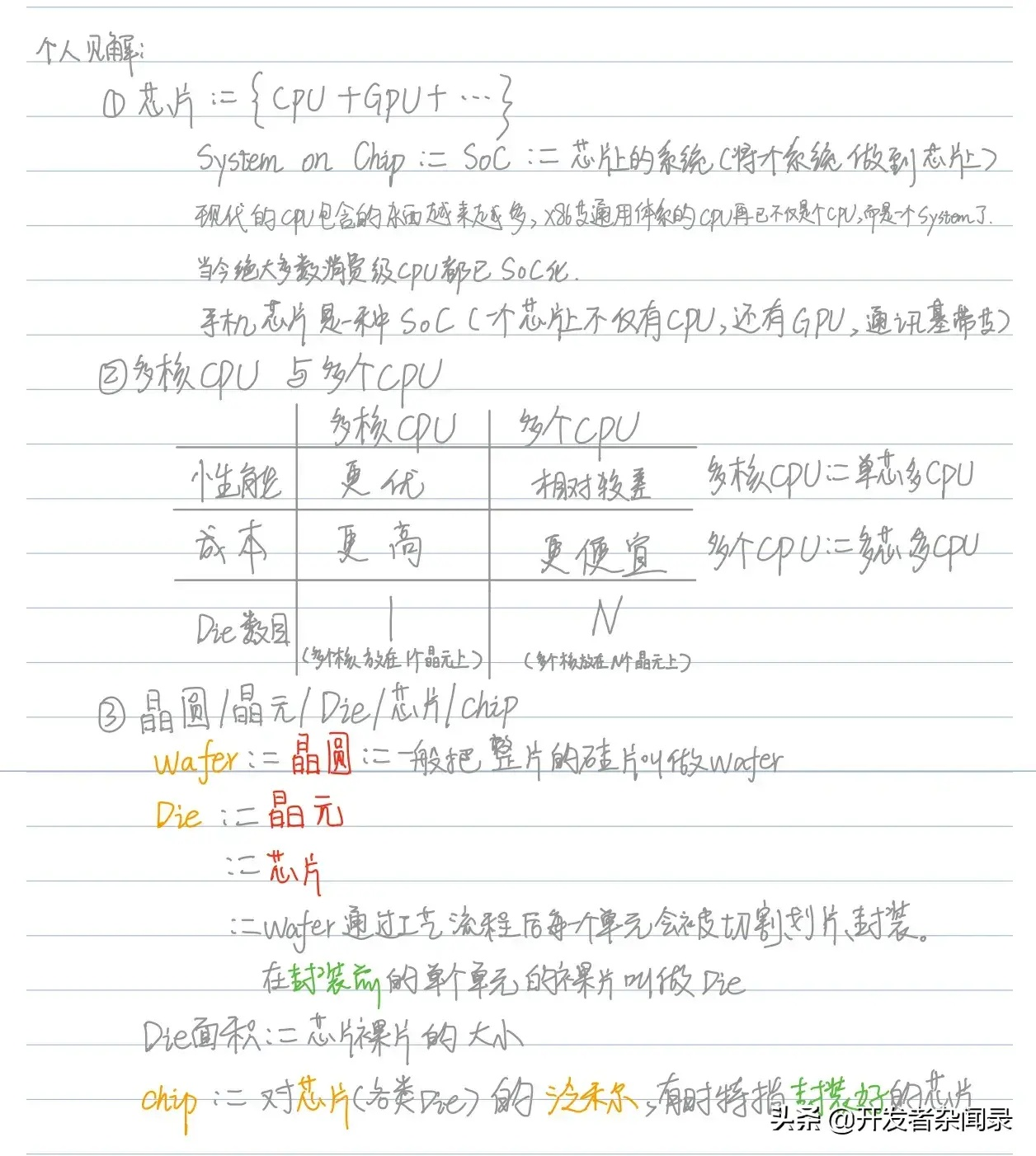

4.0 Chip | 芯片 := 晶元 := Die | Wafer := 晶圆 | 多核CPU VS 多个CPU | SoC

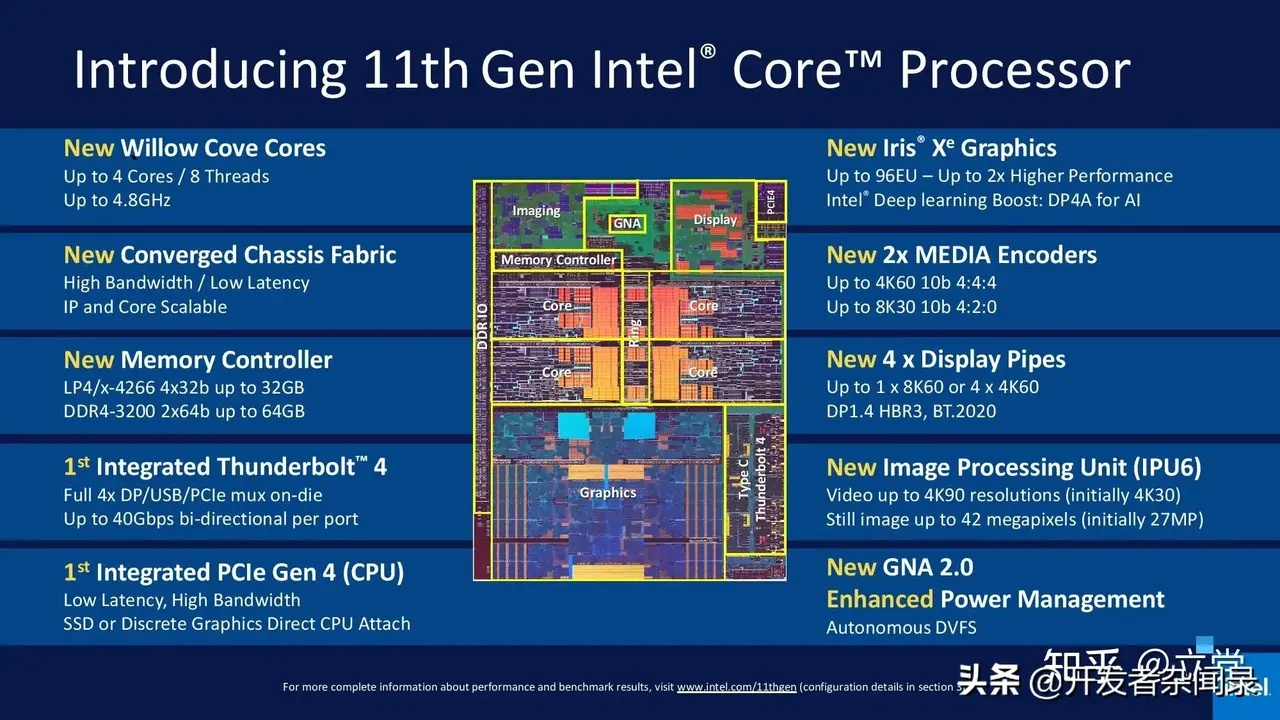

以 11th Gen Intel Core Processor 为例:

- Soc := System on Chip

Soc := System on Chip := 将N个CPU、GPU、内存等合成到一个芯片(晶圆)上 := 案例

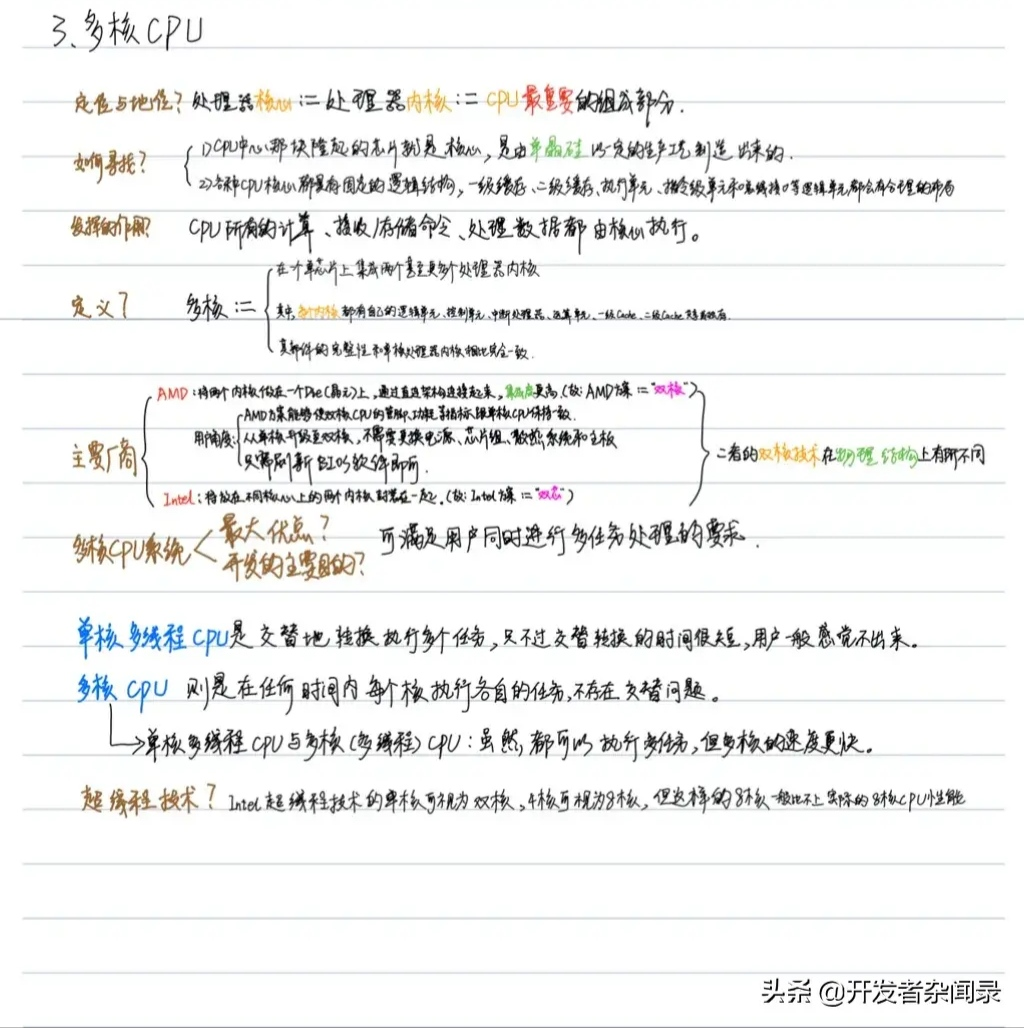

- 多核CPU

4.1 CPU的32、64位

- 32位CPU: 1个寄存器使用1个32位的0/1二进制串

- 64位CPU: 1个寄存器使用1个64位的0/1二进制串

即

- 【寄存器】的长度决定了CPU的【指令长度】和寻址能力

- 【指令长度】越长,所能支持的指令越多,地址空间越大,所能访问的物理地址越多

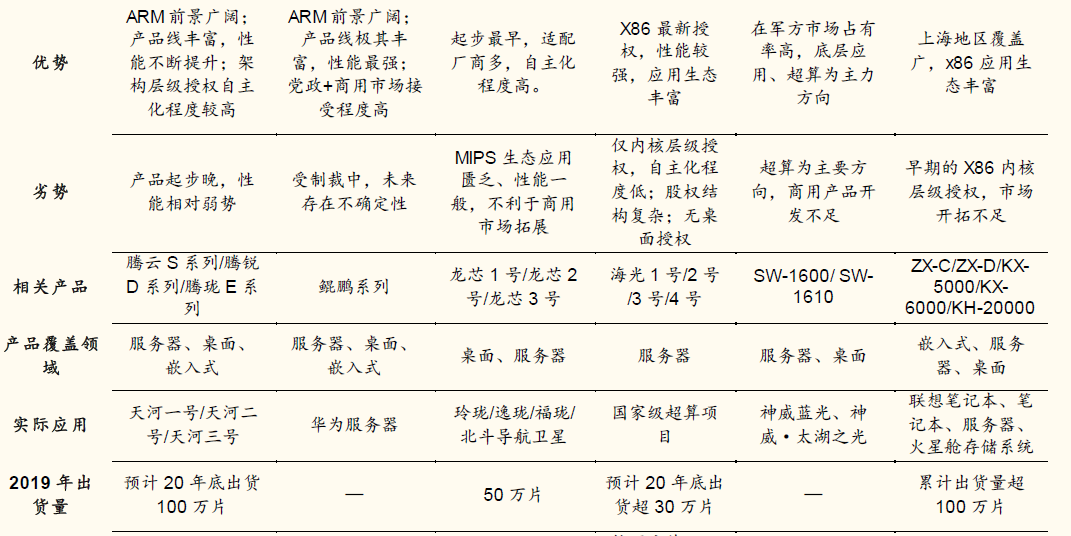

4.2 国产芯片公司

国产芯片种类繁多 基于 ARM 架构 授权的芯片厂商最有可能形成自主可控指令集。

由于指令集的复杂性和重要性,自主研发一套全新的指令集难度较大且效益不高。国产CPU厂家大多选择购买国外授权,以实现不同程度的自主可控。目前, 国产CPU架构大体可以分为三类:

-

第一类,是以龙芯为代表的MIPS 指令集架构和以申威为代表的 Alpha 架构,申威已基本实现完全自主可控(申威64已经完全形成了自己的架构),龙芯部分关键技术需付专利费。

-

第二类,是以飞腾和华为鲲鹏为代表基于 ARM 指令集授权的国产芯片。ARM主要有三种授权等级:使用层级授权、内核层级授权和架构 指令集层级授权,其中指令集层级授权等级最高,企业可以对ARM 指令集进行改造以实现自行设计处理器,如苹果在 ARM v7 架构基础上开发出苹果 Swift 架构, 其他如:高通、Krait 、Marvell等都是基于ARM指令集或微架构进行的改造。因此, 已经获得ARM V8 永久授权的海思、飞腾 等厂家凭借自身的研发能力, 亦有可能发展出一套自己的指令集架构 。

-

第三类,是以海光、兆芯为代表的获得X86的授权(仅内核层级的授权),未来扩充指令集形成自主可控指令集难度较大。因此, 可以 看 出, 在 自主可控程度上申威、龙芯 飞腾 、鲲鹏 海光、兆芯,但未来鲲鹏和飞腾如果基于 ARM V8 发展出自己的指令集, 则创新可信程度将显著提升 。同时,在未来ARM V9、V10 等新架构拿不到授权的情况下,依然可以维持先进性 。

【小结】

简单总结:

综合对比六大国产CPU厂商,市场竞争格局进一步明晰。

申威由于过去主要市场在军队,且其产品偏向底层应用及超算领域, Alpha 生态应用较少 预计其可获得的市场份额有限 。

海光、兆芯受制于X86 内核层级授权自主性较弱, 且海光仅获得AMD 服务器授权,暂未获得桌面应用授权, 兆芯由于使用台湾威盛电子的X86 早期授权,产品性能相对落后,且兆芯早期市场开拓不佳 。

因此,在党政信创市场,预计飞腾、鲲鹏和龙芯三家将成为主导 。

龙芯研发起步最早,党政市场原始份额较大(约占 70以上),国产 整机及 应用适配厂商较多,但MIPS 整体生态 、性能是劣势商用前景较一般,随着鲲鹏进入市场及飞腾逐步成熟, ARM体系的生态和性能优势逐步体现。

另一方面,在党政信创市场通过投资给当地带来税收及就业机会是获得份额的一大途径。

鲲鹏和中国长城均在多地成立了子公司 ,预计龙芯未来在党政信创领域的市占率会有所下降。

鲲鹏当前因为海思受到美国制裁,未来存在一定不确定性,预计其在党政信创市场拓展会有所取舍 。

对行业市场而言,行业市场规模是党政信创市场的数倍,行业市场对CPU性能 、生态等的要求也远高于信创市场。

因此, 在此前行业国产招标中基本只有鲲鹏 、海光两家获得更多订单, 鲲鹏作为华为海思旗下产品,性能已达到国际先进水平。

而ARM生态亦在不断成熟, 若不考虑美国制裁带来的负面影响,其前景最为光明。

海光因获得四年前AMD最先进产品授权, 且经过不断改良加之X86 架构的天然生态优势 ,在行业市场亦获得较多订单。

4.3 ARM公司的商业模式————IP知识产权授权模式

ARM的公司:安谋控股(ARM Holding plc),又称:ARM公司;总部位于剑桥的设计与软件公司,现已被日本的软银公司收购,后者同时也是国内互联网巨头阿里巴巴的最大股东。

ARM(Advanced RISC Machine,Acorn RISC Machine)也是1个CPU架构;非常适用于【移动通信】,这种低成本,高性能,低耗电的领域。

参见: 浅谈英国ARM公司的IP授权模式 - 电子说 【推荐】

4.4 竞争之烈: AMD公司 VS Intel公司

AMD

AMD(Advanced Micro Devices, (美国)超威半导体):是除了Intel以外,最大的【x86架构微处理器(CPU)】供应商;也是除了NVIDIA以外,仅有的【独立图形处理器(显卡/GPU)】供应商。

4.5 NVIDIA公司

4.4 SiFive公司

SiFive是基于免费且开放的RISC-V指令集架构的商业化处理器核心IP和芯片解决方案的领导者。

在RISC-V开创者和业内资深专家组成的团队领导下,SiFive帮助SoC设计人员缩短产品上市时间,以及通过定制的开放式架构处理器内核降低成本,同时,使系统设计人员能够构建基于RISC-V的定制半导体,从而实现芯片优化。

全球拥有15个办事处。

SiFive已经获得Sutter Hill Ventures,Qualcomm Ventures,Spark Captial,Osage University Partners, Chengwei,Huami,SK Hynix,Intel Capital以及Western Digital的支持。

4.5 Linux下如何查看计算机设备的CPU处理器、内存、磁盘等硬件信息?

X 参考文献

- [Linux]查看硬件及操作系统信息 - 博客园/千千寰宇 【推荐】

- 编译型语言与解释型语言的真正区别 - CSDN 【推荐】

- 解释型语言与编译型语言 - 博客园/千千寰宇

- 汇编语言有多少种? - Zhihu

- ARM内核和架构 - 博客园 【推荐】

- 技术宅:解密苹果A10为何更换四核架构 - 网易

- 同样ARM架构,为何苹果处理器更强? - 搜狐

- 三星最强芯,Exynos 7420 怎么样? - ifanr

- Exynos - 百度百科

- 一文读懂ARM技术架构 - 搜狐

- A12 bionic架构分析/Apple Swift/Cyclone/Twister - Zhihu

- 如何看待苹果抛弃intel,转向ARM架构? - Zhihu

- 什么是机器语言,汇编语言和高级语言 - 百度指导

- 4.3 CISC和RISC的基本概念 - CSDN

- CISC和RISC是什么?它们的特点和区别? - CSDN

- ARM宣布新架构ARMv8 终于进入64位世界 - 快科技

- ARM 64位处理器架构ARMv8技术浅析 - 快科技 【推荐】

- ARM Architecture / ARMv8-A - Wikipedis 【推荐】

- arm64和aarch64之间的区别 - oomake/码客

- ARMv8-AArch64简述 - CSDN 【推荐】

- AArch64 是什么 - CSDN

- PowerPC - 百度百科

- 什么是 BSD 协议? - 菜鸟教程 【推荐】

- RISC-V的前世今生 - CSDN 【推荐】

- 对RISC-V前途的一些看法 - CSDN

- RISC-V发展现状 - Zhihu 【推荐】

- RISC-V创始人做客紫光展锐,探讨未来技术新趋势 - 搜狐

- 浅谈英国ARM公司的IP授权模式 - 电子说 【推荐】

- 一文带你了解ARM的发展历程 - 电子说 【推荐】

- 上篇:国产CPU技术和架构全对比 - 程序员客栈 【推荐】

- Java编译(三) Java即时编译(JIT编译):运行时把Class文件字节码编译成本地机器码 - CSDN【推荐】

本文链接: https://www.cnblogs.com/johnnyzen

关于博文:评论和私信会在第一时间回复,或直接私信我。

版权声明:本博客所有文章除特别声明外,均采用 BY-NC-SA 许可协议。转载请注明出处!

日常交流:大数据与软件开发-QQ交流群: 774386015 【入群二维码】参见左下角。您的支持、鼓励是博主技术写作的重要动力!

浙公网安备 33010602011771号

浙公网安备 33010602011771号