单片机成长之路(51基础篇) - 023 N76e003 系统时钟切换到外部时钟

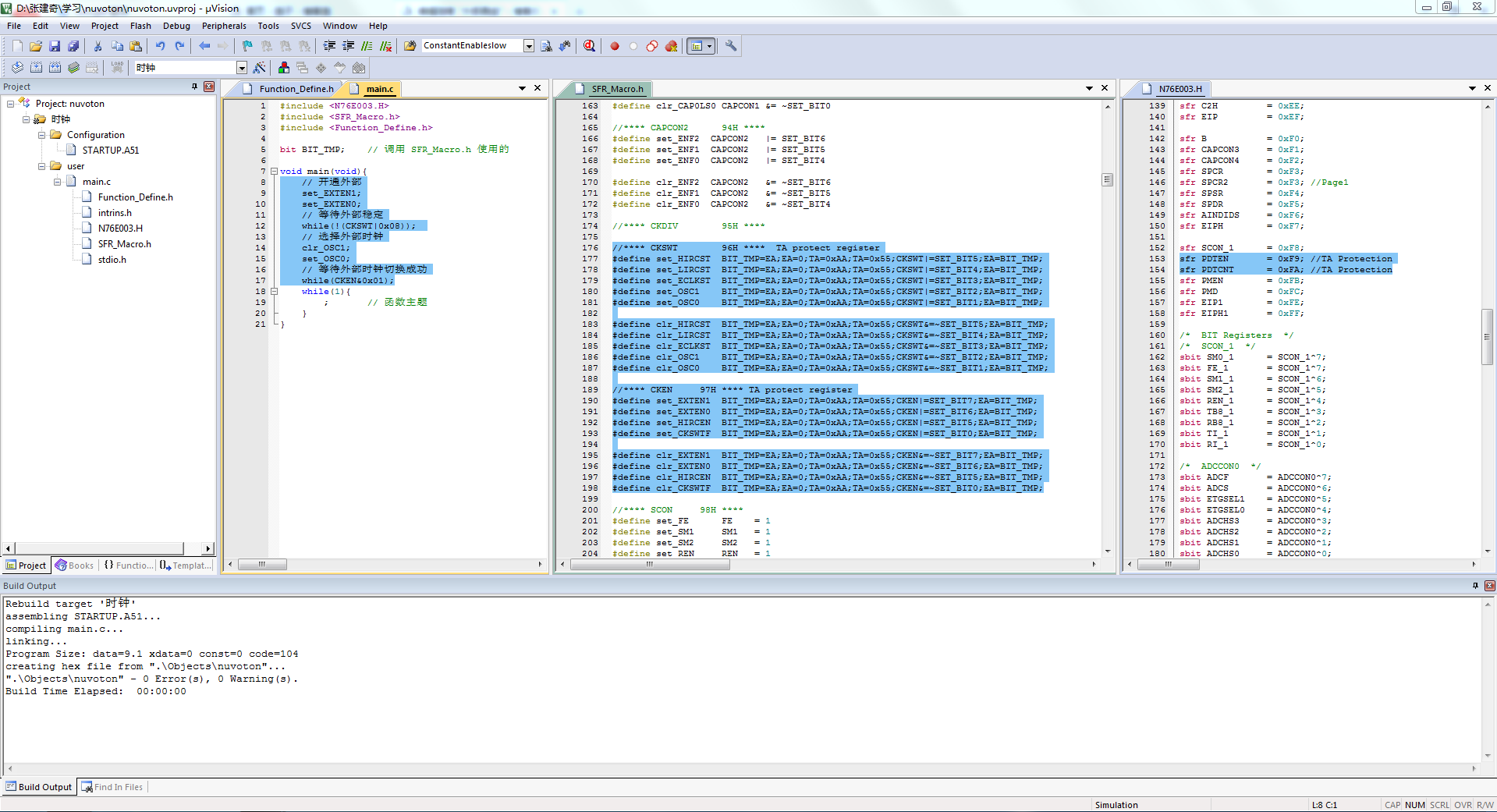

N76e003切换到外部时钟的资料很少(因为N76e003的片子是不支持无源晶振的,有源晶振的成本又很高,所以网上很少有对N76e003的介绍)。有图有真相:

代码如下:

main.c

1 #include <N76E003.H> 2 #include <SFR_Macro.h> 3 #include <Function_Define.h> 4 5 bit BIT_TMP; // 调用 SFR_Macro.h 使用的 6 7 void main(void){ 8 // 开通外部 9 set_EXTEN1; 10 set_EXTEN0; 11 // 等待外部稳定 12 while(!(CKSWT|0x08)); 13 // 选择外部时钟 14 clr_OSC1; 15 set_OSC0; 16 // 等待外部时钟切换成功 17 while(CKEN&0x01); 18 while(1){ 19 ; // 函数主题 20 } 21 }

1 /*-------------------------------------------------------------------------- 2 N76E003.H 3 4 Header file for Nuvoton N76E003 5 --------------------------------------------------------------------------*/ 6 7 #ifndef __N76E885_H__ 8 #define __N76E885_H__ 9 10 sfr P0 = 0x80; 11 sfr SP = 0x81; 12 sfr DPL = 0x82; 13 sfr DPH = 0x83; 14 sfr RWK = 0x86; 15 sfr PCON = 0x87; 16 17 sfr TCON = 0x88; 18 sfr TMOD = 0x89; 19 sfr TL0 = 0x8A; 20 sfr TL1 = 0x8B; 21 sfr TH0 = 0x8C; 22 sfr TH1 = 0x8D; 23 sfr CKCON = 0x8E; 24 sfr WKCON = 0x8F; 25 26 sfr P1 = 0x90; 27 sfr SFRS = 0x91; //TA Protection 28 sfr CAPCON0 = 0x92; 29 sfr CAPCON1 = 0x93; 30 sfr CAPCON2 = 0x94; 31 sfr CKDIV = 0x95; 32 sfr CKSWT = 0x96; //TA Protection 33 sfr CKEN = 0x97; //TA Protection 34 35 sfr SCON = 0x98; 36 sfr SBUF = 0x99; 37 sfr SBUF_1 = 0x9A; 38 sfr EIE = 0x9B; 39 sfr EIE1 = 0x9C; 40 sfr CHPCON = 0x9F; //TA Protection 41 42 sfr P2 = 0xA0; 43 sfr AUXR1 = 0xA2; 44 sfr BODCON0 = 0xA3; //TA Protection 45 sfr IAPTRG = 0xA4; //TA Protection 46 sfr IAPUEN = 0xA5; //TA Protection 47 sfr IAPAL = 0xA6; 48 sfr IAPAH = 0xA7; 49 50 sfr IE = 0xA8; 51 sfr SADDR = 0xA9; 52 sfr WDCON = 0xAA; //TA Protection 53 sfr BODCON1 = 0xAB; //TA Protection 54 sfr P3M1 = 0xAC; 55 sfr P3S = 0xAC; //Page1 56 sfr P3M2 = 0xAD; 57 sfr P3SR = 0xAD; //Page1 58 sfr IAPFD = 0xAE; 59 sfr IAPCN = 0xAF; 60 61 sfr P3 = 0xB0; 62 sfr P0M1 = 0xB1; 63 sfr P0S = 0xB1; //Page1 64 sfr P0M2 = 0xB2; 65 sfr P0SR = 0xB2; //Page1 66 sfr P1M1 = 0xB3; 67 sfr P1S = 0xB3; //Page1 68 sfr P1M2 = 0xB4; 69 sfr P1SR = 0xB4; //Page1 70 sfr P2S = 0xB5; 71 sfr IPH = 0xB7; 72 sfr PWMINTC = 0xB7; //Page1 73 74 sfr IP = 0xB8; 75 sfr SADEN = 0xB9; 76 sfr SADEN_1 = 0xBA; 77 sfr SADDR_1 = 0xBB; 78 sfr I2DAT = 0xBC; 79 sfr I2STAT = 0xBD; 80 sfr I2CLK = 0xBE; 81 sfr I2TOC = 0xBF; 82 83 sfr I2CON = 0xC0; 84 sfr I2ADDR = 0xC1; 85 sfr ADCRL = 0xC2; 86 sfr ADCRH = 0xC3; 87 sfr T3CON = 0xC4; 88 sfr PWM4H = 0xC4; //Page1 89 sfr RL3 = 0xC5; 90 sfr PWM5H = 0xC5; //Page1 91 sfr RH3 = 0xC6; 92 sfr PIOCON1 = 0xC6; //Page1 93 sfr TA = 0xC7; 94 95 sfr T2CON = 0xC8; 96 sfr T2MOD = 0xC9; 97 sfr RCMP2L = 0xCA; 98 sfr RCMP2H = 0xCB; 99 sfr TL2 = 0xCC; 100 sfr PWM4L = 0xCC; //Page1 101 sfr TH2 = 0xCD; 102 sfr PWM5L = 0xCD; //Page1 103 sfr ADCMPL = 0xCE; 104 sfr ADCMPH = 0xCF; 105 106 sfr PSW = 0xD0; 107 sfr PWMPH = 0xD1; 108 sfr PWM0H = 0xD2; 109 sfr PWM1H = 0xD3; 110 sfr PWM2H = 0xD4; 111 sfr PWM3H = 0xD5; 112 sfr PNP = 0xD6; 113 sfr FBD = 0xD7; 114 115 sfr PWMCON0 = 0xD8; 116 sfr PWMPL = 0xD9; 117 sfr PWM0L = 0xDA; 118 sfr PWM1L = 0xDB; 119 sfr PWM2L = 0xDC; 120 sfr PWM3L = 0xDD; 121 sfr PIOCON0 = 0xDE; 122 sfr PWMCON1 = 0xDF; 123 124 sfr ACC = 0xE0; 125 sfr ADCCON1 = 0xE1; 126 sfr ADCCON2 = 0xE2; 127 sfr ADCDLY = 0xE3; 128 sfr C0L = 0xE4; 129 sfr C0H = 0xE5; 130 sfr C1L = 0xE6; 131 sfr C1H = 0xE7; 132 133 sfr ADCCON0 = 0xE8; 134 sfr PICON = 0xE9; 135 sfr PINEN = 0xEA; 136 sfr PIPEN = 0xEB; 137 sfr PIF = 0xEC; 138 sfr C2L = 0xED; 139 sfr C2H = 0xEE; 140 sfr EIP = 0xEF; 141 142 sfr B = 0xF0; 143 sfr CAPCON3 = 0xF1; 144 sfr CAPCON4 = 0xF2; 145 sfr SPCR = 0xF3; 146 sfr SPCR2 = 0xF3; //Page1 147 sfr SPSR = 0xF4; 148 sfr SPDR = 0xF5; 149 sfr AINDIDS = 0xF6; 150 sfr EIPH = 0xF7; 151 152 sfr SCON_1 = 0xF8; 153 sfr PDTEN = 0xF9; //TA Protection 154 sfr PDTCNT = 0xFA; //TA Protection 155 sfr PMEN = 0xFB; 156 sfr PMD = 0xFC; 157 sfr EIP1 = 0xFE; 158 sfr EIPH1 = 0xFF; 159 160 /* BIT Registers */ 161 /* SCON_1 */ 162 sbit SM0_1 = SCON_1^7; 163 sbit FE_1 = SCON_1^7; 164 sbit SM1_1 = SCON_1^6; 165 sbit SM2_1 = SCON_1^5; 166 sbit REN_1 = SCON_1^4; 167 sbit TB8_1 = SCON_1^3; 168 sbit RB8_1 = SCON_1^2; 169 sbit TI_1 = SCON_1^1; 170 sbit RI_1 = SCON_1^0; 171 172 /* ADCCON0 */ 173 sbit ADCF = ADCCON0^7; 174 sbit ADCS = ADCCON0^6; 175 sbit ETGSEL1 = ADCCON0^5; 176 sbit ETGSEL0 = ADCCON0^4; 177 sbit ADCHS3 = ADCCON0^3; 178 sbit ADCHS2 = ADCCON0^2; 179 sbit ADCHS1 = ADCCON0^1; 180 sbit ADCHS0 = ADCCON0^0; 181 182 /* PWMCON0 */ 183 sbit PWMRUN = PWMCON0^7; 184 sbit LOAD = PWMCON0^6; 185 sbit PWMF = PWMCON0^5; 186 sbit CLRPWM = PWMCON0^4; 187 188 189 /* PSW */ 190 sbit CY = PSW^7; 191 sbit AC = PSW^6; 192 sbit F0 = PSW^5; 193 sbit RS1 = PSW^4; 194 sbit RS0 = PSW^3; 195 sbit OV = PSW^2; 196 sbit P = PSW^0; 197 198 /* T2CON */ 199 sbit TF2 = T2CON^7; 200 sbit TR2 = T2CON^2; 201 sbit CM_RL2 = T2CON^0; 202 203 /* I2CON */ 204 sbit I2CEN = I2CON^6; 205 sbit STA = I2CON^5; 206 sbit STO = I2CON^4; 207 sbit SI = I2CON^3; 208 sbit AA = I2CON^2; 209 sbit I2CPX = I2CON^0; 210 211 /* IP */ 212 sbit PADC = IP^6; 213 sbit PBOD = IP^5; 214 sbit PS = IP^4; 215 sbit PT1 = IP^3; 216 sbit PX1 = IP^2; 217 sbit PT0 = IP^1; 218 sbit PX0 = IP^0; 219 220 /* P3 */ 221 sbit P30 = P3^0; 222 223 /* IE */ 224 sbit EA = IE^7; 225 sbit EADC = IE^6; 226 sbit EBOD = IE^5; 227 sbit ES = IE^4; 228 sbit ET1 = IE^3; 229 sbit EX1 = IE^2; 230 sbit ET0 = IE^1; 231 sbit EX0 = IE^0; 232 233 /* P2 */ 234 sbit P20 = P2^0; 235 236 /* SCON */ 237 sbit SM0 = SCON^7; 238 sbit FE = SCON^7; 239 sbit SM1 = SCON^6; 240 sbit SM2 = SCON^5; 241 sbit REN = SCON^4; 242 sbit TB8 = SCON^3; 243 sbit RB8 = SCON^2; 244 sbit TI = SCON^1; 245 sbit RI = SCON^0; 246 247 /* P1 */ 248 sbit P17 = P1^7; 249 sbit AIN0 = P1^7; 250 251 sbit P10 = P1^0; 252 sbit PWM0 = P1^0; 253 sbit P11 = P1^1; 254 sbit PWM1 = P1^1; 255 sbit P12 = P1^2; 256 257 /* TCON */ 258 sbit TF1 = TCON^7; 259 sbit TR1 = TCON^6; 260 sbit TF0 = TCON^5; 261 sbit TR0 = TCON^4; 262 sbit IE1 = TCON^3; 263 sbit IT1 = TCON^2; 264 sbit IE0 = TCON^1; 265 sbit IT0 = TCON^0; 266 267 /* P0 */ 268 sbit P00 = P0^0; 269 sbit INT0 = P0^0; 270 sbit VREF = P0^0; 271 272 sbit P01 = P0^1; 273 sbit INT1 = P0^1; 274 sbit AIN1 = P0^1; 275 276 sbit P02 = P0^2; 277 sbit PWM2 = P0^2; 278 sbit AIN2 = P0^2; 279 280 sbit P03 = P0^3; 281 sbit PWM3 = P0^3; 282 sbit TXD = P0^3; 283 sbit AIN3 = P0^3; 284 285 sbit P04 = P0^4; 286 sbit SS = P0^4; 287 sbit AIN4 = P0^4; 288 289 sbit P05 = P0^5; 290 sbit PWM4 = P0^5; 291 sbit SPICK = P0^5; 292 sbit AIN5 = P0^5; 293 294 sbit P06 = P0^6; 295 sbit SCL = P0^6; 296 sbit AIN6 = P0^6; 297 sbit PWM5 = P0^6; 298 299 sbit P07 = P0^7; 300 sbit AIN7 = P0^7; 301 sbit PWM6 = P0^7; 302 303 304 #endif

1 /**** P0 80H *****/ 2 #define set_P00 P00 = 1 3 #define set_P01 P01 = 1 4 #define set_P02 P02 = 1 5 #define set_P03 P03 = 1 6 #define set_P04 P04 = 1 7 #define set_P05 P05 = 1 8 #define set_P06 P06 = 1 9 #define set_P07 P07 = 1 10 11 #define clr_P00 P00 = 0 12 #define clr_P01 P01 = 0 13 #define clr_P02 P02 = 0 14 #define clr_P03 P03 = 0 15 #define clr_P04 P04 = 0 16 #define clr_P05 P05 = 0 17 #define clr_P06 P06 = 0 18 #define clr_P07 P07 = 0 19 20 //**** SP 81H **** 21 //**** DPH 82H **** 22 //**** DPL 83H **** 23 //**** RWK 86H **** 24 25 //**** PCON 87H ***** 26 #define set_SMOD PCON |= SET_BIT7 27 #define set_SMOD0 PCON |= SET_BIT6 28 #define set_POF PCON |= SET_BIT4 29 #define set_GF1 PCON |= SET_BIT3 30 #define set_GF0 PCON |= SET_BIT2 31 #define set_PD PCON |= SET_BIT1 32 #define set_IDL PCON |= SET_BIT0 33 34 #define clr_SMOD PCON &= ~SET_BIT7 35 #define clr_SMOD0 PCON &= ~SET_BIT6 36 #define clr_POF PCON &= ~SET_BIT4 37 #define clr_GF1 PCON &= ~SET_BIT3 38 #define clr_GF0 PCON &= ~SET_BIT2 39 #define clr_PD PCON &= ~SET_BIT1 40 #define clr_IDL PCON &= ~SET_BIT0 41 42 /**** TCON 88H ****/ 43 #define set_TF1 TF1 = 1 44 #define set_TR1 TR1 = 1 45 #define set_TF0 TF0 = 1 46 #define set_TR0 TR0 = 1 //启动定时器0(定时器0启动控制,0定时器0终止,清除该位将终止定时器0并且当前计数值将保存到TH0和TL0中,1使能定时器0) 47 #define set_IE1 IE1 = 1 48 #define set_IT1 IT1 = 1 49 #define set_IE0 IE0 = 1 50 #define set_IT0 IT0 = 1 51 52 #define clr_TF1 TF1 = 0 53 #define clr_TR1 TR1 = 0 54 #define clr_TF0 TF0 = 0 55 #define clr_TR0 TR0 = 0 56 #define clr_IE1 IE1 = 0 57 #define clr_IT1 IT1 = 0 58 #define clr_IE0 IE0 = 0 59 #define clr_IT0 IT0 = 0 60 61 //**** TMOD 89H **** 62 #define set_GATE_T1 TMOD |= SET_BIT7 63 #define set_CT_T1 TMOD |= SET_BIT6 64 #define set_M1_T1 TMOD |= SET_BIT5 65 #define set_M0_T1 TMOD |= SET_BIT4 66 #define set_GATE_T0 TMOD |= SET_BIT3 67 #define set_CT_T0 TMOD |= SET_BIT2 68 #define set_M1_T0 TMOD |= SET_BIT1 69 #define set_M0_T0 TMOD |= SET_BIT0 70 71 #define clr_GATE_T1 TMOD &= ~SET_BIT7 72 #define clr_CT_T1 TMOD &= ~SET_BIT6 73 #define clr_M1_T1 TMOD &= ~SET_BIT5 74 #define clr_M0_T1 TMOD &= ~SET_BIT4 75 #define clr_GATE_T0 TMOD &= ~SET_BIT3 76 #define clr_CT_T0 TMOD &= ~SET_BIT2 77 #define clr_M1_T0 TMOD &= ~SET_BIT1 78 #define clr_M0_T0 TMOD &= ~SET_BIT0 79 80 //**** TH1 8AH **** 81 //**** TH0 8BH **** 82 //**** TL1 8CH **** 83 //**** TL0 8DH **** 84 85 //CKCON - 8EH 时钟控制寄存器 86 #define set_PWMCKS CKCON |= SET_BIT6 //设置pwm时钟源为定时器1的溢出(0为系统时钟,1为定时器1的溢出) 87 #define set_T1M CKCON |= SET_BIT4 //设置定时器1的时钟为系统时钟(0为1/12系统时钟,与8051兼容,1为选择时钟源为系统时钟) 88 #define set_T0M CKCON |= SET_BIT3 //设置定时器0的时钟为系统时钟(0为1/12系统时钟,与8051兼容,1为选择时钟源为系统时钟) 89 #define set_CLOEN CKCON |= SET_BIT1 //设置系统时钟输出使能,从PLO(P1.1)输出(0禁用系统时钟输出,1使系统时钟创覲LO(P1.1)输出) 90 //清除时钟 91 #define clr_PWMCKS CKCON &= ~SET_BIT6 //设置pwm时钟源为系统时钟(0为系统时钟,1为定时器1的溢出) 92 #define clr_T1M CKCON &= ~SET_BIT4 //设置定时器1的时钟为1/12系统时钟(0为1/12系统时钟,与8051兼容,1为选择时钟源为系统时钟) 93 #define clr_T0M CKCON &= ~SET_BIT3 //设置定时器0的时钟为1/12系统时钟(0为1/12系统时钟,与8051兼容,1为选择时钟源为系统时钟) 94 #define clr_CLOEN CKCON &= ~SET_BIT1 //设置系统时钟输出使能,禁用系统时钟输出(0禁用系统时钟输出,1使系统时钟创覲LO(P1.1)输出) 95 96 //**** WKCON 8FH **** 97 #define set_WKTCK WKCON |= SET_BIT5 98 #define set_WKTF WKCON |= SET_BIT4 99 #define set_WKTR WKCON |= SET_BIT3 100 #define set_WKPS2 WKCON |= SET_BIT2 101 #define set_WKPS1 WKCON |= SET_BIT1 102 #define set_WKPS0 WKCON |= SET_BIT0 103 104 #define clr_WKTCK WKCON &= ~SET_BIT5 105 #define clr_WKTF WKCON &= ~SET_BIT4 106 #define clr_WKTR WKCON &= ~SET_BIT3 107 #define clr_WKPS2 WKCON &= ~SET_BIT2 108 #define clr_WKPS1 WKCON &= ~SET_BIT1 109 #define clr_WKPS0 WKCON &= ~SET_BIT0 110 111 /**** P1 90H *****/ 112 #define set_P10 P10 = 1 113 #define set_P11 P11 = 1 114 #define set_P12 P12 = 1 115 #define set_P13 P13 = 1 116 #define set_P14 P14 = 1 117 #define set_P15 P15 = 1 118 #define set_P16 P16 = 1 119 #define set_P17 P17 = 1 120 121 #define clr_P10 P10 = 0 122 #define clr_P11 P11 = 0 123 #define clr_P12 P12 = 0 124 #define clr_P13 P13 = 0 125 #define clr_P14 P14 = 0 126 #define clr_P15 P15 = 0 127 #define clr_P16 P16 = 0 128 #define clr_P17 P17 = 0 129 130 //****SFRS 91H **** 131 #define set_SFRPAGE BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;SFRS|=SET_BIT0;EA=BIT_TMP 132 #define clr_SFRPAGE BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;SFRS&=~SET_BIT0;EA=BIT_TMP 133 134 //****CAPCON0 92H **** 135 #define set_CAPEN2 CAPCON0 |= SET_BIT6 136 #define set_CAPEN1 CAPCON0 |= SET_BIT5 137 #define set_CAPEN0 CAPCON0 |= SET_BIT4 138 #define set_CAPF2 CAPCON0 |= SET_BIT2 139 #define set_CAPF1 CAPCON0 |= SET_BIT1 140 #define set_CAPF0 CAPCON0 |= SET_BIT0 141 142 #define clr_CAPEN2 CAPCON0 &= ~SET_BIT6 143 #define clr_CAPEN1 CAPCON0 &= ~SET_BIT5 144 #define clr_CAPEN0 CAPCON0 &= ~SET_BIT4 145 #define clr_CAPF2 CAPCON0 &= ~SET_BIT2 146 #define clr_CAPF1 CAPCON0 &= ~SET_BIT1 147 #define clr_CAPF0 CAPCON0 &= ~SET_BIT0 148 149 //**** CAPCON1 93H **** 150 #define set_CAP2LS1 CAPCON1 |= SET_BIT5 151 #define set_CAP2LS0 CAPCON1 |= SET_BIT4 152 #define set_CAP1LS1 CAPCON1 |= SET_BIT3 153 #define set_CAP1LS0 CAPCON1 |= SET_BIT2 154 #define set_CAP0LS1 CAPCON1 |= SET_BIT1 155 #define set_CAP0LS0 CAPCON1 |= SET_BIT0 156 157 #define clr_CAP2LS1 CAPCON1 &= ~SET_BIT5 158 #define clr_CAP2LS0 CAPCON1 &= ~SET_BIT4 159 #define clr_CAP1LS1 CAPCON1 &= ~SET_BIT3 160 #define clr_CAP1LS0 CAPCON1 &= ~SET_BIT2 161 #define clr_CAP0LS1 CAPCON1 &= ~SET_BIT1 162 #define clr_CAP0LS0 CAPCON1 &= ~SET_BIT0 163 164 //**** CAPCON2 94H **** 165 #define set_ENF2 CAPCON2 |= SET_BIT6 166 #define set_ENF1 CAPCON2 |= SET_BIT5 167 #define set_ENF0 CAPCON2 |= SET_BIT4 168 169 #define clr_ENF2 CAPCON2 &= ~SET_BIT6 170 #define clr_ENF1 CAPCON2 &= ~SET_BIT5 171 #define clr_ENF0 CAPCON2 &= ~SET_BIT4 172 173 //**** CKDIV 95H **** 174 175 //**** CKSWT 96H **** TA protect register 176 #define set_HIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT5;EA=BIT_TMP; 177 #define set_LIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT4;EA=BIT_TMP; 178 #define set_ECLKST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT3;EA=BIT_TMP; 179 #define set_OSC1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT2;EA=BIT_TMP; 180 #define set_OSC0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT|=SET_BIT1;EA=BIT_TMP; 181 182 #define clr_HIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT5;EA=BIT_TMP; 183 #define clr_LIRCST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT4;EA=BIT_TMP; 184 #define clr_ECLKST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT3;EA=BIT_TMP; 185 #define clr_OSC1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT2;EA=BIT_TMP; 186 #define clr_OSC0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKSWT&=~SET_BIT1;EA=BIT_TMP; 187 188 //**** CKEN 97H **** TA protect register 189 #define set_EXTEN1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN|=SET_BIT7;EA=BIT_TMP; 190 #define set_EXTEN0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN|=SET_BIT6;EA=BIT_TMP; 191 #define set_HIRCEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN|=SET_BIT5;EA=BIT_TMP; 192 #define set_CKSWTF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN|=SET_BIT0;EA=BIT_TMP; 193 194 #define clr_EXTEN1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN&=~SET_BIT7;EA=BIT_TMP; 195 #define clr_EXTEN0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN&=~SET_BIT6;EA=BIT_TMP; 196 #define clr_HIRCEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN&=~SET_BIT5;EA=BIT_TMP; 197 #define clr_CKSWTF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CKEN&=~SET_BIT0;EA=BIT_TMP; 198 199 //**** SCON 98H **** 200 #define set_FE FE = 1 201 #define set_SM1 SM1 = 1 202 #define set_SM2 SM2 = 1 203 #define set_REN REN = 1 204 #define set_TB8 TB8 = 1 205 #define set_RB8 RB8 = 1 206 #define set_TI TI = 1 207 #define set_RI RI = 1 208 209 #define clr_FE FE = 0 210 #define clr_SM1 SM1 = 0 211 #define clr_SM2 SM2 = 0 212 #define clr_REN REN = 0 213 #define clr_TB8 TB8 = 0 214 #define clr_RB8 RB8 = 0 215 #define clr_TI TI = 0 216 #define clr_RI RI = 0 217 218 //**** SBUF 99H **** 219 //**** SBUF_1 9AH **** 220 221 //**** EIE 9BH **** 222 #define set_ET2 EIE |= SET_BIT7 223 #define set_ESPI EIE |= SET_BIT6 224 #define set_EFB EIE |= SET_BIT5 225 #define set_EWDT EIE |= SET_BIT4 226 #define set_EPWM EIE |= SET_BIT3 227 #define set_ECAP EIE |= SET_BIT2 228 #define set_EPI EIE |= SET_BIT1 229 #define set_EI2C EIE |= SET_BIT0 230 231 #define clr_ET2 EIE &= ~SET_BIT7 232 #define clr_ESPI EIE &= ~SET_BIT6 233 #define clr_EFB EIE &= ~SET_BIT5 234 #define clr_EWDT EIE &= ~SET_BIT4 235 #define clr_EPWM EIE &= ~SET_BIT3 236 #define clr_ECAP EIE &= ~SET_BIT2 237 #define clr_EPI EIE &= ~SET_BIT1 238 #define clr_EI2C EIE &= ~SET_BIT0 239 240 //**** EIE1 9CH **** 241 #define set_EWKT EIE1 |= SET_BIT2 242 #define set_ET3 EIE1 |= SET_BIT1 243 #define set_ES_1 EIE1 |= SET_BIT0 244 245 #define clr_EWKT EIE1 &= ~SET_BIT2 246 #define clr_ET3 EIE1 &= ~SET_BIT1 247 #define clr_ES_1 EIE1 &= ~SET_BIT0 248 249 //**** CHPCON 9DH **** TA protect register 250 #define set_SWRST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON|=SET_BIT7 ;EA=BIT_TMP 251 #define set_IAPFF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON|=SET_BIT6 ;EA=BIT_TMP 252 #define set_BS BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON|=SET_BIT1 ;EA=BIT_TMP 253 #define set_IAPEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON|=SET_BIT0 ;EA=BIT_TMP 254 255 #define clr_SWRST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON&=~SET_BIT7;EA=BIT_TMP 256 #define clr_IAPFF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON&=~SET_BIT6;EA=BIT_TMP 257 #define clr_BS BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON&=~SET_BIT1;EA=BIT_TMP 258 #define clr_IAPEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;CHPCON&=~SET_BIT0;EA=BIT_TMP 259 260 //**** P2 A0H **** 261 262 //**** AUXR1 A2H **** 263 #define set_SWRF AUXR1 |= SET_BIT7 264 #define set_RSTPINF AUXR1 |= SET_BIT6 265 #define set_HARDF AUXR1 |= SET_BIT5 266 #define set_GF2 AUXR1 |= SET_BIT3 267 #define set_UART0PX AUXR1 |= SET_BIT2 268 #define set_DPS AUXR1 |= SET_BIT0 269 270 #define clr_SWRF AUXR1 &= ~SET_BIT7 271 #define clr_RSTPINF AUXR1 &= ~SET_BIT6 272 #define clr_HARDF AUXR1 &= ~SET_BIT5 273 #define clr_GF2 AUXR1 &= ~SET_BIT3 274 #define clr_UART0PX AUXR1 &= ~SET_BIT2 275 #define clr_DPS AUXR1 &= ~SET_BIT0 276 277 //**** BODCON0 A3H **** TA protect register 278 #define set_BODEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT7;EA=BIT_TMP 279 #define set_BOV2 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT6;EA=BIT_TMP 280 #define set_BOV1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT5;EA=BIT_TMP 281 #define set_BOV0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT4;EA=BIT_TMP 282 #define set_BOF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT3;EA=BIT_TMP 283 #define set_BORST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT2;EA=BIT_TMP 284 #define set_BORF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT1;EA=BIT_TMP 285 #define set_BOS BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0|=SET_BIT0;EA=BIT_TMP 286 287 #define clr_BODEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT7;EA=BIT_TMP 288 #define clr_BOV2 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT6;EA=BIT_TMP 289 #define clr_BOV1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT5;EA=BIT_TMP 290 #define clr_BOV0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT4;EA=BIT_TMP 291 #define clr_BOF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT3;EA=BIT_TMP 292 #define clr_BORST BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT2;EA=BIT_TMP 293 #define clr_BORF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT1;EA=BIT_TMP 294 #define clr_BOS BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON0&=~SET_BIT0;EA=BIT_TMP 295 296 //**** IAPTRG A4H **** TA protect register 297 #define set_IAPGO BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPTRG|=SET_BIT0 ;EA=BIT_TMP 298 #define clr_IAPGO BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPTRG&=~SET_BIT0;EA=BIT_TMP 299 300 //**** IAPUEN A5H **** TA protect register 301 #define set_CFUEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPUEN|=SET_BIT2;EA=BIT_TMP 302 #define set_LDUEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPUEN|=SET_BIT1;EA=BIT_TMP 303 #define set_APUEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPUEN|=SET_BIT0;EA=BIT_TMP 304 305 #define clr_CFUEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPUEN&=~SET_BIT2;EA=BIT_TMP 306 #define clr_LDUEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPUEN&=~SET_BIT1;EA=BIT_TMP 307 #define clr_APUEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;IAPUEN&=~SET_BIT0;EA=BIT_TMP 308 309 //**** IAPAL A6H **** 310 //**** IAPAH A7H **** 311 312 //IE A8H 中断时能寄存器 313 #define set_EA EA = 1 //使能开启所有中断(0禁止所有中断,1每个中断使能依靠使能单独中断将会产生相应的单个中断) 314 #define set_EADC EADC = 1 //使能开启ADC中断(0禁止ADC中断,1使能由ADCF(ADCCON0.7)产生中断) 315 #define set_EBOD EBOD = 1 //使能开启BOD中段(0禁止BOD中断,1使能有BOD(BODCON0.3)产生中断) 316 #define set_ES ES = 1 //使能开启串口0中断(0禁止串口0中断,1使能由T1(SCON.1)或RI(SCON.0)中断) 317 #define set_ET1 ET1 = 1 318 #define set_EX1 EX1 = 1 319 #define set_ET0 ET0 = 1 //使能定时器0中断(0禁止定时器0中断,1使能由TF0(TCON.5)产生中断) 320 #define set_EX0 EX0 = 1 321 322 #define clr_EA EA = 0 323 #define clr_EADC EADC = 0 324 #define clr_EBOD EBOD = 0 325 #define clr_ES ES = 0 326 #define clr_ET1 ET1 = 0 327 #define clr_EX1 EX1 = 0 328 #define clr_ET0 ET0 = 0 329 #define clr_EX0 EX0 = 0 330 331 //**** SADDR A9H **** 332 333 //**** WDCON AAH **** TA protect register 334 #define set_WDTR BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT7;EA=BIT_TMP; 335 #define set_WDCLR BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT6;EA=BIT_TMP; 336 #define set_WDTF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT5;EA=BIT_TMP; 337 #define set_WIDPD BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT4;EA=BIT_TMP; 338 #define set_WDTRF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT3;EA=BIT_TMP; 339 #define set_WPS2 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT2;EA=BIT_TMP; 340 #define set_WPS1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT1;EA=BIT_TMP; 341 #define set_WPS0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON|=SET_BIT0;EA=BIT_TMP; 342 343 #define clr_WDTEN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT7;EA=BIT_TMP; 344 #define clr_WDCLR BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT6;EA=BIT_TMP; 345 #define clr_WDTF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT5;EA=BIT_TMP; 346 #define clr_WDTRF BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT3;EA=BIT_TMP; 347 #define clr_WPS2 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT2;EA=BIT_TMP; 348 #define clr_WPS1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT1;EA=BIT_TMP; 349 #define clr_WPS0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;WDCON&=~SET_BIT0;EA=BIT_TMP; 350 351 //**** BODCON1 ABH **** TA protect register 352 #define set_LPBOD1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON1|=SET_BIT2 ;EA=BIT_TMP; 353 #define set_LPBOD0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON1|=SET_BIT1 ;EA=BIT_TMP; 354 #define set_BODFLT BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON1|=SET_BIT0 ;EA=BIT_TMP; 355 356 #define clr_LPBOD1 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON1&=~SET_BIT2;EA=BIT_TMP; 357 #define clr_LPBOD0 BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON1&=~SET_BIT1;EA=BIT_TMP; 358 #define clr_BODFLT BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;BODCON1&=~SET_BIT0;EA=BIT_TMP; 359 360 361 //**** P3M1 ACH PAGE0 **** 362 #define set_P3M1_0 P3M1 |= SET_BIT0 363 #define clr_P3M1_0 P3M1 &= ~SET_BIT0 364 365 //**** P3S ACH PAGE1 **** SFRS must set as 1 to modify this register 366 #define set_P3S_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P3S|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 367 #define clr_P3S_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P3S&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 368 369 //**** P3M2 ADH PAGE0 **** 370 #define set_P3M2_0 P3M2 |= SET_BIT0 371 #define clr_P3M2_0 P3M2 &= ~SET_BIT0 372 373 //**** P3SR ADH PAGE1 **** SFRS must set as 1 to modify this register 374 #define set_P3SR_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P3SR|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 375 #define clr_P3SR_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P3SR&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 376 377 //**** IAPFD AEH **** 378 379 //**** IAPCN AFH **** 380 #define set_FOEN IAPN |= SET_BIT5 381 #define set_FCEN IAPN |= SET_BIT4 382 #define set_FCTRL3 IAPN |= SET_BIT3 383 #define set_FCTRL2 IAPN |= SET_BIT2 384 #define set_FCTRL1 IAPN |= SET_BIT1 385 #define set_FCTRL0 IAPN |= SET_BIT0 386 387 #define clr_FOEN IAPN &= ~SET_BIT5 388 #define clr_FCEN IAPN &= ~SET_BIT4 389 #define clr_FCTRL3 IAPN &= ~SET_BIT3 390 #define clr_FCTRL2 IAPN &= ~SET_BIT2 391 #define clr_FCTRL1 IAPN &= ~SET_BIT1 392 #define clr_FCTRL0 IAPN &= ~SET_BIT0 393 394 //**** P3 B0H **** 395 #define set_P30 P30 = 1 396 #define clr_P30 P30 = 0 397 398 //**** P0M1 B1H PAGE0 **** 399 #define set_P0M1_7 P0M1 |= SET_BIT7 400 #define set_P0M1_6 P0M1 |= SET_BIT6 401 #define set_P0M1_5 P0M1 |= SET_BIT5 402 #define set_P0M1_4 P0M1 |= SET_BIT4 403 #define set_P0M1_3 P0M1 |= SET_BIT3 404 #define set_P0M1_2 P0M1 |= SET_BIT2 405 #define set_P0M1_1 P0M1 |= SET_BIT1 406 #define set_P0M1_0 P0M1 |= SET_BIT0 407 408 #define clr_P0M1_7 P0M1 &= ~SET_BIT7 409 #define clr_P0M1_6 P0M1 &= ~SET_BIT6 410 #define clr_P0M1_5 P0M1 &= ~SET_BIT5 411 #define clr_P0M1_4 P0M1 &= ~SET_BIT4 412 #define clr_P0M1_3 P0M1 &= ~SET_BIT3 413 #define clr_P0M1_2 P0M1 &= ~SET_BIT2 414 #define clr_P0M1_1 P0M1 &= ~SET_BIT1 415 #define clr_P0M1_0 P0M1 &= ~SET_BIT0 416 417 //**** P0S B2H PAGE1 **** SFRS must set as 1 to modify this register 418 #define set_P0S_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 419 #define set_P0S_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 420 #define set_P0S_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 421 #define set_P0S_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 422 #define set_P0S_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 423 #define set_P0S_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 424 #define set_P0S_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 425 #define set_P0S_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 426 427 #define clr_P0S_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 428 #define clr_P0S_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 429 #define clr_P0S_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 430 #define clr_P0S_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 431 #define clr_P0S_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 432 #define clr_P0S_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 433 #define clr_P0S_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 434 #define clr_P0S_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0S&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 435 436 //**** P0M2 B2H PAGE0 **** 437 #define set_P0M2_7 P0M2 |= SET_BIT7 438 #define set_P0M2_6 P0M2 |= SET_BIT6 439 #define set_P0M2_5 P0M2 |= SET_BIT5 440 #define set_P0M2_4 P0M2 |= SET_BIT4 441 #define set_P0M2_3 P0M2 |= SET_BIT3 442 #define set_P0M2_2 P0M2 |= SET_BIT2 443 #define set_P0M2_1 P0M2 |= SET_BIT1 444 #define set_P0M2_0 P0M2 |= SET_BIT0 445 446 #define clr_P0M2_7 P0M2 &= ~SET_BIT7 447 #define clr_P0M2_6 P0M2 &= ~SET_BIT6 448 #define clr_P0M2_5 P0M2 &= ~SET_BIT5 449 #define clr_P0M2_4 P0M2 &= ~SET_BIT4 450 #define clr_P0M2_3 P0M2 &= ~SET_BIT3 451 #define clr_P0M2_2 P0M2 &= ~SET_BIT2 452 #define clr_P0M2_1 P0M2 &= ~SET_BIT1 453 #define clr_P0M2_0 P0M2 &= ~SET_BIT0 454 455 456 //**** P0SR B0H PAGE1 **** SFRS must set as 1 to modify this register 457 #define set_P0SR_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 458 #define set_P0SR_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 459 #define set_P0SR_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 460 #define set_P0SR_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 461 #define set_P0SR_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 462 #define set_P0SR_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 463 #define set_P0SR_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 464 #define set_P0SR_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 465 466 #define clr_P0SR_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 467 #define clr_P0SR_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 468 #define clr_P0SR_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 469 #define clr_P0SR_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 470 #define clr_P0SR_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 471 #define clr_P0SR_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 472 #define clr_P0SR_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 473 #define clr_P0SR_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P0SR&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 474 475 476 //**** P1M1 B3H PAGE0 **** 477 #define set_P1M1_7 P1M1 |= SET_BIT7 478 #define set_P1M1_6 P1M1 |= SET_BIT6 479 #define set_P1M1_5 P1M1 |= SET_BIT5 480 #define set_P1M1_4 P1M1 |= SET_BIT4 481 #define set_P1M1_3 P1M1 |= SET_BIT3 482 #define set_P1M1_2 P1M1 |= SET_BIT2 483 #define set_P1M1_1 P1M1 |= SET_BIT1 484 #define set_P1M1_0 P1M1 |= SET_BIT0 485 486 #define clr_P1M1_7 P1M1 &= ~SET_BIT7 487 #define clr_P1M1_6 P1M1 &= ~SET_BIT6 488 #define clr_P1M1_5 P1M1 &= ~SET_BIT5 489 #define clr_P1M1_4 P1M1 &= ~SET_BIT4 490 #define clr_P1M1_3 P1M1 &= ~SET_BIT3 491 #define clr_P1M1_2 P1M1 &= ~SET_BIT2 492 #define clr_P1M1_1 P1M1 &= ~SET_BIT1 493 #define clr_P1M1_0 P1M1 &= ~SET_BIT0 494 495 //**** P1S B3H PAGE1 **** SFRS must set as 1 to modify this register 496 #define set_P1S_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 497 #define set_P1S_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 498 #define set_P1S_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 499 #define set_P1S_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 500 #define set_P1S_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 501 #define set_P1S_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 502 #define set_P1S_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 503 #define set_P1S_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 504 505 #define clr_P1S_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 506 #define clr_P1S_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 507 #define clr_P1S_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 508 #define clr_P1S_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 509 #define clr_P1S_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 510 #define clr_P1S_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 511 #define clr_P1S_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 512 #define clr_P1S_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1S&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 513 514 //**** P1M2 B4H PAGE0 **** 515 #define set_P12UP P1M2 |= SET_BIT2 516 #define set_P1M2_1 P1M2 |= SET_BIT1 517 #define set_P1M2_0 P1M2 |= SET_BIT0 518 519 #define clr_P12UP P1M2 &= ~SET_BIT2 520 #define clr_P1M2_1 P1M2 &= ~SET_BIT1 521 #define clr_P1M2_0 P1M2 &= ~SET_BIT0 522 523 //**** P1SR B4H PAGE1 **** SFRS must set as 1 to modify this register 524 #define set_P1SR_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 525 #define set_P1SR_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 526 #define set_P1SR_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 527 #define set_P1SR_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 528 #define set_P1SR_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 529 #define set_P1SR_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 530 #define set_P1SR_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 531 #define set_P1SR_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 532 533 #define clr_P1SR_7 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT7;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 534 #define clr_P1SR_6 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT6;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 535 #define clr_P1SR_5 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 536 #define clr_P1SR_4 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 537 #define clr_P1SR_3 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 538 #define clr_P1SR_2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 539 #define clr_P1SR_1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 540 #define clr_P1SR_0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;P1SR&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 541 542 543 //**** P2S B5H **** 544 #define set_P2S_0 P2S |= SET_BIT0 545 #define clr_P2S_0 P2S &= ~SET_BIT0 546 547 //**** IPH B7H PAGE0 **** 548 #define set_PADCH IPH |= SET_BIT6 549 #define set_PBODH IPH |= SET_BIT5 550 #define set_PSH IPH |= SET_BIT4 551 #define set_PT1H IPH |= SET_BIT3 552 #define set_PX11 IPH |= SET_BIT2 553 #define set_PT0H IPH |= SET_BIT1 554 #define set_PX0H IPH |= SET_BIT0 555 556 #define clr_PADCH IPH &= ~SET_BIT6 557 #define clr_PBODH IPH &= ~SET_BIT5 558 #define clr_PSH IPH &= ~SET_BIT4 559 #define clr_PT1H IPH &= ~SET_BIT3 560 #define clr_PX11 IPH &= ~SET_BIT2 561 #define clr_PT0H IPH &= ~SET_BIT1 562 #define clr_PX0H IPH &= ~SET_BIT0 563 564 //**** PWMINTC B7H PAGE1 **** SFRS must set as 1 to modify this register 565 #define set_INTTYP1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC|=SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 566 #define set_INTTYP0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC|=SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 567 #define set_INTSEL2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC|=SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 568 #define set_INTSEL1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 569 #define set_INTSEL0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC|=SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 570 571 #define clr_INTTYP1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC&=~SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 572 #define clr_INTTYP0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC&=~SET_BIT4;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 573 #define clr_INTSEL2 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC&=~SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 574 #define clr_INTSEL1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 575 #define clr_INTSEL0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PWMINTC&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 576 577 //**** IP B8H **** 578 #define set_PADC PADC = 1 579 #define set_PBOD PBOD = 1 580 #define set_PS PS = 1 581 #define set_PT1 PT1 = 1 582 #define set_PX1 PX1 = 1 583 #define set_PT0 PT0 = 1 584 #define set_PX0 PX0 = 1 585 586 #define clr_PADC PADC = 0 587 #define clr_PBOD PBOD = 0 588 #define clr_PS PS = 0 589 #define clr_PT1 PT1 = 0 590 #define clr_PX1 PX1 = 0 591 #define clr_PT0 PT0 = 0 592 #define clr_PX0 PX0 = 0 593 594 //**** SADEN B9H **** 595 //**** SADEN_1 8AH **** 596 //**** SADDR_1 BBH **** 597 //**** I2DAT BCH **** 598 //**** I2STAT BDH **** 599 //**** I2CLK BEH **** 600 601 //**** I2TOC BFH **** 602 #define set_I2TOCEN I2TOC |= SET_BIT2 603 #define set_DIV I2TOC |= SET_BIT1 604 #define set_I2TOF I2TOC |= SET_BIT0 605 606 #define clr_I2TOCEN I2TOC &= ~SET_BIT2 607 #define clr_DIV I2TOC &= ~SET_BIT1 608 #define clr_I2TOF I2TOC &= ~SET_BIT0 609 610 //**** I2CON C0H **** 611 #define set_I2CEN I2CEN = 1 612 #define set_STA STA = 1 613 #define set_STO STO = 1 614 #define set_SI SI = 1 615 #define set_AA AA = 1 616 #define set_I2CPX I2CPX = 1 617 618 #define clr_I2CEN I2CEN = 0 619 #define clr_STA STA = 0 620 #define clr_STO STO = 0 621 #define clr_SI SI = 0 622 #define clr_AA AA = 0 623 #define clr_I2CPX I2CPX = 0 624 625 //**** I2ADDR C1H **** 626 #define set_GC I2ADDR |= SET_BIT0 627 #define clr_GC I2ADDR &= ~SET_BIT0 628 629 //**** ADCRL C2H **** 630 //**** ADCRH C3H **** 631 632 //**** T3CON C4H PAGE0 **** 633 #define set_SMOD_1 T3CON |= SET_BIT7 634 #define set_SMOD0_1 T3CON |= SET_BIT6 635 #define set_BRCK T3CON |= SET_BIT5 636 #define set_TF3 T3CON |= SET_BIT4 637 #define set_TR3 T3CON |= SET_BIT3 638 #define set_T3PS2 T3CON |= SET_BIT2 639 #define set_T3PS1 T3CON |= SET_BIT1 640 #define set_T3PS0 T3CON |= SET_BIT0 641 642 #define clr_SMOD_1 T3CON &= ~SET_BIT7 643 #define clr_SMOD0_1 T3CON &= ~SET_BIT6 644 #define clr_BRCK T3CON &= ~SET_BIT5 645 #define clr_TF3 T3CON &= ~SET_BIT4 646 #define clr_TR3 T3CON &= ~SET_BIT3 647 #define clr_T3PS2 T3CON &= ~SET_BIT2 648 #define clr_T3PS1 T3CON &= ~SET_BIT1 649 #define clr_T3PS0 T3CON &= ~SET_BIT0 650 651 //**** PWM4H C4H PAGE1 **** SFRS must set as 1 to modify this register 652 //**** RL3 C5H PAGE0 **** 653 //**** PWM5H C5H PAGE1 **** SFRS must set as 1 to modify this register 654 //**** RH3 C6H PAGE0 **** 655 656 //**** PIOCON1 C6H PAGE1 **** SFRS must set as 1 to modify this register 657 #define set_PIO15 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1|=SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 658 #define set_PIO13 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1|=SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 659 #define set_PIO12 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1|=SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 660 #define set_PIO11 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 661 662 #define clr_PIO15 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1&=~SET_BIT5;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 663 #define clr_PIO13 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1&=~SET_BIT3;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 664 #define clr_PIO12 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1&=~SET_BIT2;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 665 #define clr_PIO11 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;PIOCON1&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 666 667 //**** T2CON C8H **** 668 #define set_TF2 TF2 = 1 669 #define set_TR2 TR2 = 1 670 #define set_CMRL2 CMRL2 = 1 671 672 #define clr_TF2 TF2 = 0 673 #define clr_TR2 TR2 = 0 674 #define clr_CMRL2 CMRL2 = 0 675 676 //**** T2MOD C9H **** 677 #define set_LDEN T2MOD |= SET_BIT7 678 #define set_T2DIV2 T2MOD |= SET_BIT6 679 #define set_T2DIV1 T2MOD |= SET_BIT5 680 #define set_T2DIV0 T2MOD |= SET_BIT4 681 #define set_CAPCR T2MOD |= SET_BIT3 682 #define set_CMPCR T2MOD |= SET_BIT2 683 #define set_LDTS1 T2MOD |= SET_BIT1 684 #define set_LDTS0 T2MOD |= SET_BIT0 685 686 #define clr_LDEN T2MOD &= ~SET_BIT7 687 #define clr_T2DIV2 T2MOD &= ~SET_BIT6 688 #define clr_T2DIV1 T2MOD &= ~SET_BIT5 689 #define clr_T2DIV0 T2MOD &= ~SET_BIT4 690 #define clr_CAPCR T2MOD &= ~SET_BIT3 691 #define clr_CMPCR T2MOD &= ~SET_BIT2 692 #define clr_LDTS1 T2MOD &= ~SET_BIT1 693 #define clr_LDTS0 T2MOD &= ~SET_BIT0 694 695 //**** RCMP2H CAH **** 696 //**** RCMP2L CBH **** 697 //**** TL2 CCH PAGE0 **** 698 //**** PWM4L CCH PAGE1 **** SFRS must set as 1 to modify this register 699 //**** TH2 CDH PAGE0 **** 700 //**** PWM5L CDH PAGE1 **** SFRS must set as 1 to modify this register 701 //**** ADCMPL CEH **** 702 //**** ADCMPH CFH **** 703 704 /**** PSW D0H ****/ 705 #define set_CY CY = 1 706 #define set_AC AC = 1 707 #define set_F0 F0 = 1 708 #define set_RS1 RS1 = 1 709 #define set_RS0 RS0 = 1 710 #define set_OV OV = 1 711 #define set_P P = 1 712 713 #define clr_CY CY = 0 714 #define clr_AC AC = 0 715 #define clr_F0 F0 = 0 716 #define clr_RS1 RS1 = 0 717 #define clr_RS0 RS0 = 0 718 #define clr_OV OV = 0 719 #define clr_P P = 0 720 721 //**** PWMPH D1H **** 722 //**** PWM0H D2H **** 723 //**** PWM1H D3H **** 724 //**** PWM2H D4H **** 725 //**** PWM3H D5H **** 726 727 //**** PNP D6H **** 728 #define set_PNP5 PNP |= SET_BIT5 729 #define set_PNP4 PNP |= SET_BIT4 730 #define set_PNP3 PNP |= SET_BIT3 731 #define set_PNP2 PNP |= SET_BIT2 732 #define set_PNP1 PNP |= SET_BIT1 733 #define set_PNP0 PNP |= SET_BIT0 734 735 #define clr_PNP5 PNP &= ~SET_BIT5 736 #define clr_PNP4 PNP &= ~SET_BIT4 737 #define clr_PNP3 PNP &= ~SET_BIT3 738 #define clr_PNP2 PNP &= ~SET_BIT2 739 #define clr_PNP1 PNP &= ~SET_BIT1 740 #define clr_PNP0 PNP &= ~SET_BIT0 741 742 //**** FBD D7H **** 743 #define set_FBF FBD |= SET_BIT7 744 #define set_FBINLS FBD |= SET_BIT6 745 #define set_FBD5 FBD |= SET_BIT5 746 #define set_FBD4 FBD |= SET_BIT4 747 #define set_FBD3 FBD |= SET_BIT3 748 #define set_FBD2 FBD |= SET_BIT2 749 #define set_FBD1 FBD |= SET_BIT1 750 #define set_FBD0 FBD |= SET_BIT0 751 752 #define clr_FBF FBD &= ~SET_BIT7 753 #define clr_FBINLS FBD &= ~SET_BIT6 754 #define clr_FBD5 FBD &= ~SET_BIT5 755 #define clr_FBD4 FBD &= ~SET_BIT4 756 #define clr_FBD3 FBD &= ~SET_BIT3 757 #define clr_FBD2 FBD &= ~SET_BIT2 758 #define clr_FBD1 FBD &= ~SET_BIT1 759 #define clr_FBD0 FBD &= ~SET_BIT0 760 761 /**** PWMCON0 D8H ****/ 762 #define set_PWMRUN PWMRUN = 1 //运行PWM使能 763 #define set_LOAD LOAD = 1 //写:更新PWM值(本次结束更新),读:(导入新的pwm没有完成) 764 #define set_PWMF PWMF = 1 // 765 #define set_CLRPWM CLRPWM = 1 //写:清空pwm寄存器,读:PWM 16位计数器内还有数值,未清零 766 767 #define clr_PWMRUN PWMRUN = 0 //关闭PWM使能 768 #define clr_LOAD LOAD = 0 //写:=导入新周期和占空比已经完成,读:=当前一个PWM周期输出结束,载入动作才会开始 769 #define clr_PWMF PWMF = 0 // 770 #define clr_CLRPWM CLRPWM = 0 //写: 无动作,读: PWM 16位计数器已清零 771 772 //**** PWMPL D9H **** 773 //**** PWM0L DAH **** 774 //**** PWM1L DBH **** 775 //**** PWM2L DCH **** 776 //**** PWM3L DDH **** 777 778 //**** PIOCON0 DEH **** 779 #define set_PIO05 PIOCON0 |= SET_BIT5 780 #define set_PIO04 PIOCON0 |= SET_BIT4 781 #define set_PIO03 PIOCON0 |= SET_BIT3 782 #define set_PIO02 PIOCON0 |= SET_BIT2 783 #define set_PIO01 PIOCON0 |= SET_BIT1 784 #define set_PIO00 PIOCON0 |= SET_BIT0 785 786 #define clr_PIO05 PIOCON0 &= ~SET_BIT5 787 #define clr_PIO04 PIOCON0 &= ~SET_BIT4 788 #define clr_PIO03 PIOCON0 &= ~SET_BIT3 789 #define clr_PIO02 PIOCON0 &= ~SET_BIT2 790 #define clr_PIO01 PIOCON0 &= ~SET_BIT1 791 #define clr_PIO00 PIOCON0 &= ~SET_BIT0 792 793 //**** PWMCON1 DFH **** 794 #define set_PWMMOD1 PWMCON1 |= SET_BIT7 795 #define set_PWMMOD0 PWMCON1 |= SET_BIT6 796 #define set_GP PWMCON1 |= SET_BIT5 797 #define set_PWMTYP PWMCON1 |= SET_BIT4 798 #define set_FBINEN PWMCON1 |= SET_BIT3 799 #define set_PWMDIV2 PWMCON1 |= SET_BIT2 800 #define set_PWMDIV1 PWMCON1 |= SET_BIT1 801 #define set_PWMDIV0 PWMCON1 |= SET_BIT0 802 803 #define clr_PWMMOD1 PWMCON1 &= ~SET_BIT7 804 #define clr_PWMMOD0 PWMCON1 &= ~SET_BIT6 805 #define clr_GP PWMCON1 &= ~SET_BIT5 806 #define clr_PWMTYP PWMCON1 &= ~SET_BIT4 807 #define clr_FBINEN PWMCON1 &= ~SET_BIT3 808 #define clr_PWMDIV2 PWMCON1 &= ~SET_BIT2 809 #define clr_PWMDIV1 PWMCON1 &= ~SET_BIT1 810 #define clr_PWMDIV0 PWMCON1 &= ~SET_BIT0 811 812 //**** ACC E0H **** 813 814 //**** ADCCON1 E1H **** 815 #define set_STADCPX ADCCON1 |= SET_BIT6 816 #define set_ETGTYP1 ADCCON1 |= SET_BIT3 817 #define set_ETGTYP0 ADCCON1 |= SET_BIT2 818 #define set_ADCEX ADCCON1 |= SET_BIT1 819 #define set_ADCEN ADCCON1 |= SET_BIT0 820 821 #define clr_STADCPX ADCCON1 &= ~SET_BIT6 822 #define clr_ETGTYP1 ADCCON1 &= ~SET_BIT3 823 #define clr_ETGTYP0 ADCCON1 &= ~SET_BIT2 824 #define clr_ADCEX ADCCON1 &= ~SET_BIT1 825 #define clr_ADCEN ADCCON1 &= ~SET_BIT0 826 827 //**** ADCON2 E2H **** 828 #define set_ADFBEN ADCCON2 |= SET_BIT7 829 #define set_ADCMPOP ADCCON2 |= SET_BIT6 830 #define set_ADCMPEN ADCCON2 |= SET_BIT5 831 #define set_ADCMPO ADCCON2 |= SET_BIT4 832 833 #define clr_ADFBEN ADCCON2 &= ~SET_BIT7 834 #define clr_ADCMPOP ADCCON2 &= ~SET_BIT6 835 #define clr_ADCMPEN ADCCON2 &= ~SET_BIT5 836 #define clr_ADCMPO ADCCON2 &= ~SET_BIT4 837 838 //**** ADCDLY E3H **** 839 //**** C0L E4H **** 840 //**** C0H E5H **** 841 //**** C1L E6H **** 842 //**** C1H E7H **** 843 844 //**** ADCCON0 EAH **** 845 #define set_ADCF ADCF = 1 846 #define set_ADCS ADCS = 1 847 #define set_ETGSEL1 ETGSEL1 = 1 848 #define set_ETGSEL0 ETGSEL0 = 1 849 #define set_ADCHS3 ADCHS3 = 1 850 #define set_ADCHS2 ADCHS2 = 1 851 #define set_ADCHS1 ADCHS1 = 1 852 #define set_ADCHS0 ADCHS0 = 1 853 854 #define clr_ADCF ADCF = 0 855 #define clr_ADCS ADCS = 0 856 #define clr_ETGSEL1 ETGSEL1 = 0 857 #define clr_ETGSEL0 ETGSEL0 = 0 858 #define clr_ADCHS3 ADCHS3 = 0 859 #define clr_ADCHS2 ADCHS2 = 0 860 #define clr_ADCHS1 ADCHS1 = 0 861 #define clr_ADCHS0 ADCHS0 = 0 862 863 //**** PICON E9H **** 864 #define set_PIT67 PICON |= SET_BIT7 865 #define set_PIT45 PICON |= SET_BIT6 866 #define set_PIT3 PICON |= SET_BIT5 867 #define set_PIT2 PICON |= SET_BIT4 868 #define set_PIT1 PICON |= SET_BIT3 869 #define set_PIT0 PICON |= SET_BIT2 870 #define set_PIPS1 PICON |= SET_BIT1 871 #define set_PIPS0 PICON |= SET_BIT0 872 873 #define clr_PIT67 PICON &= ~SET_BIT7 874 #define clr_PIT45 PICON &= ~SET_BIT6 875 #define clr_PIT3 PICON &= ~SET_BIT5 876 #define clr_PIT2 PICON &= ~SET_BIT4 877 #define clr_PIT1 PICON &= ~SET_BIT3 878 #define clr_PIT0 PICON &= ~SET_BIT2 879 #define clr_PIPS1 PICON &= ~SET_BIT1 880 #define clr_PIPS0 PICON &= ~SET_BIT0 881 882 //**** PINEN EAH **** 883 #define set_PINEN7 PINEN |= SET_BIT7 884 #define set_PINEN6 PINEN |= SET_BIT6 885 #define set_PINEN5 PINEN |= SET_BIT5 886 #define set_PINEN4 PINEN |= SET_BIT4 887 #define set_PINEN3 PINEN |= SET_BIT3 888 #define set_PINEN2 PINEN |= SET_BIT2 889 #define set_PINEN1 PINEN |= SET_BIT1 890 #define set_PINEN0 PINEN |= SET_BIT0 891 892 #define clr_PINEN7 PINEN &= ~SET_BIT7 893 #define clr_PINEN6 PINEN &= ~SET_BIT6 894 #define clr_PINEN5 PINEN &= ~SET_BIT5 895 #define clr_PINEN4 PINEN &= ~SET_BIT4 896 #define clr_PINEN3 PINEN &= ~SET_BIT3 897 #define clr_PINEN2 PINEN &= ~SET_BIT2 898 #define clr_PINEN1 PINEN &= ~SET_BIT1 899 #define clr_PINEN0 PINEN &= ~SET_BIT0 900 901 //**** PIPEN EBH **** 902 #define set_PIPEN7 PIPEN |= SET_BIT7 903 #define set_PIPEN6 PIPEN |= SET_BIT6 904 #define set_PIPEN5 PIPEN |= SET_BIT5 905 #define set_PIPEN4 PIPEN |= SET_BIT4 906 #define set_PIPEN3 PIPEN |= SET_BIT3 907 #define set_PIPEN2 PIPEN |= SET_BIT2 908 #define set_PIPEN1 PIPEN |= SET_BIT1 909 #define set_PIPEN0 PIPEN |= SET_BIT0 910 911 #define clr_PIPEN7 PIPEN &= ~SET_BIT7 912 #define clr_PIPEN6 PIPEN &= ~SET_BIT6 913 #define clr_PIPEN5 PIPEN &= ~SET_BIT5 914 #define clr_PIPEN4 PIPEN &= ~SET_BIT4 915 #define clr_PIPEN3 PIPEN &= ~SET_BIT3 916 #define clr_PIPEN2 PIPEN &= ~SET_BIT2 917 #define clr_PIPEN1 PIPEN &= ~SET_BIT1 918 #define clr_PIPEN0 PIPEN &= ~SET_BIT0 919 920 //**** PIF ECH **** 921 #define set_PIF7 PIF |= SET_BIT7 922 #define set_PIF6 PIF |= SET_BIT6 923 #define set_PIF5 PIF |= SET_BIT5 924 #define set_PIF4 PIF |= SET_BIT4 925 #define set_PIF3 PIF |= SET_BIT3 926 #define set_PIF2 PIF |= SET_BIT2 927 #define set_PIF1 PIF |= SET_BIT1 928 #define set_PIF0 PIF |= SET_BIT0 929 930 #define clr_PIF7 PIF &= ~SET_BIT7 931 #define clr_PIF6 PIF &= ~SET_BIT6 932 #define clr_PIF5 PIF &= ~SET_BIT5 933 #define clr_PIF4 PIF &= ~SET_BIT4 934 #define clr_PIF3 PIF &= ~SET_BIT3 935 #define clr_PIF2 PIF &= ~SET_BIT2 936 #define clr_PIF1 PIF &= ~SET_BIT1 937 #define clr_PIF0 PIF &= ~SET_BIT0 938 939 //**** C2L EDH **** 940 //**** C2H EEH **** 941 942 //**** EIP EFH **** 943 #define set_PT2 EIP |= SET_BIT7 944 #define set_PSPI EIP |= SET_BIT6 945 #define set_PFB EIP |= SET_BIT5 946 #define set_PWDT EIP |= SET_BIT4 947 #define set_PPWM EIP |= SET_BIT3 948 #define set_PCAP EIP |= SET_BIT2 949 #define set_PPI EIP |= SET_BIT1 950 #define set_PI2C EIP |= SET_BIT0 951 952 #define clr_PT2 EIP &= ~SET_BIT7 953 #define clr_PSPI EIP &= ~SET_BIT6 954 #define clr_PFB EIP &= ~SET_BIT5 955 #define clr_PWDT EIP &= ~SET_BIT4 956 #define clr_PPWM EIP &= ~SET_BIT3 957 #define clr_PCAP EIP &= ~SET_BIT2 958 #define clr_PPI EIP &= ~SET_BIT1 959 #define clr_PI2C EIP &= ~SET_BIT0 960 961 //**** B F0H **** 962 963 //**** CAPCON3 F1H **** 964 #define set_CAP13 CAPCON3 |= SET_BIT7 965 #define set_CAP12 CAPCON3 |= SET_BIT6 966 #define set_CAP11 CAPCON3 |= SET_BIT5 967 #define set_CAP10 CAPCON3 |= SET_BIT4 968 #define set_CAP03 CAPCON3 |= SET_BIT3 969 #define set_CAP02 CAPCON3 |= SET_BIT2 970 #define set_CAP01 CAPCON3 |= SET_BIT1 971 #define set_CAP00 CAPCON3 |= SET_BIT0 972 973 #define clr_CAP13 CAPCON3 &= ~SET_BIT7 974 #define clr_CAP12 CAPCON3 &= ~SET_BIT6 975 #define clr_CAP11 CAPCON3 &= ~SET_BIT5 976 #define clr_CAP10 CAPCON3 &= ~SET_BIT4 977 #define clr_CAP03 CAPCON3 &= ~SET_BIT3 978 #define clr_CAP02 CAPCON3 &= ~SET_BIT2 979 #define clr_CAP01 CAPCON3 &= ~SET_BIT1 980 #define clr_CAP00 CAPCON3 &= ~SET_BIT0 981 982 //**** CAPCON4 F2H **** 983 #define set_CAP23 CAPCON4 |= SET_BIT3 984 #define set_CAP22 CAPCON4 |= SET_BIT2 985 #define set_CAP21 CAPCON4 |= SET_BIT1 986 #define set_CAP20 CAPCON4 |= SET_BIT0 987 988 #define clr_CAP23 CAPCON4 &= ~SET_BIT3 989 #define clr_CAP22 CAPCON4 &= ~SET_BIT2 990 #define clr_CAP21 CAPCON4 &= ~SET_BIT1 991 #define clr_CAP20 CAPCON4 &= ~SET_BIT0 992 993 //**** SPCR F3H PAGE0 **** 994 #define set_SSOE SPCR |= SET_BIT7 995 #define set_SPIEN SPCR |= SET_BIT6 996 #define set_LSBFE SPCR |= SET_BIT5 997 #define set_MSTR SPCR |= SET_BIT4 998 #define set_CPOL SPCR |= SET_BIT3 999 #define set_CPHA SPCR |= SET_BIT2 1000 #define set_SPR1 SPCR |= SET_BIT1 1001 #define set_SPR0 SPCR |= SET_BIT0 1002 1003 #define clr_SSOE SPCR &= ~SET_BIT7 1004 #define clr_SPIEN SPCR &= ~SET_BIT6 1005 #define clr_LSBFE SPCR &= ~SET_BIT5 1006 #define clr_MSTR SPCR &= ~SET_BIT4 1007 #define clr_CPOL SPCR &= ~SET_BIT3 1008 #define clr_CPHA SPCR &= ~SET_BIT2 1009 #define clr_SPR1 SPCR &= ~SET_BIT1 1010 #define clr_SPR0 SPCR &= ~SET_BIT0 1011 1012 //**** SPCR2 F3H PAGE1 **** SFRS must set as 1 to modify this register 1013 #define set_SPIS1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x01;SPCR2|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 1014 #define set_SPIS0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x00;SPCR2|=SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 1015 1016 #define clr_SPIS1 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x00;SPCR2&=~SET_BIT1;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 1017 #define clr_SPIS0 BIT_TMP=EA;TA=0xAA;TA=0x55;SFRS=0x00;SPCR2&=~SET_BIT0;TA=0xAA;TA=0x55;SFRS=0x00;EA=BIT_TMP 1018 1019 //**** SPSR F4H **** 1020 #define set_SPIF SPSR |= SET_BIT7 1021 #define set_WCOL SPSR |= SET_BIT6 1022 #define set_SPIOVF SPSR |= SET_BIT5 1023 #define set_MODF SPSR |= SET_BIT4 1024 #define set_DISMODF SPSR |= SET_BIT3 1025 1026 #define clr_SPIF SPSR &= ~SET_BIT7 1027 #define clr_WCOL SPSR &= ~SET_BIT6 1028 #define clr_SPIOVF SPSR &= ~SET_BIT5 1029 #define clr_MODF SPSR &= ~SET_BIT4 1030 #define clr_DISMODF SPSR &= ~SET_BIT3 1031 1032 //**** SPDR F5H **** 1033 1034 //**** AINDIDS F6H **** 1035 #define set_P11DIDS AINDIDS |= SET_BIT7 1036 #define set_P03DIDS AINDIDS |= SET_BIT6 1037 #define set_P04DIDS AINDIDS |= SET_BIT5 1038 #define set_P05DIDS AINDIDS |= SET_BIT4 1039 #define set_P06DIDS AINDIDS |= SET_BIT3 1040 #define set_P07DIDS AINDIDS |= SET_BIT2 1041 #define set_P30DIDS AINDIDS |= SET_BIT1 1042 #define set_P17DIDS AINDIDS |= SET_BIT0 1043 1044 #define clr_P11DIDS AINDIDS &= ~SET_BIT7 1045 #define clr_P03DIDS AINDIDS &= ~SET_BIT6 1046 #define clr_P04DIDS AINDIDS &= ~SET_BIT5 1047 #define clr_P05DIDS AINDIDS &= ~SET_BIT4 1048 #define clr_P06DIDS AINDIDS &= ~SET_BIT3 1049 #define clr_P07DIDS AINDIDS &= ~SET_BIT2 1050 #define clr_P30DIDS AINDIDS &= ~SET_BIT1 1051 #define clr_P17DIDS AINDIDS &= ~SET_BIT0 1052 1053 //**** EIPH F7H **** 1054 #define set_PT2H EIPH |= SET_BIT7 1055 #define set_PSPIH EIPH |= SET_BIT6 1056 #define set_PFBH EIPH |= SET_BIT5 1057 #define set_PWDTH EIPH |= SET_BIT4 1058 #define set_PPWMH EIPH |= SET_BIT3 1059 #define set_PCAPH EIPH |= SET_BIT2 1060 #define set_PPIH EIPH |= SET_BIT1 1061 #define set_PI2CH EIPH |= SET_BIT0 1062 1063 #define clr_PT2H EIPH &= ~SET_BIT7 1064 #define clr_PSPIH EIPH &= ~SET_BIT6 1065 #define clr_PFBH EIPH &= ~SET_BIT5 1066 #define clr_PWDTH EIPH &= ~SET_BIT4 1067 #define clr_PPWMH EIPH &= ~SET_BIT3 1068 #define clr_PCAPH EIPH &= ~SET_BIT2 1069 #define clr_PPIH EIPH &= ~SET_BIT1 1070 #define clr_PI2CH EIPH &= ~SET_BIT0 1071 1072 /**** SCON_1 F8H ****/ 1073 #define set_FE_1 FE_1 = 1 1074 #define set_SM1_1 SM1_1 = 1 1075 #define set_SM2_1 SM2_1 = 1 1076 #define set_REN_1 REN_1 = 1 1077 #define set_TB8_1 TB8_1 = 1 1078 #define set_RB8_1 RB8_1 = 1 1079 #define set_TI_1 TI_1 = 1 1080 #define set_RI_1 RI_1 = 1 1081 1082 #define clr_FE_1 FE_1 = 0 1083 #define clr_SM1_1 SM1_1 = 0 1084 #define clr_SM2_1 SM2_1 = 0 1085 #define clr_REN_1 REN_1 = 0 1086 #define clr_TB8_1 TB8_1 = 0 1087 #define clr_RB8_1 RB8_1 = 0 1088 #define clr_TI_1 TI_1 = 0 1089 #define clr_RI_1 RI_1 = 0 1090 1091 //**** PDTEN F9H **** 1092 #define set_PDT45EN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;PDTEN|= SET_BIT2 ;EA=BIT_TMP; 1093 #define set_PDT23EN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;PDTEN|= SET_BIT1 ;EA=BIT_TMP; 1094 #define set_PDT01EN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;PDTEN|= SET_BIT0 ;EA=BIT_TMP; 1095 1096 #define clr_PDT45EN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;PDTEN &= ~SET_BIT2 ;EA=BIT_TMP; 1097 #define clr_PDT23EN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;PDTEN &= ~SET_BIT1 ;EA=BIT_TMP; 1098 #define clr_PDT01EN BIT_TMP=EA;EA=0;TA=0xAA;TA=0x55;PDTEN &= ~SET_BIT0 ;EA=BIT_TMP; 1099 1100 //**** PDTCNT FAH **** 1101 1102 //**** PMEN FBH **** 1103 #define set_PMEN5 PMEN |= SET_BIT5 1104 #define set_PMEN4 PMEN |= SET_BIT4 1105 #define set_PMEN3 PMEN |= SET_BIT3 1106 #define set_PMEN2 PMEN |= SET_BIT2 1107 #define set_PMEN1 PMEN |= SET_BIT1 1108 #define set_PMEN0 PMEN |= SET_BIT0 1109 1110 #define clr_PMEN5 PMEN &= ~SET_BIT5 1111 #define clr_PMEN4 PMEN &= ~SET_BIT4 1112 #define clr_PMEN3 PMEN &= ~SET_BIT3 1113 #define clr_PMEN2 PMEN &= ~SET_BIT2 1114 #define clr_PMEN1 PMEN &= ~SET_BIT1 1115 #define clr_PMEN0 PMEN &= ~SET_BIT0 1116 1117 //**** PMD FCH **** 1118 #define set_PMD7 PMD |= SET_BIT7 1119 #define set_PMD6 PMD |= SET_BIT6 1120 #define set_PMD5 PMD |= SET_BIT5 1121 #define set_PMD4 PMD |= SET_BIT4 1122 #define set_PMD3 PMD |= SET_BIT3 1123 #define set_PMD2 PMD |= SET_BIT2 1124 #define set_PMD1 PMD |= SET_BIT1 1125 #define set_PMD0 PMD |= SET_BIT0 1126 1127 #define clr_PMD7 PMD &= ~SET_BIT7 1128 #define clr_PMD6 PMD &= ~SET_BIT6 1129 #define clr_PMD5 PMD &= ~SET_BIT5 1130 #define clr_PMD4 PMD &= ~SET_BIT4 1131 #define clr_PMD3 PMD &= ~SET_BIT3 1132 #define clr_PMD2 PMD &= ~SET_BIT2 1133 #define clr_PMD1 PMD &= ~SET_BIT1 1134 #define clr_PMD0 PMD &= ~SET_BIT0 1135 1136 //**** EIP1 FEH **** 1137 #define set_PWKT EIP1 |= SET_BIT2 1138 #define set_PT3 EIP1 |= SET_BIT1 1139 #define set_PS_1 EIP1 |= SET_BIT0 1140 1141 #define clr_PWKT EIP1 &= ~SET_BIT2 1142 #define clr_PT3 EIP1 &= ~SET_BIT1 1143 #define clr_PS_1 EIP1 &= ~SET_BIT0 1144 1145 //**** EIPH1 FFH **** 1146 #define set_PWKTH EIPH1 |= SET_BIT2 1147 #define set_PT3H EIPH1 |= SET_BIT1 1148 #define set_PSH_1 EIPH1 |= SET_BIT0 1149 1150 #define clr_PWKTH EIPH1 &= ~SET_BIT2 1151 #define clr_PT3H EIPH1 &= ~SET_BIT1 1152 #define clr_PSH_1 EIPH1 &= ~SET_BIT0