第六章 内建自测试

1 内建自测试概念

1.1 背景

1.ATE测试成本

2.Memory测试的特殊性

-

- Memory内部需要测试的单元多

- Memory内部单元规整

3.客户对于在线测试的需求:汽车电子的可靠性要求

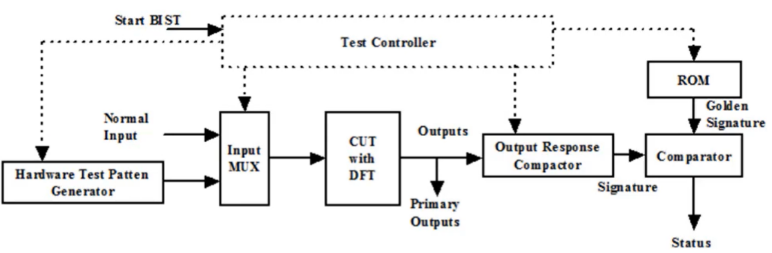

1.2 基本流程

- Start BIST:外部控制信号,开始自测试

- Test Controller控制Pattern Generator生成测试向量

- 测试向量与正常输入经过Input MUX选择后进入待测单元

- Compator输出结果压缩,得到Signature签名值

- 将期望签名值固化保存至ROM中

- Comparator进行对比输出最终结果

1.3 两种自测试

- Memory BIST:利用特定算法和向量来测试Memory

- Logic BIST:利用伪随机测试向量来测试逻辑电路

1.4 自测试优缺点

- 优点:降低测试成本、缩短测试时间(内部全速测试)、在线测试

- 缺点:占用额外的电路面积、无法产生某些特殊的测试向量

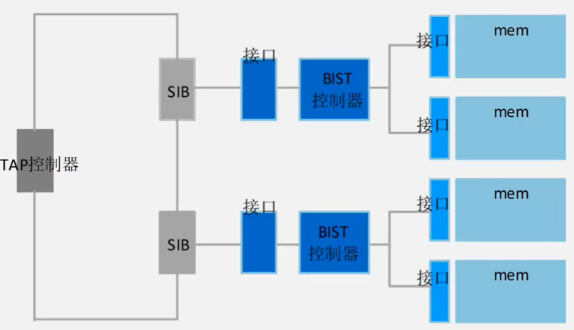

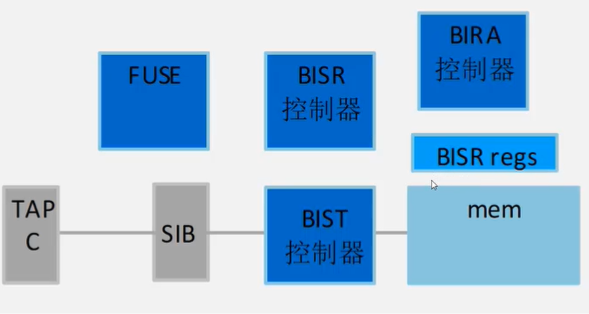

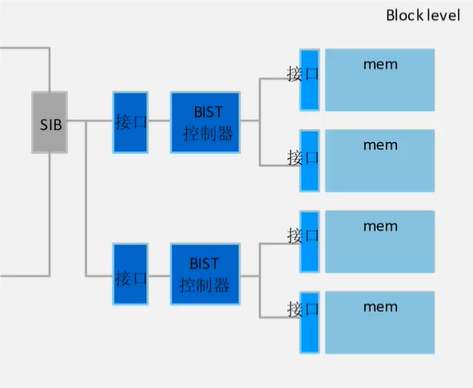

2 Memory BIST基本架构

- TAP控制器:TDI、TMS等IJAT控制信号部分;

- SIB:IJTAG控制开关,SIB打开意味着BIST电路连入IJTAG网络,SIB关闭不做测试处理;

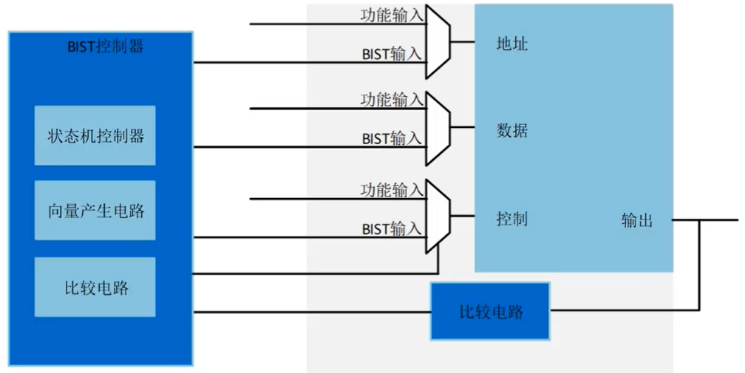

2.1 BIST部分结构

- 比较电路:可放在每个Memory附近,也可放在BIST控制器内。放在Memory附近可缩短大量Memory输出到比较电路之间的物理连线长度,比较电路只需要返回一根信号到BIST控制器,但这种放置会导致面积变大;相反,放在BIST呃逆面积小,但绕线难度大;

2.2 Tessent MBIST状态

1.启动:

-

- BIST控制器的输入:MBISTPG_EN = 1

- BIST控制器的输入:BIST_SETUP[1] = 1,BIST_SETUP[0] = 0

2.运转状态:

-

- BIST运行时DONE为0.test结束后DONE为1

- Test出错后GO为0,一直保持到test结束

2.3 BIST运行状态

- DONE = 0 且 GO = 0:测试未完成,但是已出错

- DONE = 1 且 GO = 0:测试完成,有memory出错

- DONE = 0 且 GO = 1:测试未完成,暂时没有memory出错

- DONE = 1 且 GO = 1:测试完成,所有memory通过测试

3 MBIST算法

memory的Fault Model:Fault model通常是由IP开发商、生产制造商、EDA、客户共同参入指定的

常见的fault model包括:

-

- Stuck-at fault:固接1或0

- Transition fault

- Coupling fault

- Address decoder fault

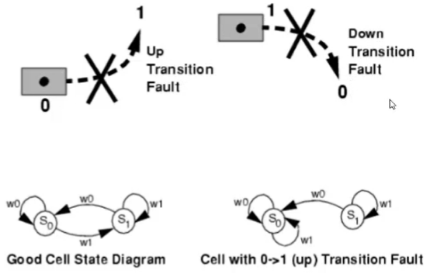

3.1 Transition fault

Up Transition Fault:上升跳变错误

Down Transition Fault:下降跳变错误

3.2 Coupling Fault 耦合错误

反向耦合错误:邻近的单元状态变化,导致单元取反

状态耦合错误:临近单元状态变化,导致单元状态变化

3.3 Address Decoder fault

- 某一个有效的地址对应不上相应的存储单元

- 某一个地址对应多个存储单元

- 多个地址对应一个存储单元

3.4 MBIST基础算法

3.4.1 March-C算法

- 按地址从低到高:写0

- 读0,写1

- 读1,写0

- 读0

- 按地址从高到低:读0,写1

- 读1,写0

- 读0

3.4.2 Read-Only算法

- 按地址从低到高:读ROM里的数据,通过MISR压缩

- 比较压缩后的签名值与期望的签名值

- 按地址从高到低:读ROM里的数据,通过MISR压缩

- 比较压缩后的签名值与期望的签名值

4 Memory BIST修复功能

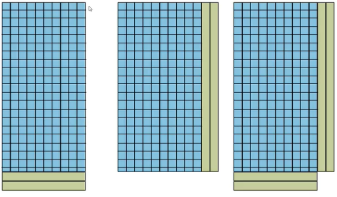

4.1 Memory Redundancy

Memory设计中Redundancy(Row,Column):额外增加一些冗余单元,牺牲面积提升Memory面积

4.2 BIST修复功能

- BISR regs(Build In Self Repairs):带有redanduncy的memory通常会额外多一些管脚,这些管脚会连到BISR regs上,寄存器存储memory repairs信息,控制哪些redanduncy替换哪些原本的存储单元;

- 每个memory的repairs信息不同,均有属于自己的regs,对于可修复的存储单元均可以加上BISR regs;

- 将BISR regs串成一条链路,链路信息从FUSE中获取;

- FUSE保存整个存储空间的修复信息(测试人员会将测试故障归纳得到修复信息,得出哪些单元需要修复,如何修复);

5 Tessent插入Memory BIST流程

5.1 主要步骤

- 读入网表

- 配置测试时钟等信号

- 配置MBIST

- 插入MBIST

- 生成综合脚本

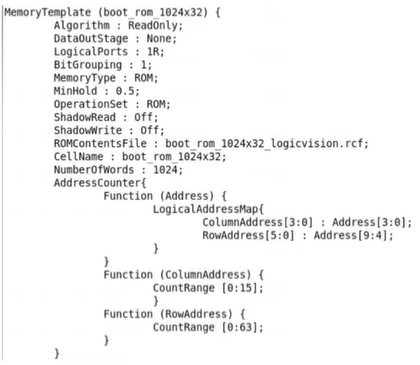

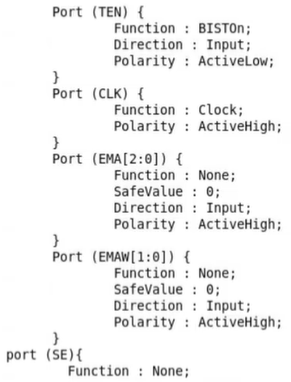

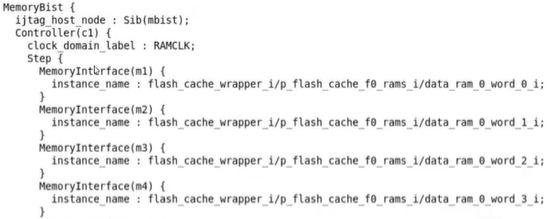

5.2 读入网表

- set_context dft -no_rtl

- read_cell_library & read_verilog

- set_current_design

- set_design_level block

- Memory bist文件:

5.3 配置时钟等信号

- 配置时钟信息:Add_clocks RAMCLK -period 10ns -label ramclk

- check_design_rules

5.4 配置MBIST

- set_dft_specification_requirements -memory_test on

-

- -memory_bist

- -memory_bisr_chains:repairs寄存器

- -memory_bisr_controller:控制器

- on表示上述三个均打开,off均关闭

5.5 配置MBIST

- Create_dft_specification:根据工具内部规则将memory分组,每个分组配置不同

- Report_dft_specification

5.6 插入MBIST

- Process_dft_specification:生成相应的MBIST模块的RTL,插入现有网表

- Extract_icl

- ICL是描述IEEE1687网络的连接关系

- 这一步会检查网表的连接关系是否正确

- 必须pass,才能保证后面的test pattern generation正确

5.7 生成综合脚本

- run_synthesis(-generate_scripts_only)

- 在tessent shell内部调用综合工具

- 只生成综合脚本,用户在外部调用综合工具

- write_design_import_script

最终插入MBIST的总体框架如下

6. 实训环节

实训环节后续补充