第三章 测试压缩技术

1.常用的测试压缩技术

1.1 测试压缩的驱动力

- 工艺复杂度导致错误类型的增加

- 芯片复杂度导致扫描单元数的增加

- 测试向量的增加

- 测试管脚的有限性

- 测试机台内存容量的有限性

- 测试时间的增加

1.2测试压缩的目标

- 测试开销

-

- 减轻测试机台需要存储的测试向量的大小

- 减少测试时间

- 减少测试需要的管脚数

- 测试质量

-

- 支持所有测试向量的压缩

- 保证测试覆盖率

- 保证测试的可诊断性

1.3常用的测试压缩技术

- 测试压缩技术分为:

- 测试压缩:

- XOR压缩

- OPMISR压缩

- 测试解压缩:

- 广播解压

- 可配置选择器解压

- Ring Generator片上解压

- 测试压缩:

- 测试压缩技术

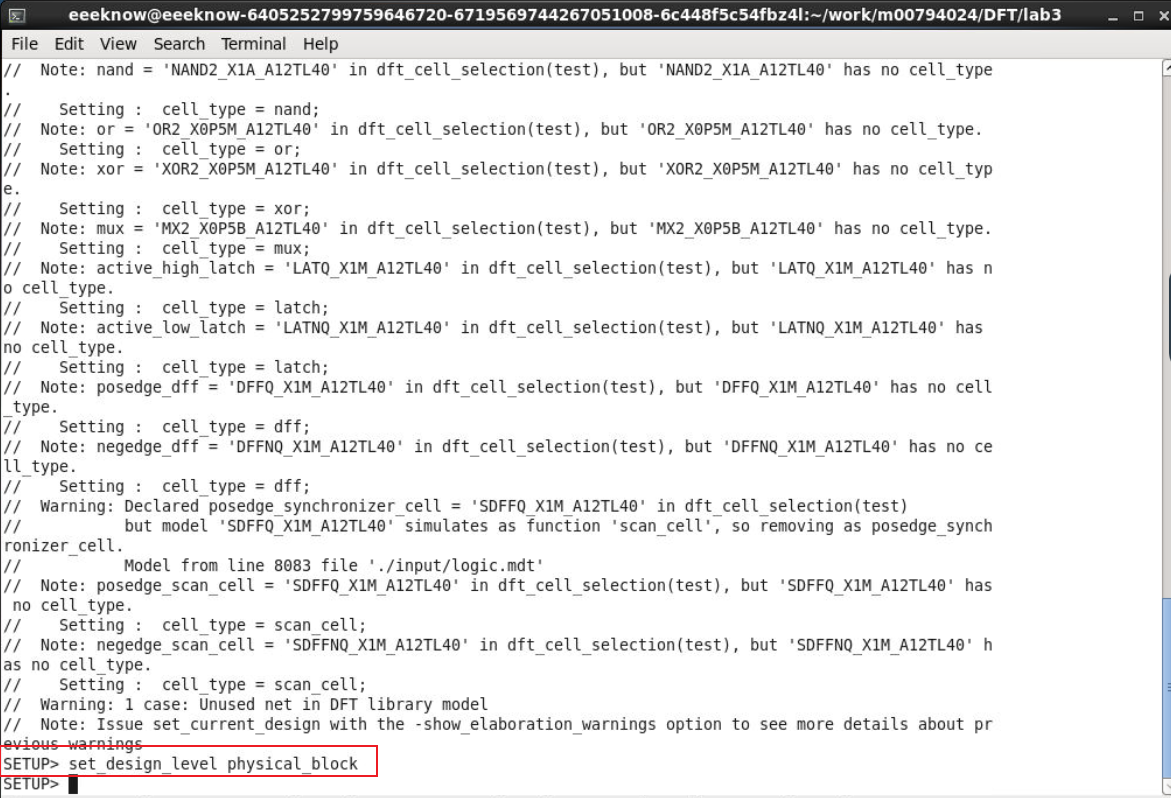

- XOR扫描链压缩:在扫描链的尾部插入N级XOR树状结构,将扫描链压缩为1/2的N次方。空间压缩。

- 压缩率较高

- 逻辑增加较少

- 扫描链上的X态会影响测试覆盖率

- 不同扫描链的同一bit上同时出现fault,也会影响测试覆盖率

- 为什么用异或门,而不用与门或门?因为异或门输出与两个输入都有关系,受两者的影响;同时,加入与门扫描链上出现一个状态“0”,那与该条扫描链相邻的都会被屏蔽掉

- XOR扫描链压缩:在扫描链的尾部插入N级XOR树状结构,将扫描链压缩为1/2的N次方。空间压缩。

-

- 改进型XOR压缩树

- 较好的可观测性

- 扫描端口数较多

- 扫描链上的X态会影响测试覆盖率

- 优势在于,加入扫描链1上有未知态,则扫描链2上的状态可以通过扫描输出3观察,但同时存在如果扫描链2上有未知态,则未知态就会影响更多的扫描链了

- 改进型XOR压缩树

-

- OPMISR:片上多输入签名寄存器

上图为典型MISR内部电路结构,下图为扫描链结构

Si/So为双向扫描输入输出端口,可移入数据,也可移出数据。

Mask可过滤不定态。

MISR为压缩模块,mrun为控制压缩/移位信号,mrst为压缩复位信号。

工作流程:通过Si/So端口将数据移入扫描链,然后存到MISR线性移位寄存器中保存,同时可以将新一轮的测试向量移入扫描链,当所有测试向量都移入MISR完成压缩默认完成一次签名,最后通过sdir信号控制Si/So端口方向将压缩向量输出端机台。但OPMISR不是无损压缩,不能通过签名值反推出扫描链上所有可能错误。

-

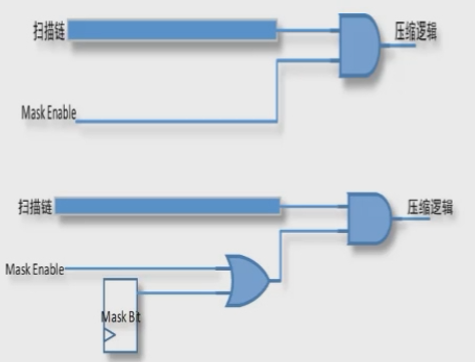

- 未知态掩膜(X masking)

- 未知态引入:

- 未串入扫描链的寄存器

- False path

- 未处在测试状态下的Memory

- 未知态消除

- 更改逻辑,通过增加阻塞逻辑阻止传播

- 在压缩逻辑前面增加Masking逻辑

- 未知态引入:

- 未知态掩膜(X masking)

- 测试解压缩技术

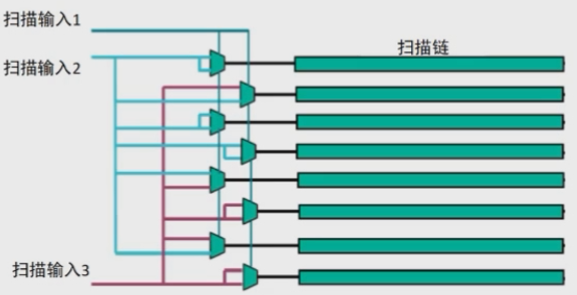

- 广播方式:优点:结构简单,不增加额外逻辑;缺点:扫描输入FanOut过大造成Pr绕线问题,同时移入相同向量一些逻辑是测试不到的

-

- 可编程广播方式:动态调整扫描输入(Synopsys解压工具)

-

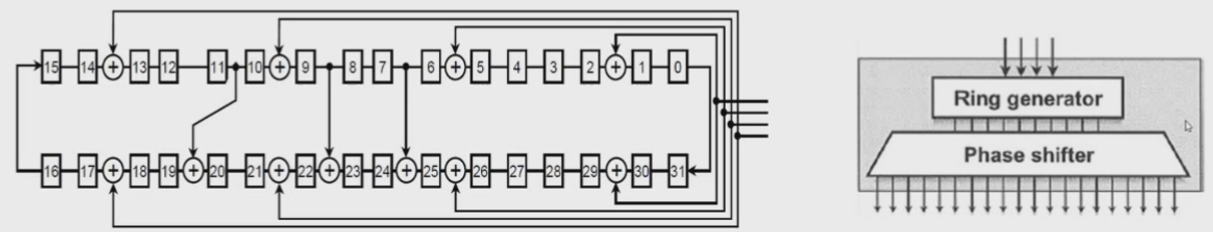

- Ring Generator(环形测试向量生成器):Phase shifter减少线性相关性(Mentor公司)

2.Tessent压缩模块EDT的简介

2.1 Tessent EDT逻辑

EDT:Embedded Deterministic Test

- 解压逻辑:解压测试向量,并将外部极少的测试输入端转换成内部较多的扫描链输入端;

- 旁路逻辑:保证模型模式下,测试人员可以通过旁路逻辑Bypass掉EDT压缩逻辑的影响,用全扫描的方式进行诊断;

- 掩膜逻辑:减少扫描链上的未知态对正常逻辑的产生结果的影响;

- 压缩逻辑:EDT压缩逻辑采用XOR压缩技术;

- EDT时钟:测试时钟,用来驱动EDT内部解压逻辑和掩膜逻辑内部的寄存器,和普通移位时钟不同,但可通过他特定逻辑产生移位时钟;

- EDT扫描输入:扫描数据输入;;

- EDT Update:复位EDT内部逻辑;

- EDT旁路逻辑信号:Bypass掉EDT的压缩逻辑;

- EDT扫描输出:扫描结果输出;

2.1.1 解压逻辑

少量测试管脚通过解压逻辑,将一系列测试向量灌输到内部环形向量发生器内以产生更多的向量。同时利用异或门组成的Phase Shifter来减少环形向量发生器产生的线性相关的向量;将通过Phase Shifter解压的向量输送到内部众多的扫描链上。最终实现完整的解压过程。

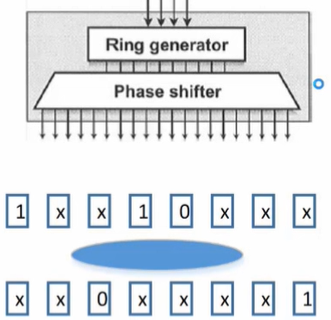

通过解压模块产生的向量是针对性的测试,测试时会向芯片内全部单元扫入向量,但是测试fault的单元只会是一部分,每次扫描只会是系统全部单元的5%-10%,而这部分的扫描寄存器需要确定的测试值用于测试,其他不测fault的单元测试向量不感知。

如上图所示,图中只有5个寄存器的值需要特定的测试向量测试,其他的单元不在意测试向量值。

旁路逻辑

旁路逻辑由一组选择器组成,下面是简单版本的EDT示例。每个选择器是加载到每个扫描链内部头上,选择器一端是EDT的解压逻辑,另外一端是扫描输入端或扫描输出端,压缩逻辑之后还有一个选择器,用以选择扫描输出的数据。

问题:如果扫描链是在不同时钟域上,这种串行的数据通路应该如何处理?

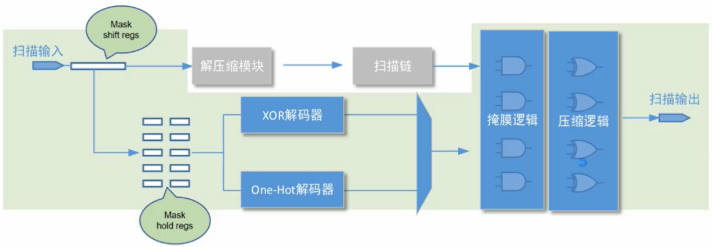

压缩逻辑+掩膜逻辑

EDT掩膜两种模式:XOR解码器、One-Hot解码器。如果测试时有过多的未知态,就使用One-Hot模式,只让关心的那条扫描链输出到扫描端口,或者只想诊断某条扫描链上的fault。平时测试时未知态不会太多,一般使用XOR模式,然后使用掩膜逻辑中的与门直接将整条扫描链都掩膜掉,防止未知态传播到压缩逻辑中,影响测试结果。

问题:掩膜向量是如何进入芯片中?EDT有两组寄存器,分别是掩膜移位寄存器、掩膜保持寄存器。在ATE机台将测试向量打入测试逻辑时,会在测试向量尾端增加一节掩膜向量,在测试向量移入Ring Generator后,还需要几个测试时钟周期将掩膜向量移入掩膜移位寄存器中,掩膜保持寄存器就会保持住移位寄存器中掩膜向量,并通过一段逻辑Decode产生各种需要的信号。

问题:为什么需要掩膜保持寄存器呢?因为需要确保当前测试向量的掩膜逻辑不变,防止有新的测试向量进来后,原来的掩膜向量仍然能够起到作用。

2.2 Tessent EDT插入流程

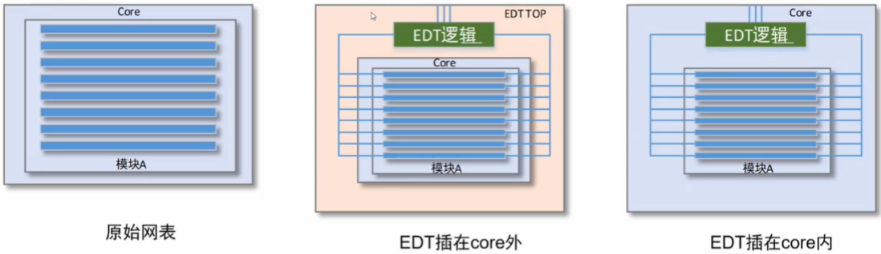

插入EDT压缩逻辑按照位置分为Core内插入和Core外插入。

具体区别示意图如下:

2.2.1 Core外插入EDT的流程

Tessent不支持综合网表,需要拿到综合后的网标文件进行扫描链的插入。

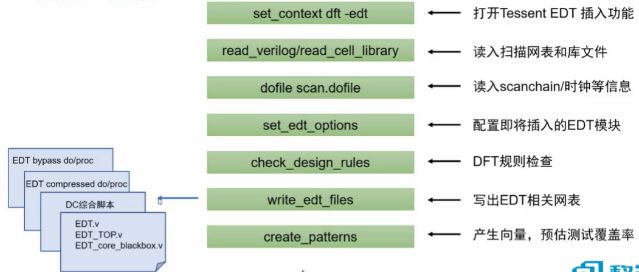

具体流程图如下:

流程命令如下:

-

- set_context dft -edt

- read_verilog/read_cell_library

- dofile scan.dofile:dofile文件是在扫描链插入时工具自动生成的文件,里面包含了扫描链信息与时钟复位信息;

- set_edt_options

- check_design_rules

- write_edt_files

- create_patterns

写出EDT相关网表:

-

- EDT.v:EDT模块代码;

- EDT_TOP.v:新增的外层逻辑代码;

- EDT_core_blackbox.v:防止在综合与插入过程中修改core逻辑,这里使用一个black作为core的代替;

- DC综合脚本:用于综合EDT的脚本;

- EDT compressed/bypass do/proc:包含压缩后生成的do/proc文件、将压缩逻辑旁路掉的do/proc文件,用以产生压缩与不压缩的测试向量,预估测试覆盖率;

3.实训环节:插入EDT

实训环节后续补充

这里提前对.db文件与DC综合时各种lib library做出说明:

Target Library:

由ASIC Vendor提供,后缀一般为".db",里面包含标准单元,Verilog文件映射为最后结构级网表的时候,就在里面查找标准单元。综合的最后就是把自己的code转换为vendor提供的单元的过程。

Link Library:

设计中不可避免的要用到一些第三方的IP,这些IP并不是designer设计的而是直接例化使用的。这些第三方的IP比如PLL,编译好的RAM,PAD等。这些IP在仿真时候往往使用vendor提供的一个仿真模型来模拟IP的真实行为。在综合的过程中并不希望DC把这些模型转换为标准单元库的。所以就需要用到Link Library,Link Library就是告诉DC这些第三方的IP不用你综合直接调用Link Library的lib文件即可。

Symbol Library:

在使用DCG模式是需要标准单元在电脑上显示的一个样子,也就是每个标准单元的“图标”,就要使用Symbol Library一般后缀为“.sdb”。

synthetic library

和link lib有点类似。当设计中使用了synopsys的DesignWare中的一些IP时,需要在综合中加入该库。

DC综合时用来将HDL代码转化为相对应的元件时所参考的模型库,比如RTL中的符号“+”,可以通过查找模型库将生成某一类加法器。

=============2023.08.27=============

Tessent可以在block和TOP level分别插入EDT压缩逻辑,也可以新增一个逻辑层次,用来包含功能逻辑和新插入的EDT逻辑。下面以在block level的内部插入EDT进行演示。

3.1 生成DET逻辑

在block level生成EDT相关的RTL。

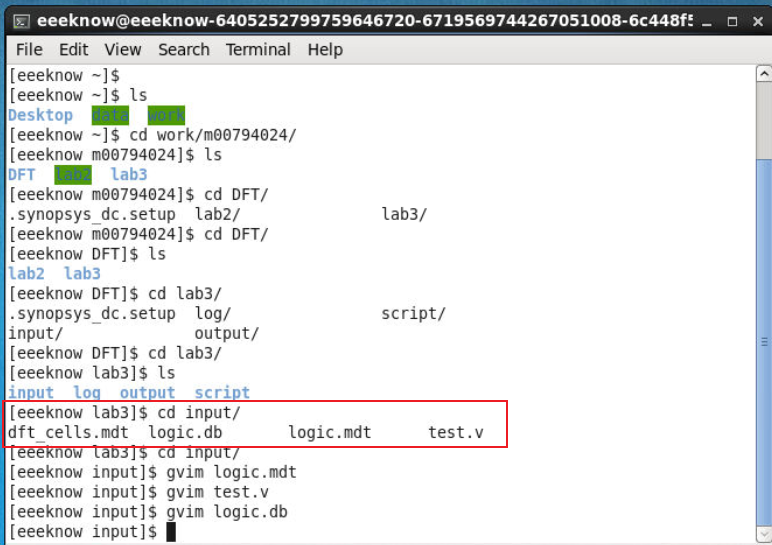

准备好的综合后网表和相应库文件统一放在lib3/input目录下,input目录下文件如下:

- logic.mdt : 标准单元的DFT库文件。

- dft_cells.mdt : 告诉Tessent,在需要插入逻辑时,从这个文件里选择相应功能的cell类型。

- test.v :输入网表文件。

- logic.db : 综合用的STD cell库。(综合所用的单元库)

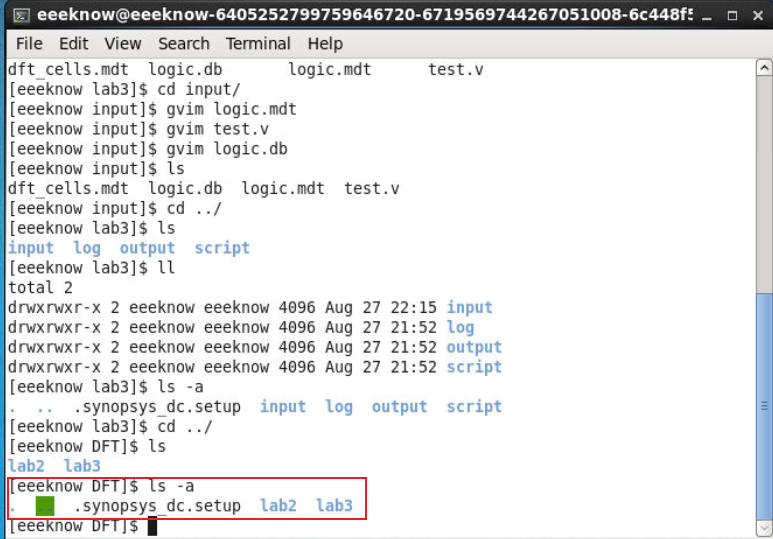

注意,同时要复制DC的启动文件(.synopsys_dc.setup)到你的工作目录下,否则后面的EDT工作会出错:

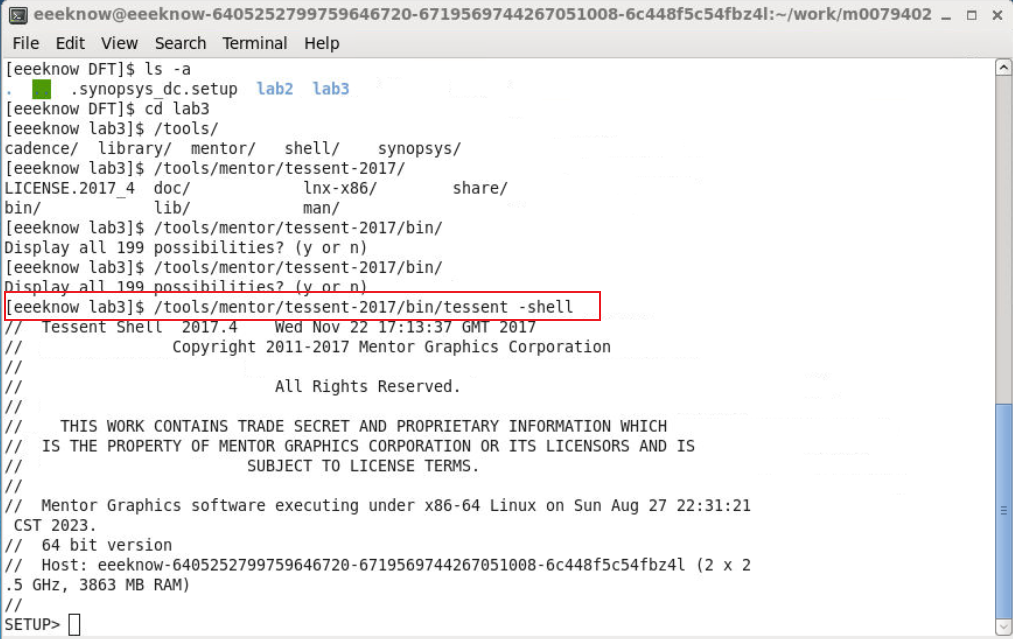

3.1.1 启动Tessent

要插入EDT,所以需要设置以下的context:

#-no_rtl指的是我们用的是综合网表,而不是RTL网表,-design_id是为了方便记忆起的名字。

SETUP> set_context dft -no_rtl -design_id edt

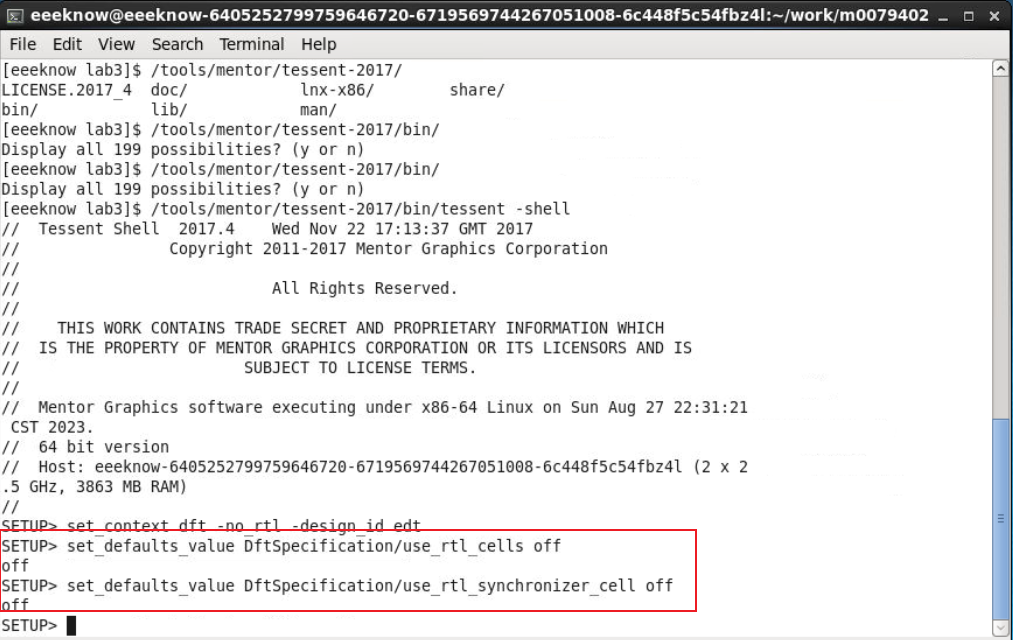

执行下面两条命令,告诉工具不要自己综合cell,而是尽可能选用dft_cells.mdt里指定的cell类型

set_defaults_value DftSpecification/use_rtl_cells off

set_defaults_value DftSpecification/use_rtl_synchronizer_cell off

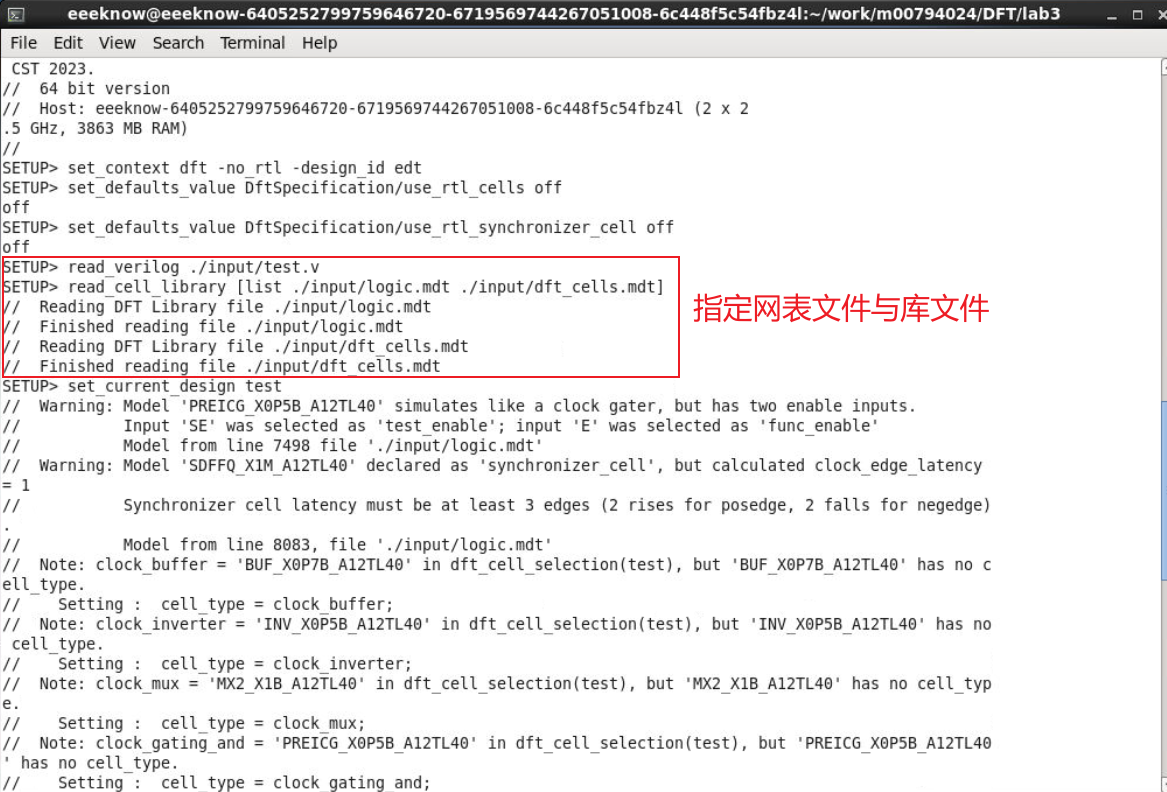

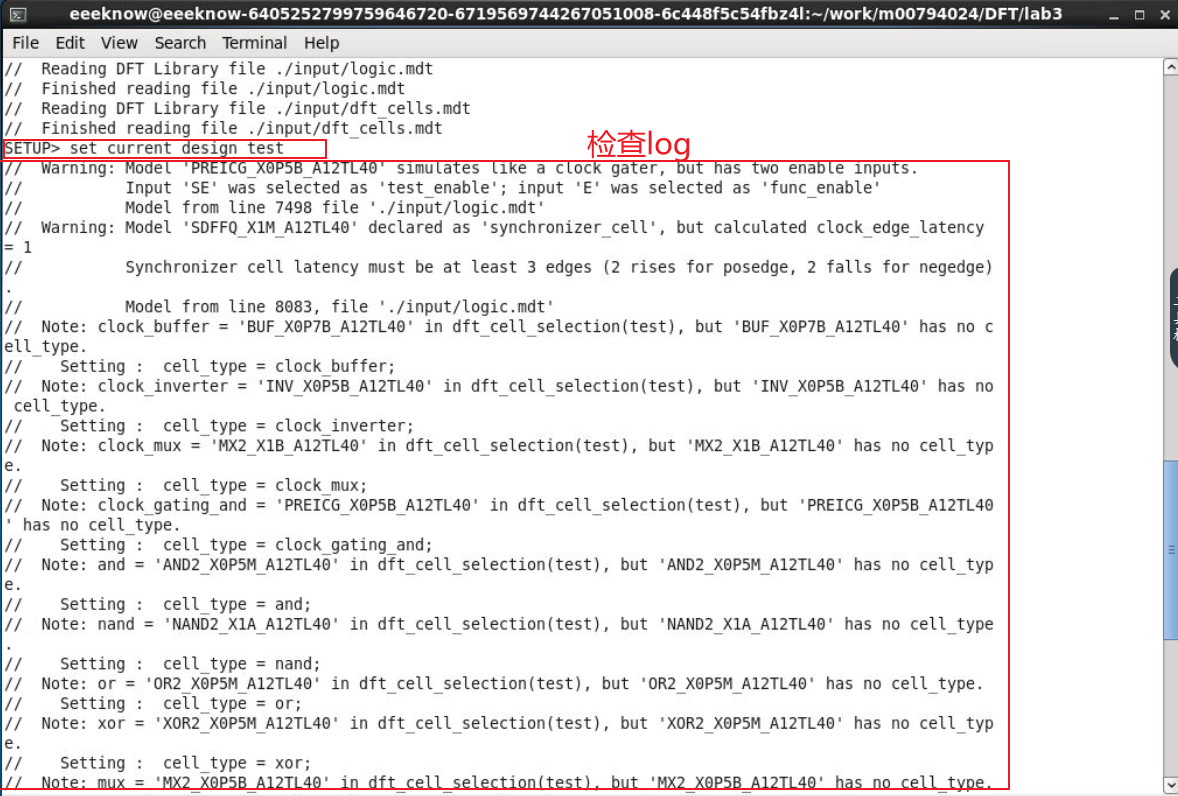

指定网表文件和读入网表文件、库文件:

#指定网表文件 read_verilog ./input/test.v(指定网表文件) read_cell_library [list ./input/logic.mdt ./input/dft_cells.mdt] set_current_design test(读入网表文件,并进行检查) set_design_level physical_block(当前层次结构为block,而非top)

读入网表:

设置当前的层次信息: