第二章 扫描链的插入

一、扫描链插入的流程

1.背景回顾

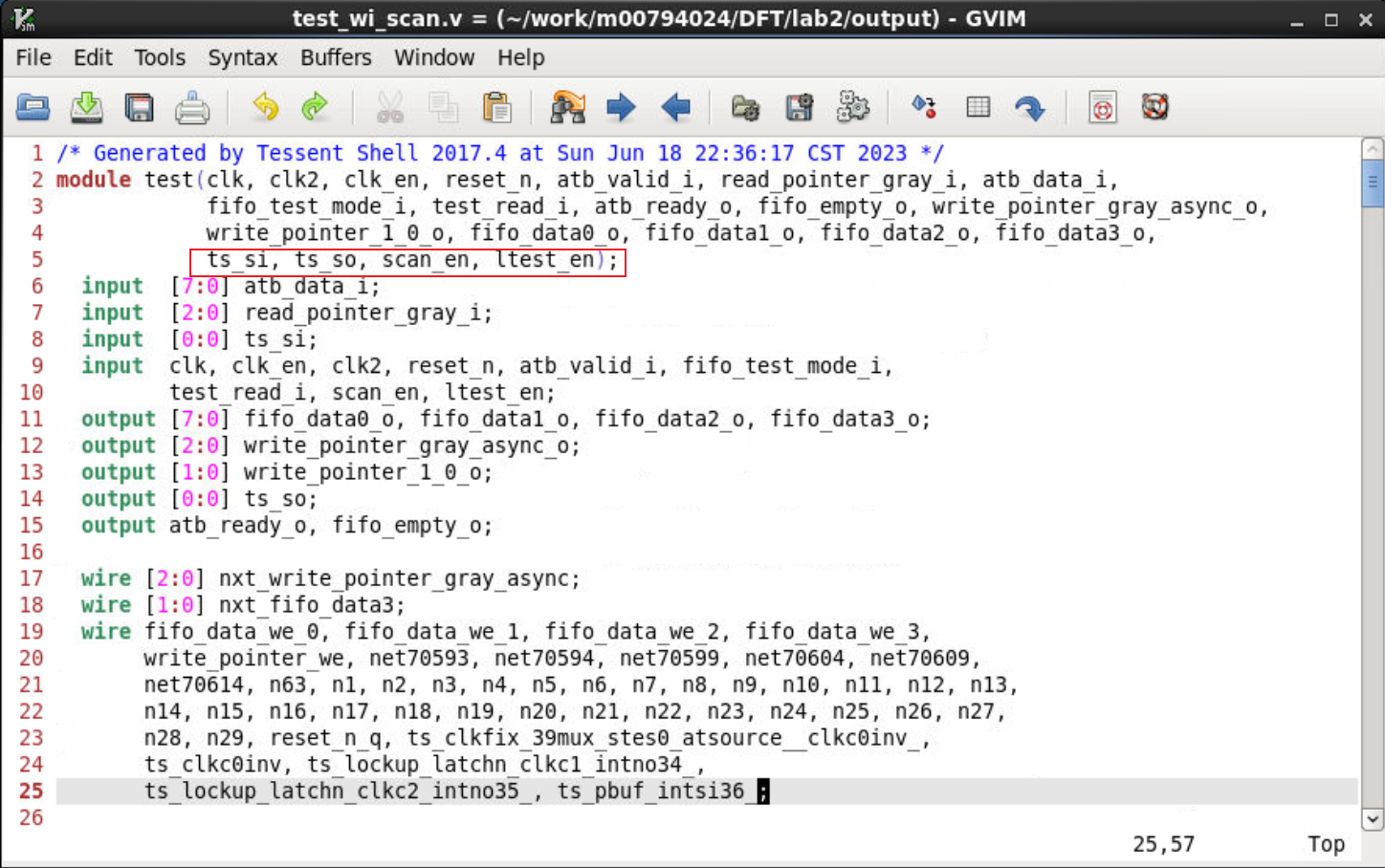

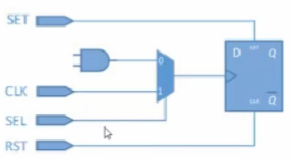

为了可观测性、可测试性,DFT将D触发器替换成了带有MUX的DFF,如下图所示。

D端:常规数据输入端口;

S端:扫描链数据输入端口;

SE端:工作模式选择端;

CK端:时钟;

Q端:数据输出端;

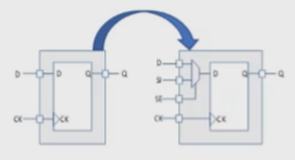

通过将电路中的寄存器替换成扫描寄存器,可以有效检查出电路在制造过程中哪部分逻辑电路出现问题。如下图所示,通过将与门前后的三个寄存器替换成扫描寄存器,就可以检查与门功能是否正确。

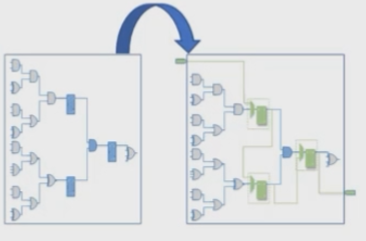

实际电路中,组合逻辑中会插入很多时序逻辑触发器,那么我们可以将这些触发器都换成扫描触发器,就可以检查整个电路的逻辑功能是否正常。如下图所示。

2.扫描链插入流程(以Mentor公司的tessent为例)

1)初始化

- set_context dft -scan(指定功能,扫描链插入功能)

- read_verilog(读入网表)

- read_cell_library(读入库文件)

- analyze_control_sianals

2)测试配置

- set_scan_enable

- set_test_logic

3)规则检查

- set_system_mode_analysis(检查设计规则是否有问题)

4)扫描链插入

- analyze_scan_chains

- insert_test_logic

5)保存结果

- write_design

- write_atpg_setup

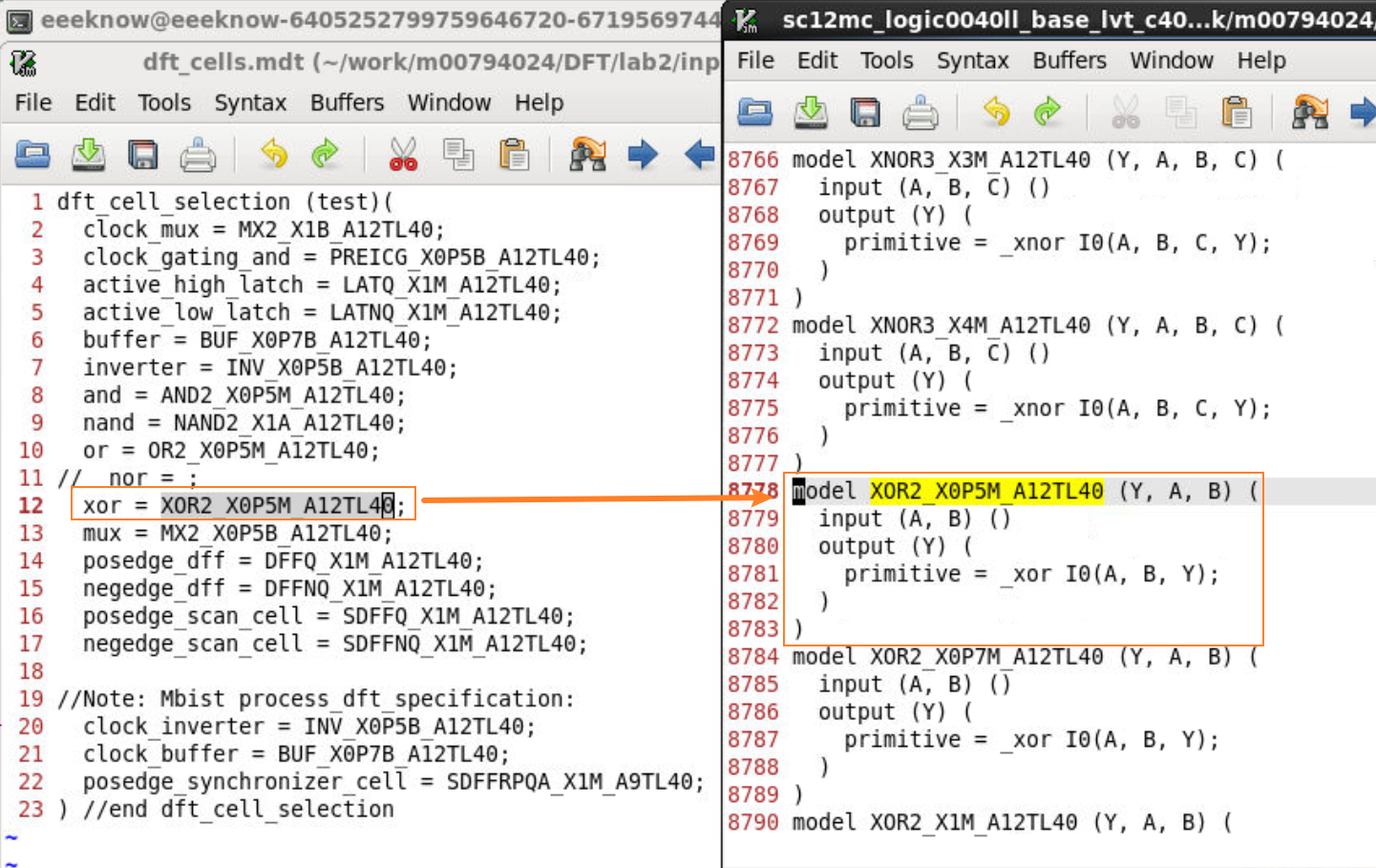

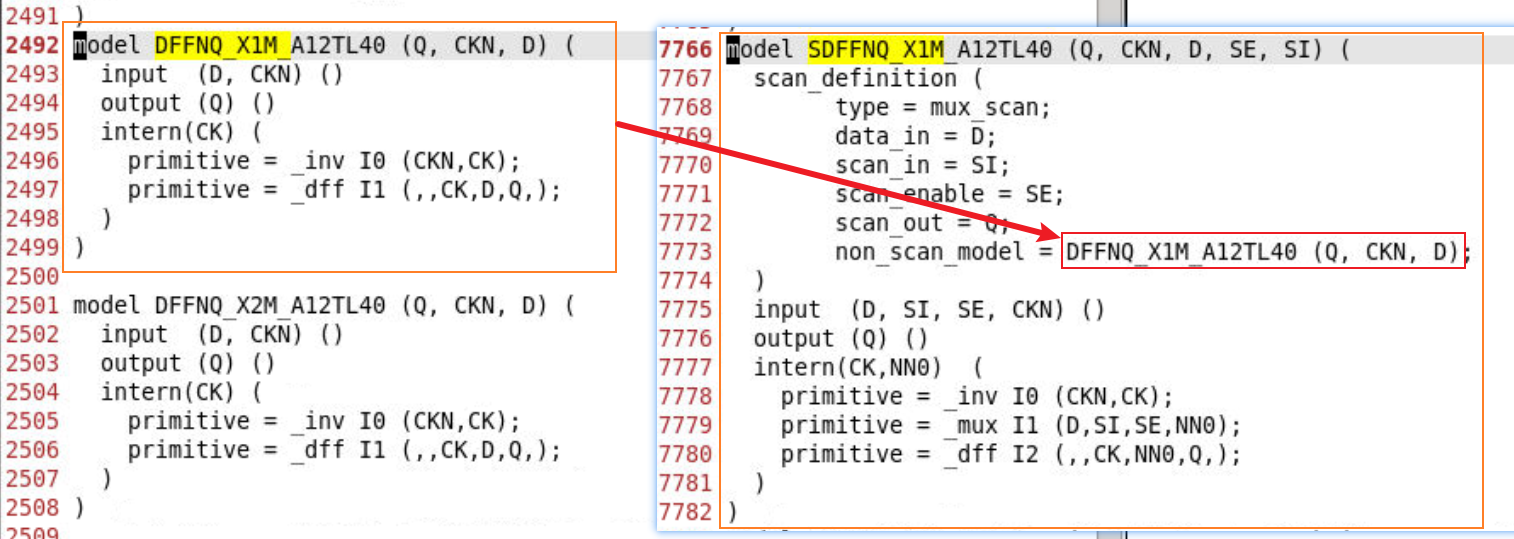

2.1 初始化

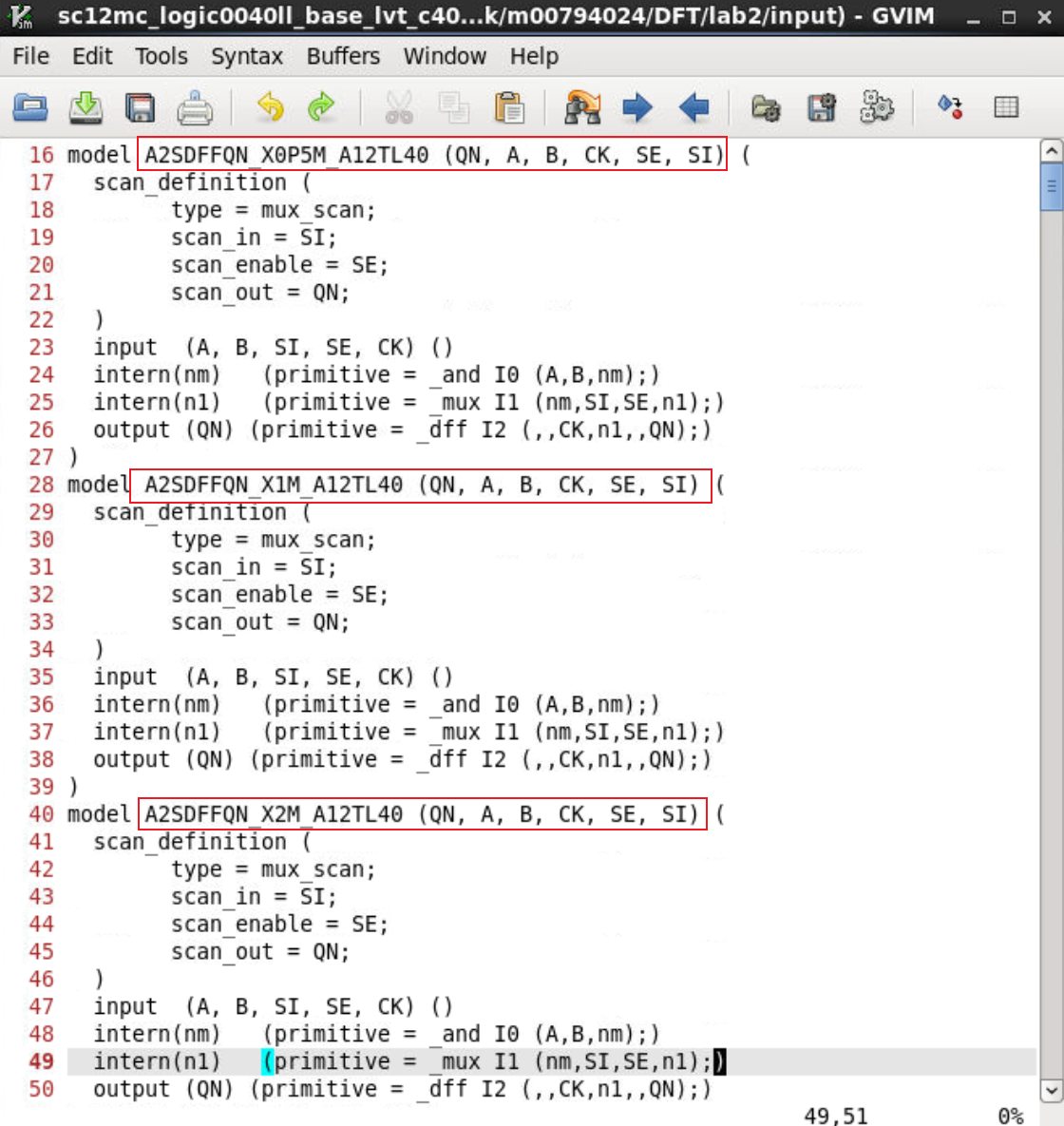

1)读入综合后的网表文件

2)读入DFT库文件:对cell进行建模

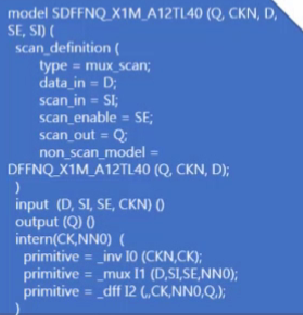

上图所示:常规的DFF网表文件

上图所示:带有DMUX的DFF网表文件,其中non_scan_model对应着的就是不带MUX的同类DFF

3)综合完成后,如果需要对综合后的网表文件进行扫描寄存器的替换,可以使用工具自动将普通寄存器替换成带扫描功能的寄存器;

也可以用命令强制替换:set_cell_model_mapping -new_model DFF -module ABC。

其中module ABC是替换范围的设置,对ABCmodule中寄存器替换,-instance ABC就是对instance名字的DFF中进行替换。

4)指定输入端口的初始化状态:add_input_constraints SEL -C1(指定下图中MUX的选择端为1)

指定所有可以改变寄存器状态的输入信号,比如,时钟,复位,置位。

工具自动识别信号:analyze_control_signals

手动指定:add_clock 0 CLK;#0 表示CLK inactive的状态

2.2 测试配置

1)一般可采用工具默认的配置,自动生成Ltest_en(测试使能),scan_en(扫描使能端)

对于复杂设计,就需要手动指定:

set_scan_enable/SCAN_ENABLE(指定扫描使能端为“SCAN_ENABLE”)

通过set_test_logic告诉工具可以自动修正clock/reset/set上的DRC违例,例如,set_test_logic -clock/reset/set on

2.3 规则检查(主要检查寄存器配置、扫描链配置、时钟复位置位等配置)

确保扫描操作可以正确执行

确保寄存器可控性

- set_system_mode_analysis & report_drc_rules

2.4 扫描链插入

- analyze_scan_chains:将扫描寄存器分配到扫描链上

扫描链配置:

- set_scan_mode

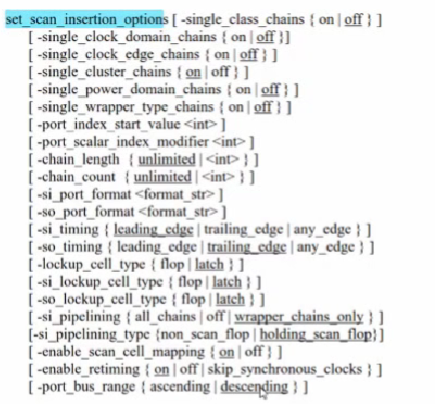

- set_scan_insertion_options

- create_scan_chain_family,三个命令都可以进行配置,具体配置options如下图所示

-

- single_clock_domain_chains on/off 是否允许相同时钟串在一条扫描链上

- single_clock_edge_chains on/off 是否允许相同时钟沿触发器串在一条链上

- chain_length 链长

- chain_count 链数

- insert_test_logic:插入指定数量、长度的扫描链,插入测试逻辑(受set_test_logic选项控制)。如下如所示,左图在第一个寄存器移位操作时,中间寄存器复位状态不定不可控,第三个寄存器时钟端又受到第二个寄存器影响分频电路,第二个寄存器在移位时第三个时钟不可控,通过insert和set这两个命令工具会自动修正上述问题。或门可以在测试使能时会屏蔽来自Q端的信号,第三个寄存器在测试时使用原本的时钟而不是来自Q端的数据。

2.5 保存结果

- insert_test_logic -write_in_tsdb on(默认将网表信息和配置信息保存到tsdb文件中,也可使用下面两个命令)

- write_design -output_file abc_scan.v(保存带扫描链信息的网表)

- write_atpg_setup abc(保存.defile&.testproc file,作为后续ATPG工作的输入)

二、扫描链插入的考量因素

1.时钟域

- 工具默认行为:不同时钟域,同一时钟域的不同时钟沿出发,被划分在不同的扫描链上。

- 同一时钟域的上升沿和下降沿可以串在同一条链上:下降沿寄存器在前,上升沿寄存器在后。

- 不同时钟域的寄存器可以串在同一条链上。

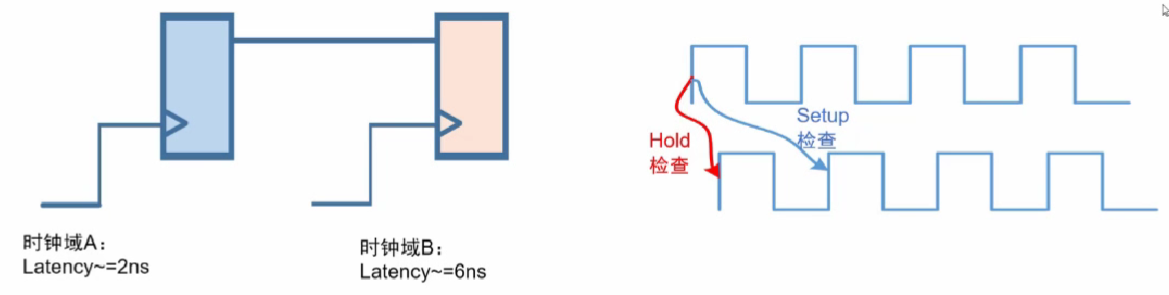

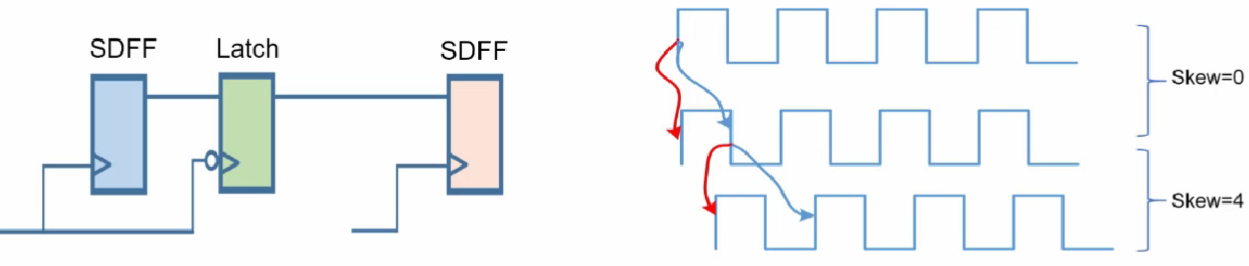

2.跨时钟域扫描链连接导致的时序违例问题

1)当扫描链上存在跨时钟域的连接,很有可能导致扫描移位的时序出现保持时间的违例。如下图所示,因为移位通常采用的慢速时钟,不会出现setup_violation,同时扫描寄存器之间又不会有组合逻辑,经常导致holdup_violation问题。

2)增加lockup latch来解决跨时钟域潜在的保持时间违例,如下图所示,增加低电平有效的Latch,使得数据延迟半个时钟周期到下一个寄存器,可有效解决holdup问题。

3.扫描链长度的考量

1)扫描链长度和扫描链条数的对应关系:

扫描链长度≈ 全芯片扫描单元bit数/扫描链的条数

2)以全芯片扫描单元bit数10K为例。

3)从减少测试时间的角度出发,希望增加扫描链的条数以减少扫描链的长度。(条数增加会导致扫描端口数增加,但是可以压缩技术解决)

4.扫描链长度均衡性的考量

1)测试向量从测试机台移位到测试芯片时,以芯片最长的扫描链长度为准。

2)为了减少测试时间,在插入扫描链时,尽量保证各扫描链长度的均衡性。

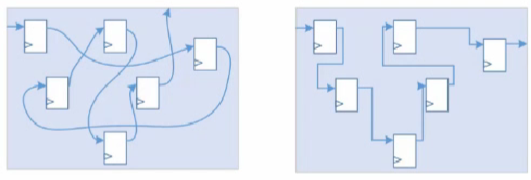

5.基于物理信息的扫描链链接

1)如果不考虑扫描寄存器的物理位置,扫描链的连接可能杂乱无章,容易引起后端绕线和时序问题。

2)后端工具的scan reordering功能优化力度较小,不能完全解决绕线和时钟问题。

3)在做扫描链连接时,通过后端传递回来的DEF文件,标定所有寄存器的物理位置,工具则可以就近串链,对后端时序比较友好。

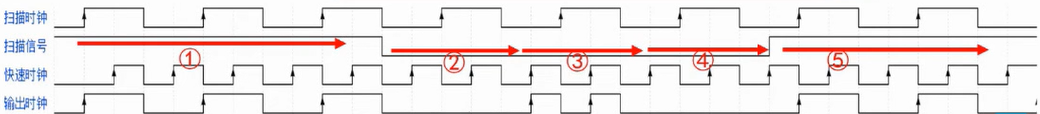

三、测试时钟介绍

1.测试时钟的频率

1)对于移位操作以及DC测试的捕获操作,通常选择较低的时钟频率(~ 50Mhz),这类测试时钟一般由测试机台提供。

2)对于AC测试的捕获操作,通常选择和功能时钟频率相同的测试时钟,往往在片内产生。

问:什么是DC测试?什么是AC测试?

2.测试时钟的两个问题

由于搜啊秒寄存器只有一个时钟端,则到达寄存器的时钟必须同时具有功能和测试两种属性:

问题1:怎么将功能时钟和测试时钟融合?

问题2:怎么在片上产生AC测试时钟波形?

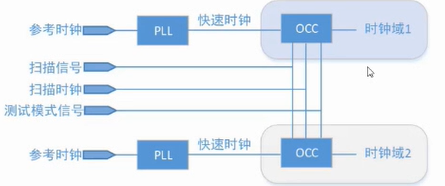

3.测试时钟的引入

为了解决这两个问题,需要在功能时钟上加入片上时钟控制器(On-Chip Clock Controller):

1)切换功能时钟和测试时钟;

2)为AC测试提供正确数量的功能时钟脉冲;

3)每个时钟域单独控制;

问:扫描信号指的是什么?用于OCC的捕获时钟获取,移入时钟向量到时钟链条状寄存器

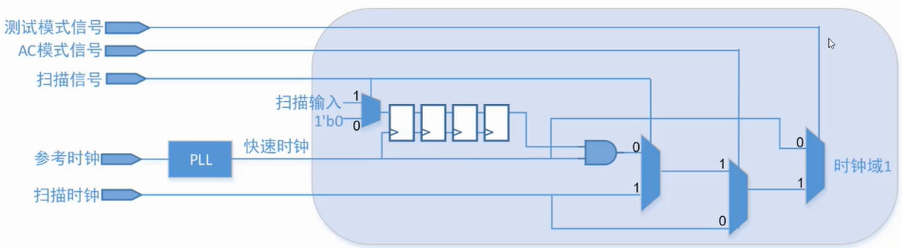

上图所示,OCC内部电路模型

上图所示,片上时钟控制器(OCC)工作模式:功能模式

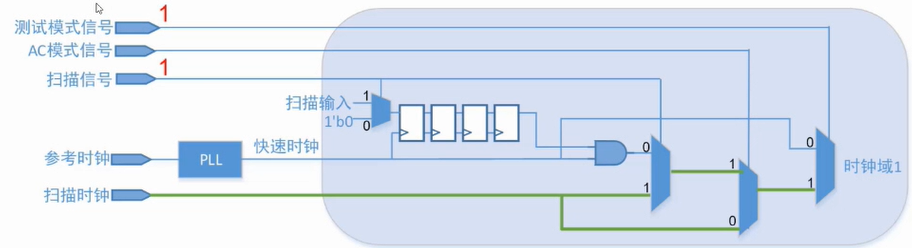

上图所示,片上时钟控制器(OCC)工作模式:扫描模式

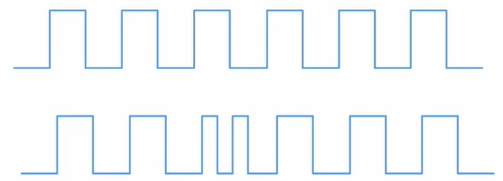

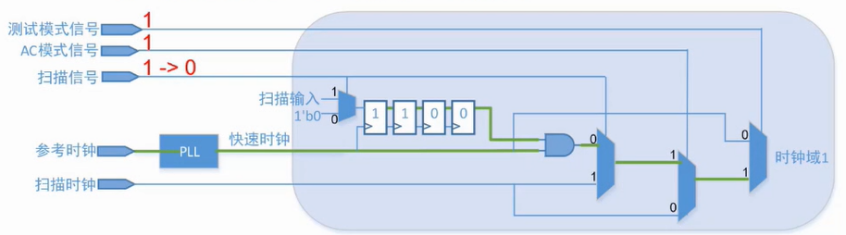

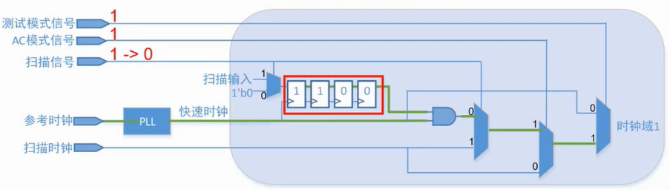

片上时钟控制器(OCC)工作模式:AC捕获模式,在扫描模式下,将OCC扫描寄存器配置成某个状态,比如1100.

最终OCC产生的捕获时钟及电路配置如下图所示:

波形图如下:

四、实训

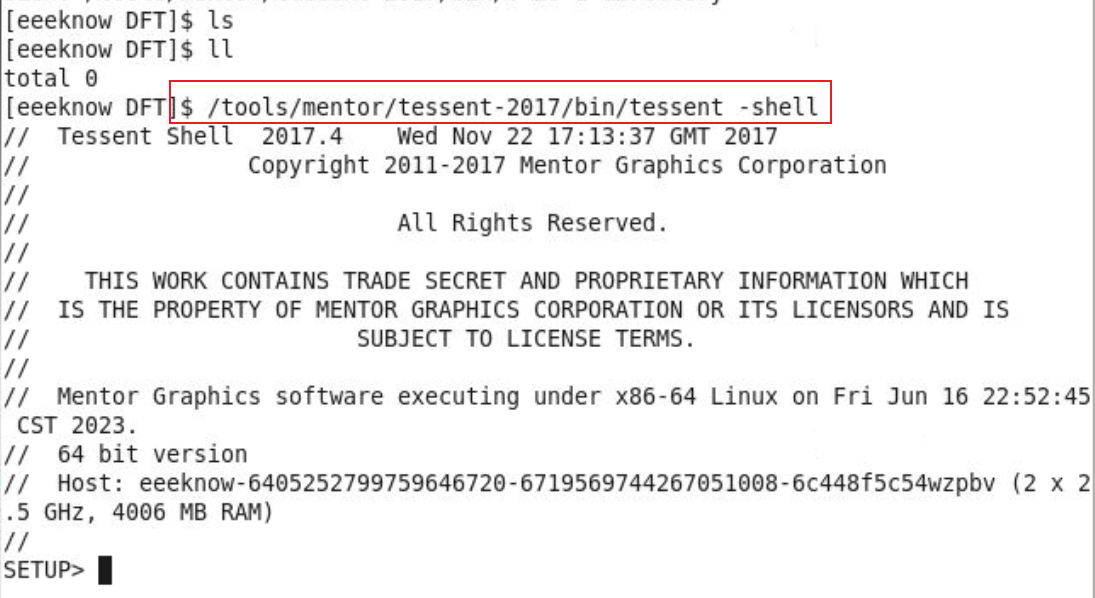

1.软件介绍

Tessent Shell是Mentor公司的DFT工具,它集成了很多DFT相关的特性,包括:

- 编辑网表

- 分析扫描结构,插入扫描链

- 生成测试向量,仿真

- 基于芯片测试反馈的结果进行诊断

- IJTAG相关的ICL抽取以及PDL retargeting工作

- 解、压缩逻辑EDT的插入。

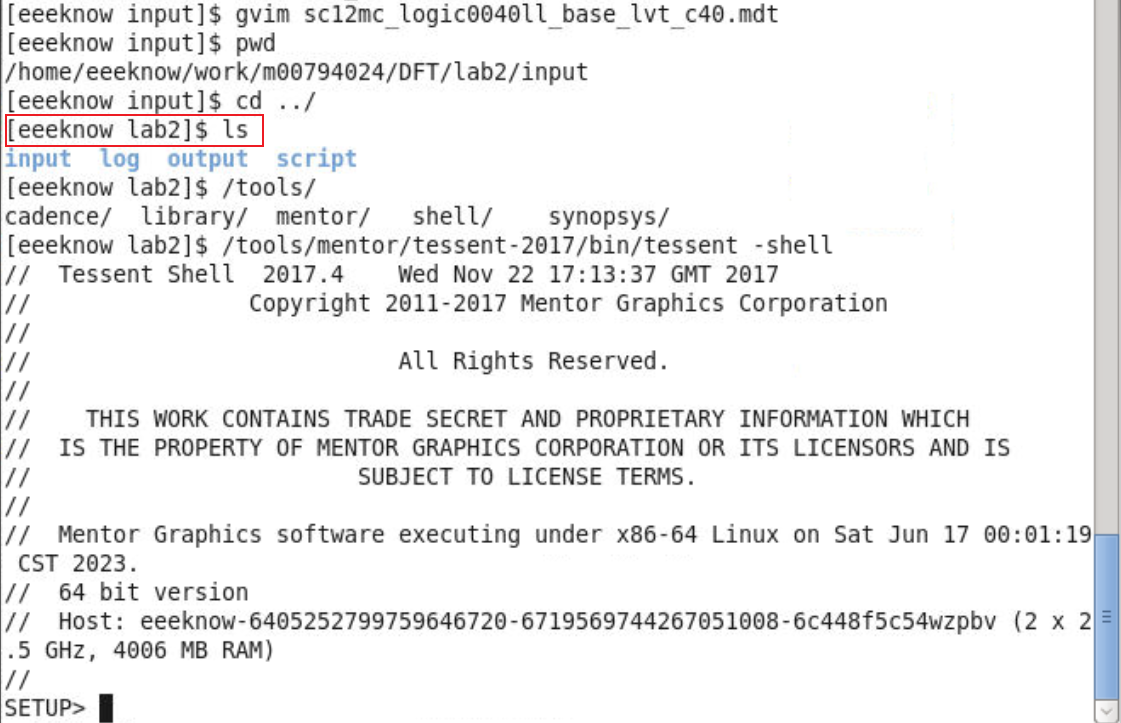

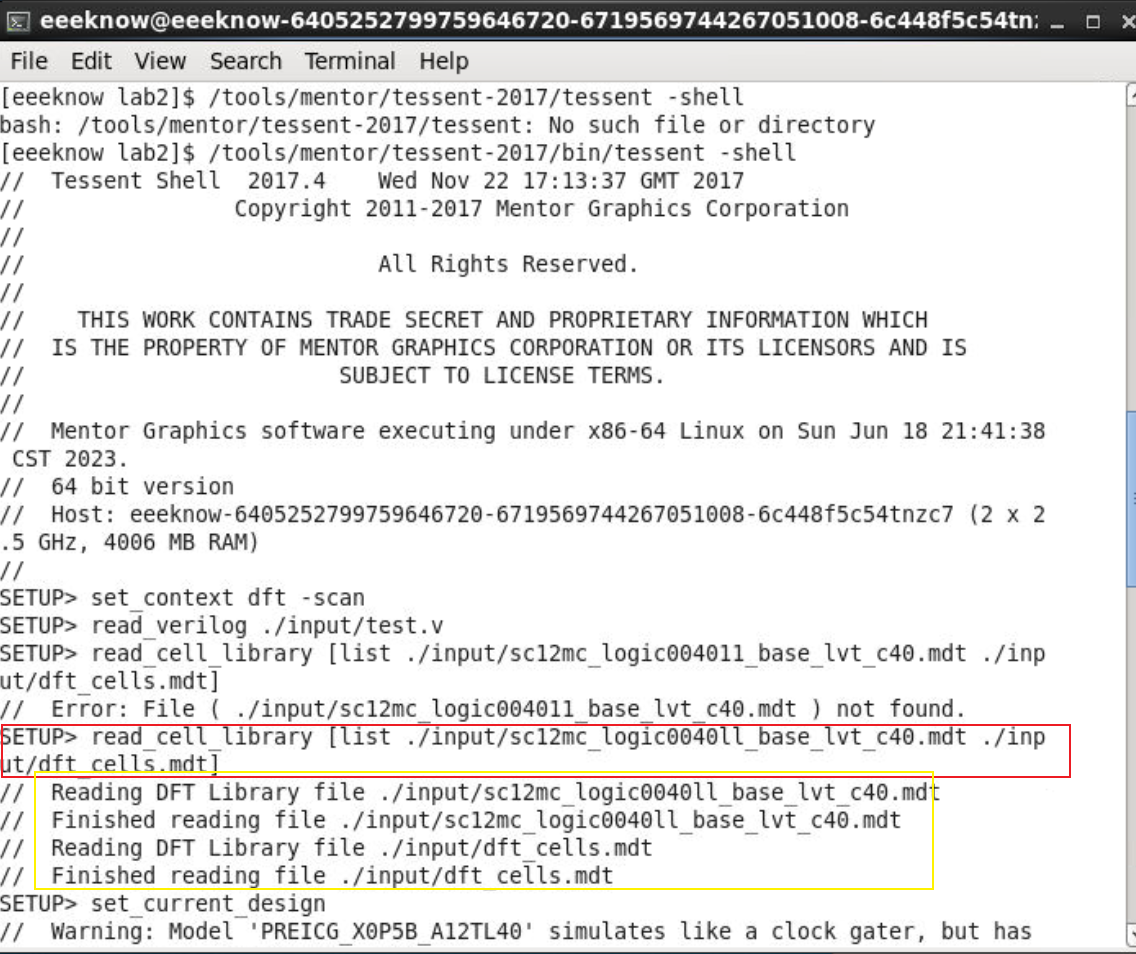

在cshell中,只需要用以下命令行来打开tessent,在进入tessent之后,以上每个特性都可以用相应的context命令行来激活,在接下来的几个章节会详细介绍每一个特性对应的context命令行。

#Tessent可执行文件位于: ls /tools/mentor/tessent-2017/bin/tessent #在自己的工作目录下打开tessent cd <your_working_dir> /tools/mentor/tessent-2017/bin/tessent -shell

请注意刚启动软件时,左边的字符:

SETUP>

Teseent有三种模式,分别为:

- SETUP :Tool启动时默认的模式。用于选择需要的工具特性(如上),或用来读入网表和库文件。

- ANALYSIS:检查、分析网表,向量生成,仿真等。

- INSERTION:对网表进行操作,比如扫描链插入等。

一般而言,工具在特定的流程中会自动切换需要进入的模式(在下面的扫描链插入流程中可以仔细观察),用户也可以使用命令行设置需要的模式:

![]()

注意,上面这个命令只有在已经选择相应的context后才能使用,否则会报错。

2.扫描链插入的流程

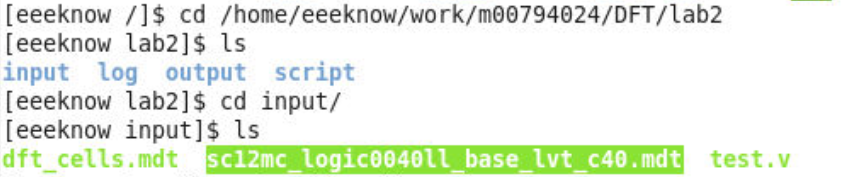

2.1 综合后网表与库文件

#复制我们为你准备好的lab到你的工作目录 cp -rf /home/eeeknow/data/dft/labs/lab2 <your_working_dir> #进入工作目录下的数据目录 cd <your_working_dir>/labs/lab2 #在该数据目录下,有一个input目录,该目录用来存放本次实验需要用到的综合网表(扫描链插入之前),DFT库文件。 ls input/

input文件如下:

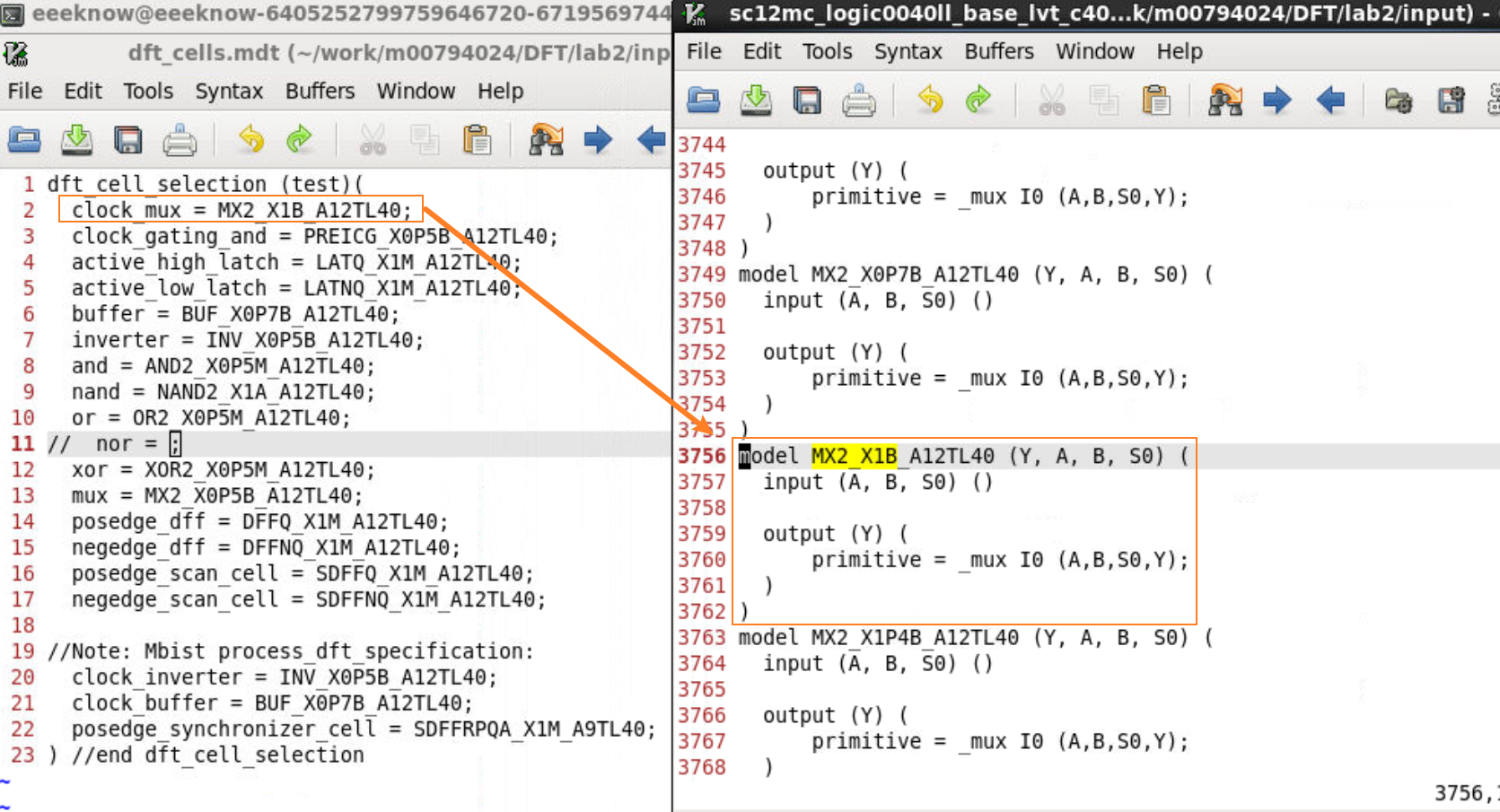

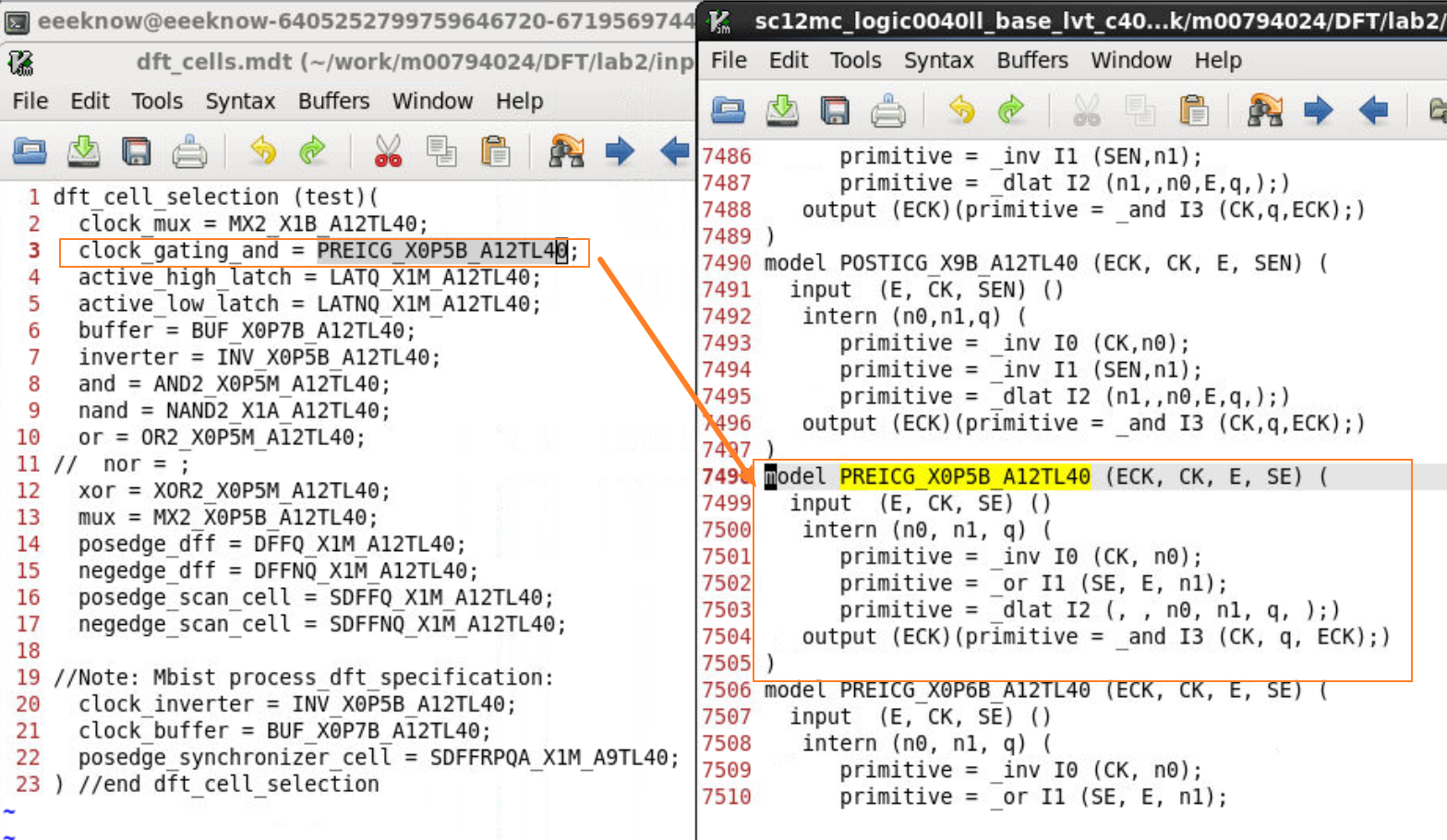

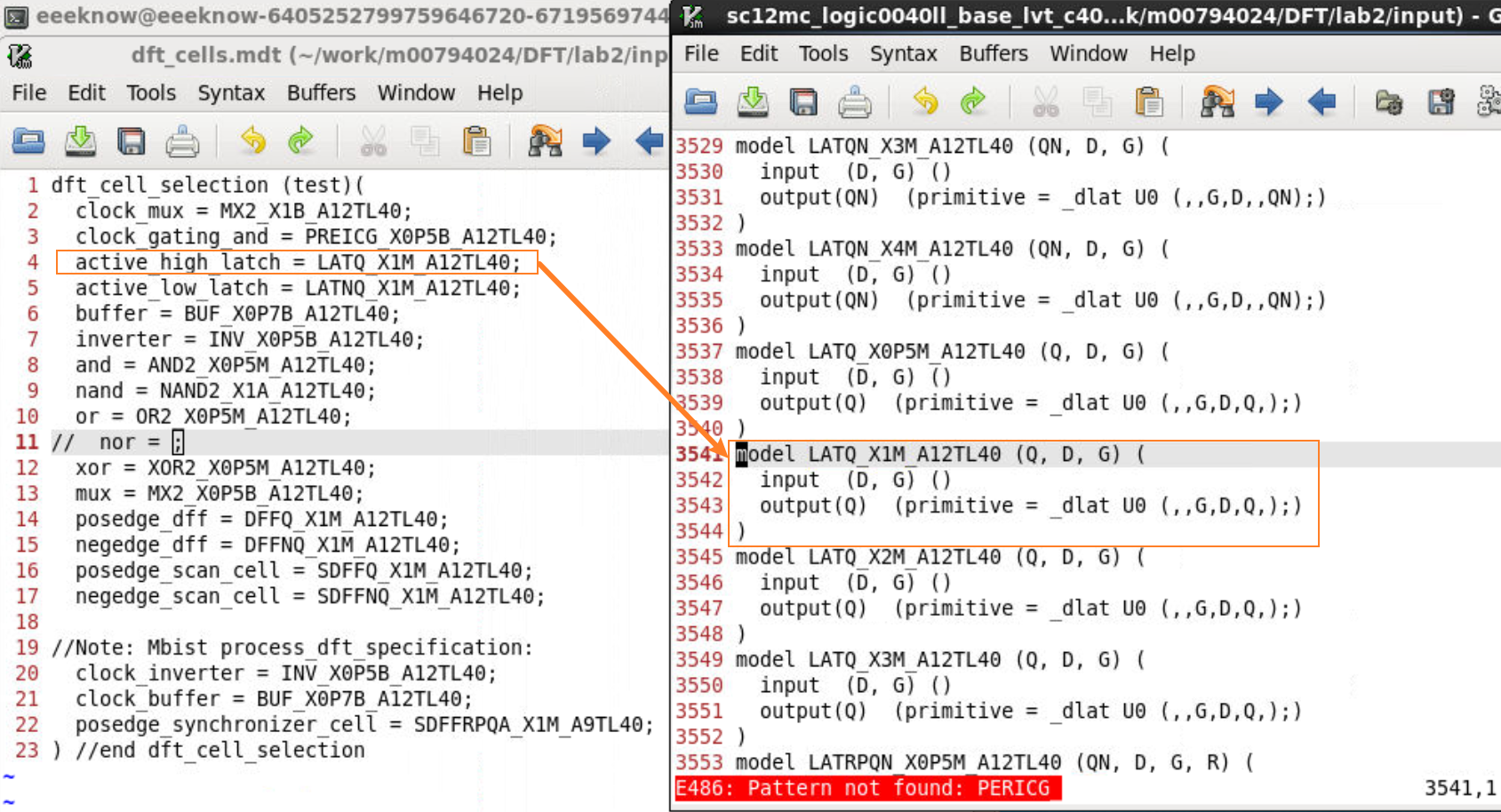

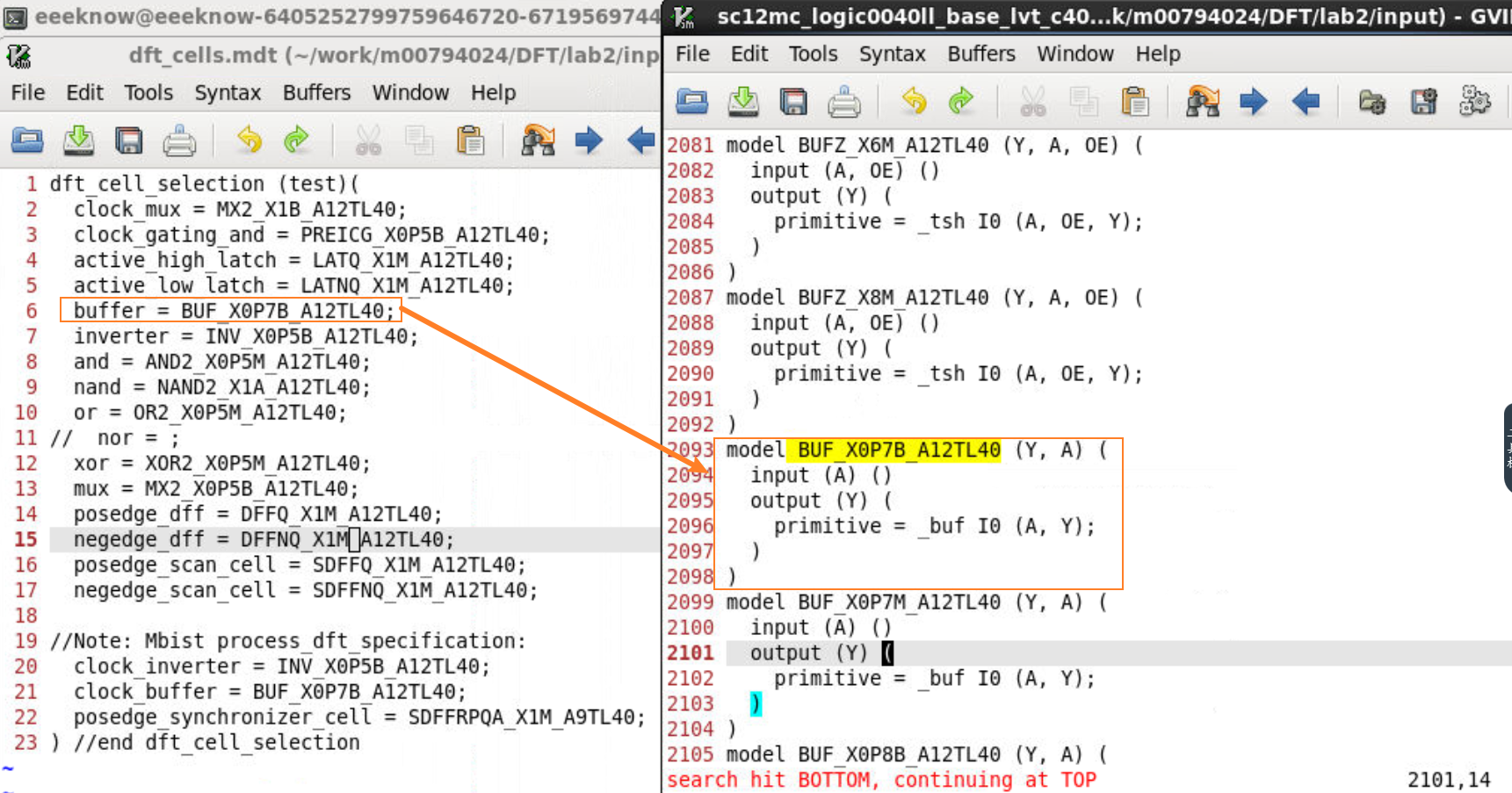

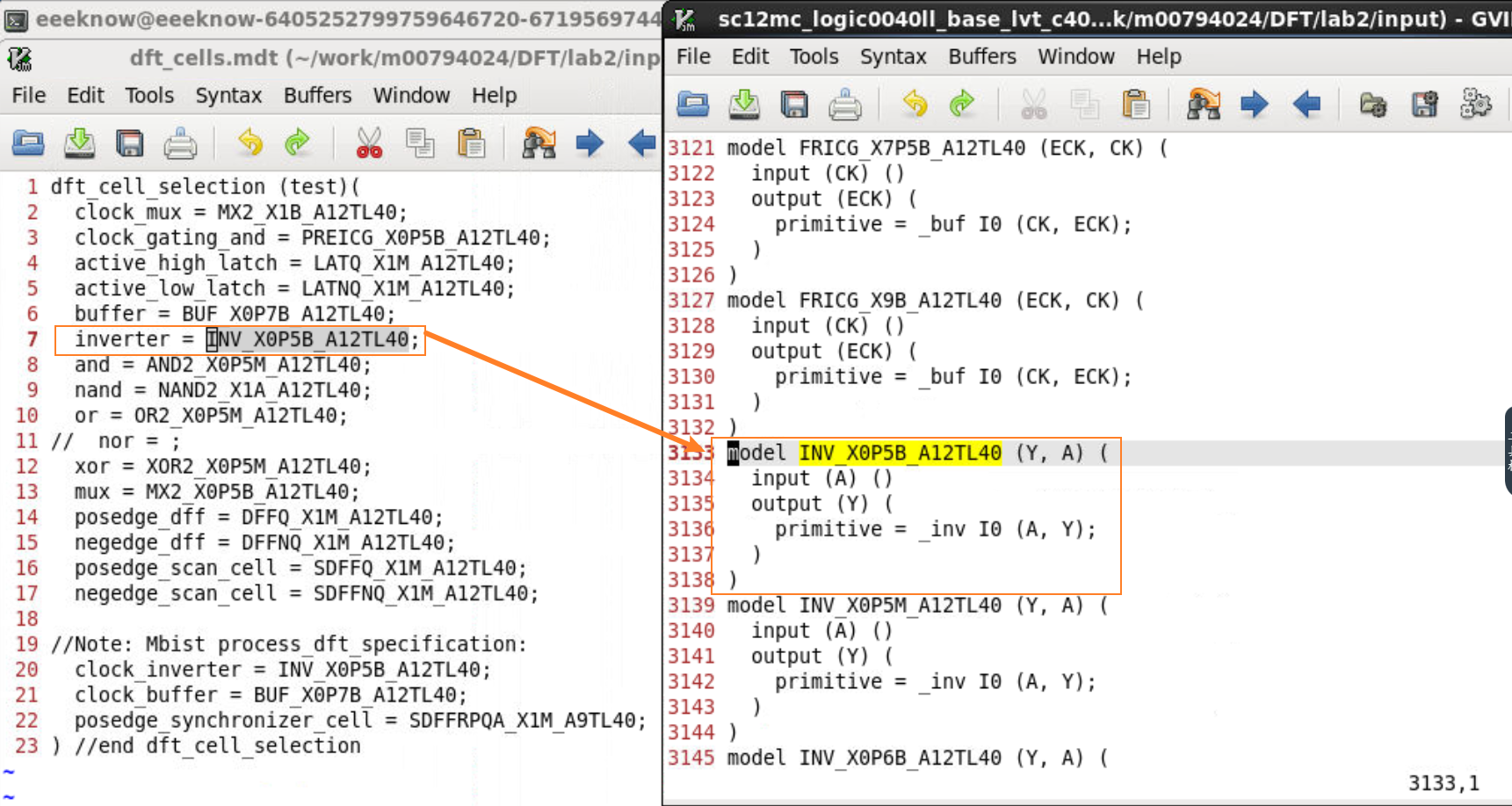

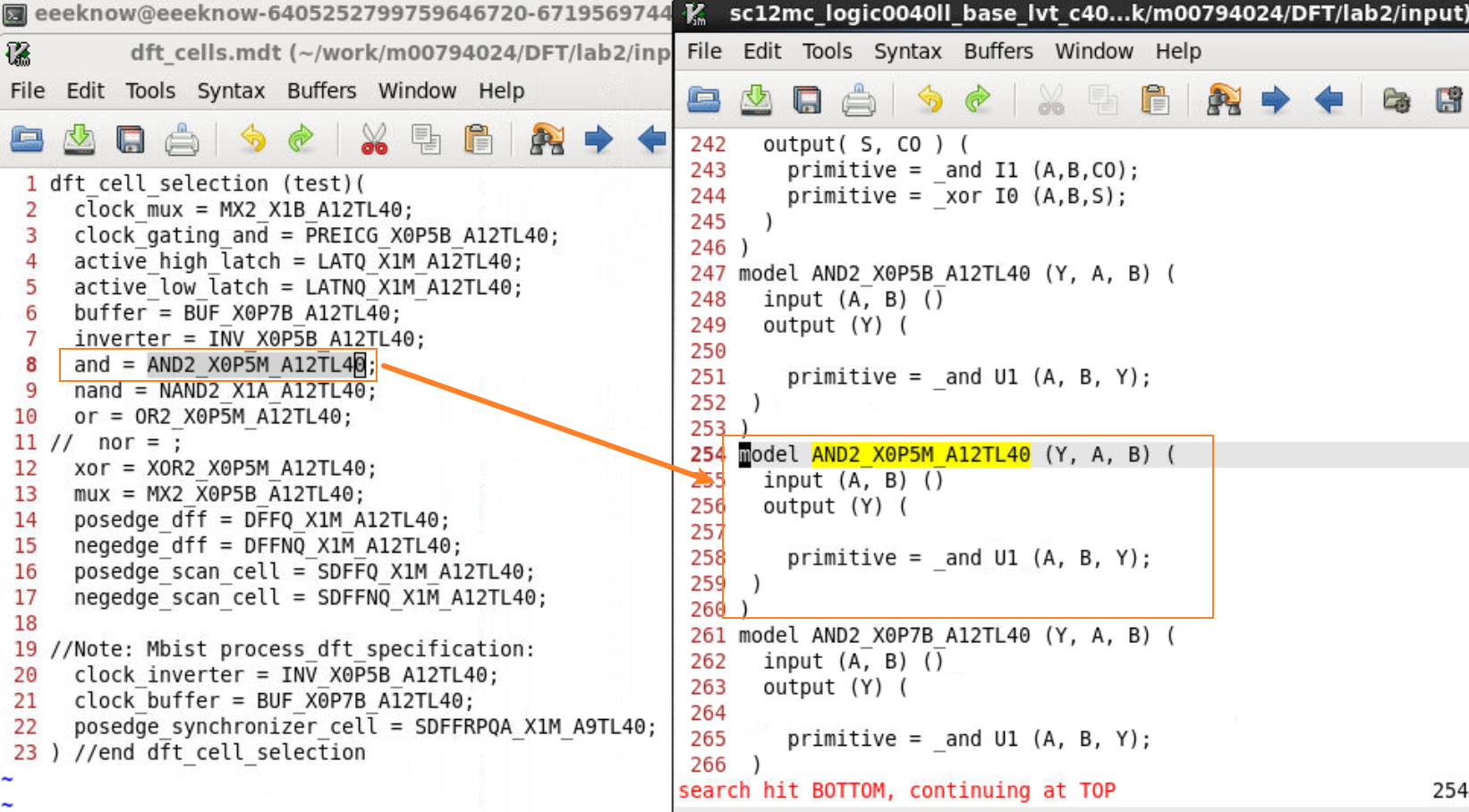

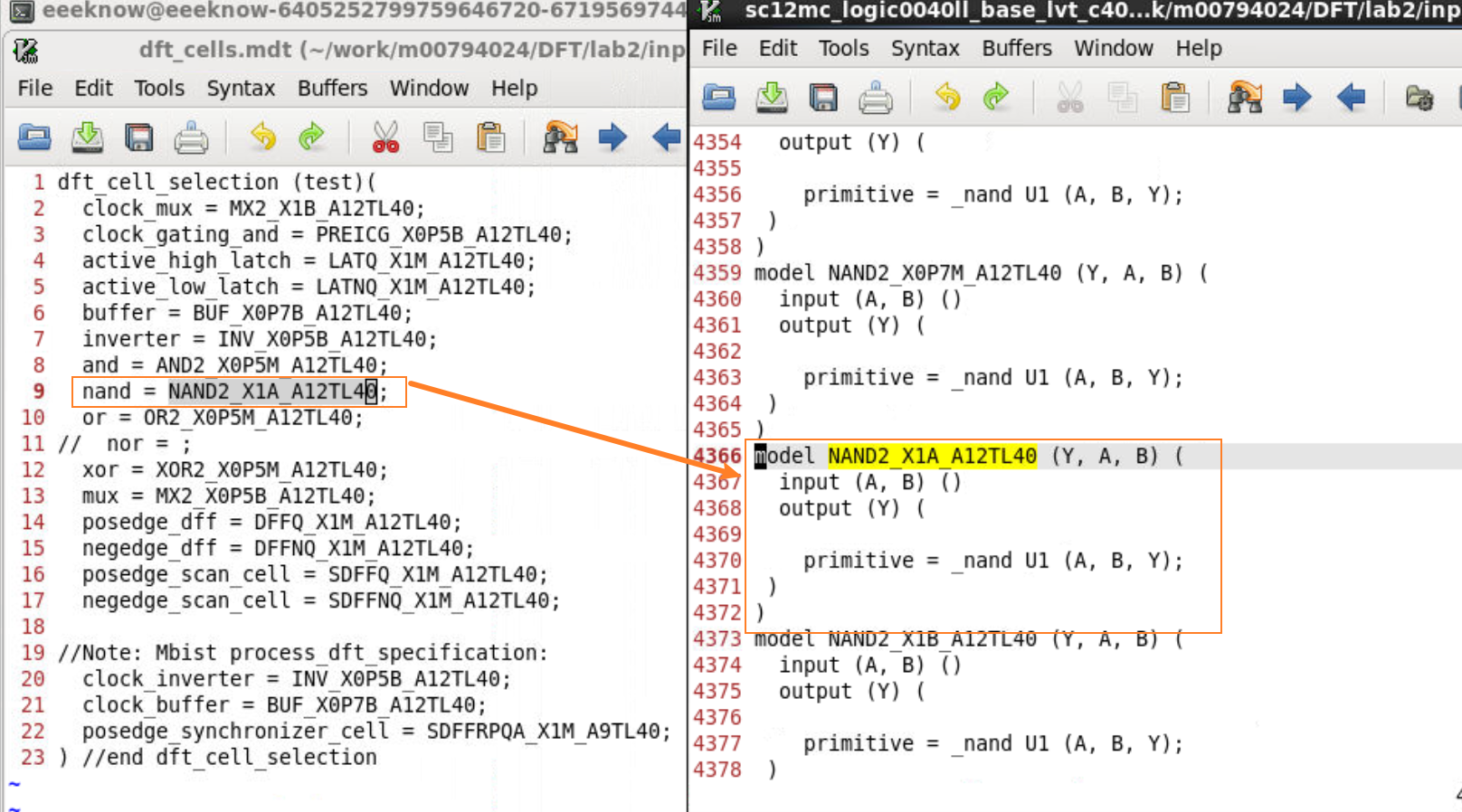

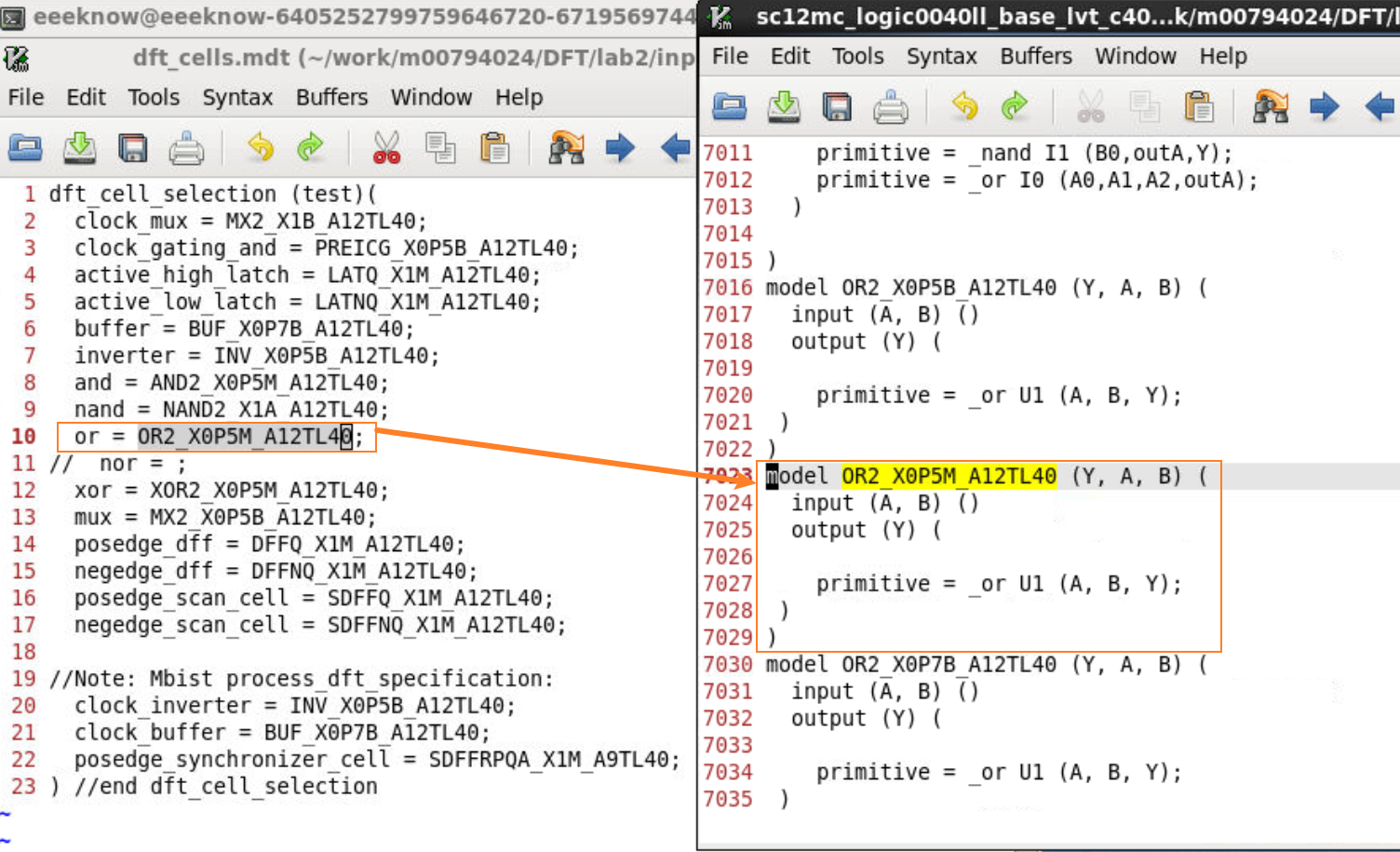

- sc12mc_logic0040ll_base_lvt_c40.mdt : 标准单元的DFT库文件(扫描寄存器的DFT基本单元类型)

- dft_cells.mdt : 告诉Tessent,在需要插入逻辑时,从这个文件里选择相应功能的cell类型。

- test.v:输入网表文件

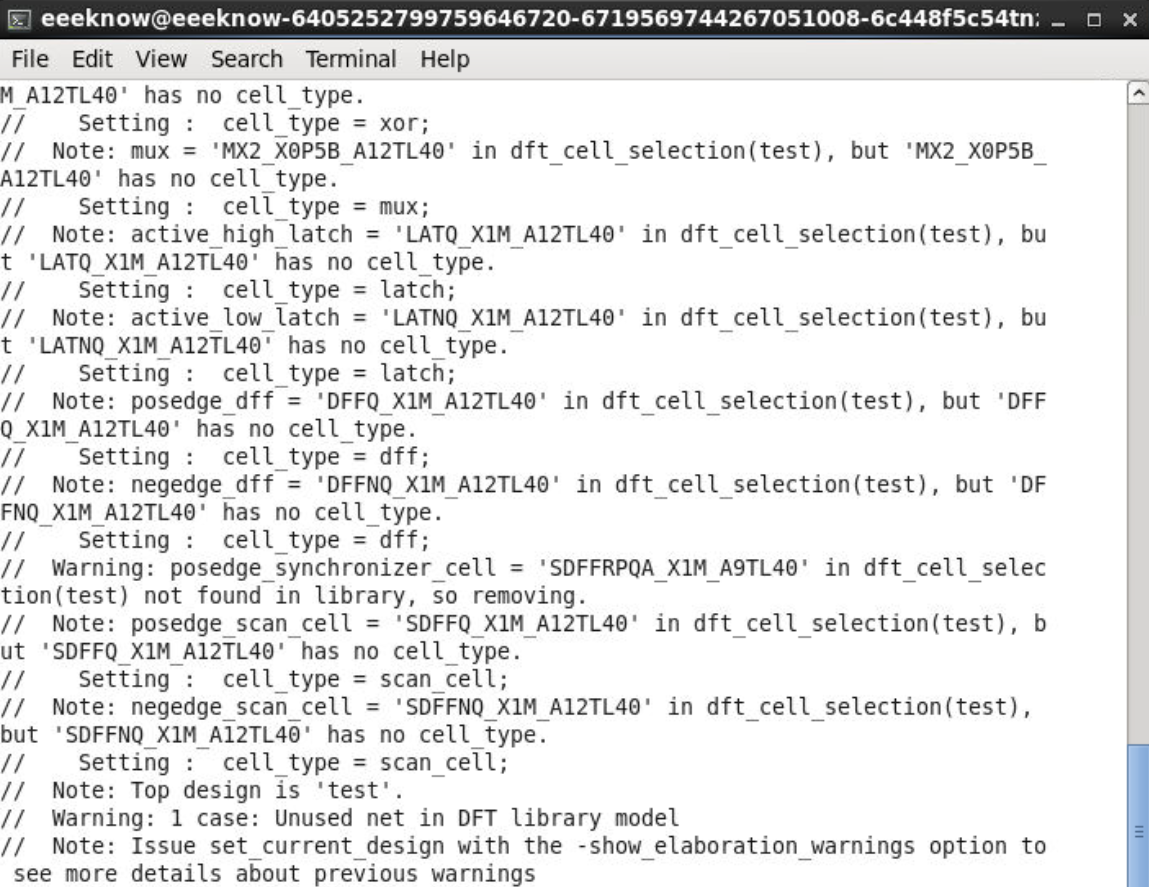

打开标准单元DFT库文件,熟悉一下DFT库文件里对寄存器的定义。注意观察SDFF和DFF区别,比如:SDFFNQ_X1M_A12TL40和DFFNQ_X1M_A12TL40。

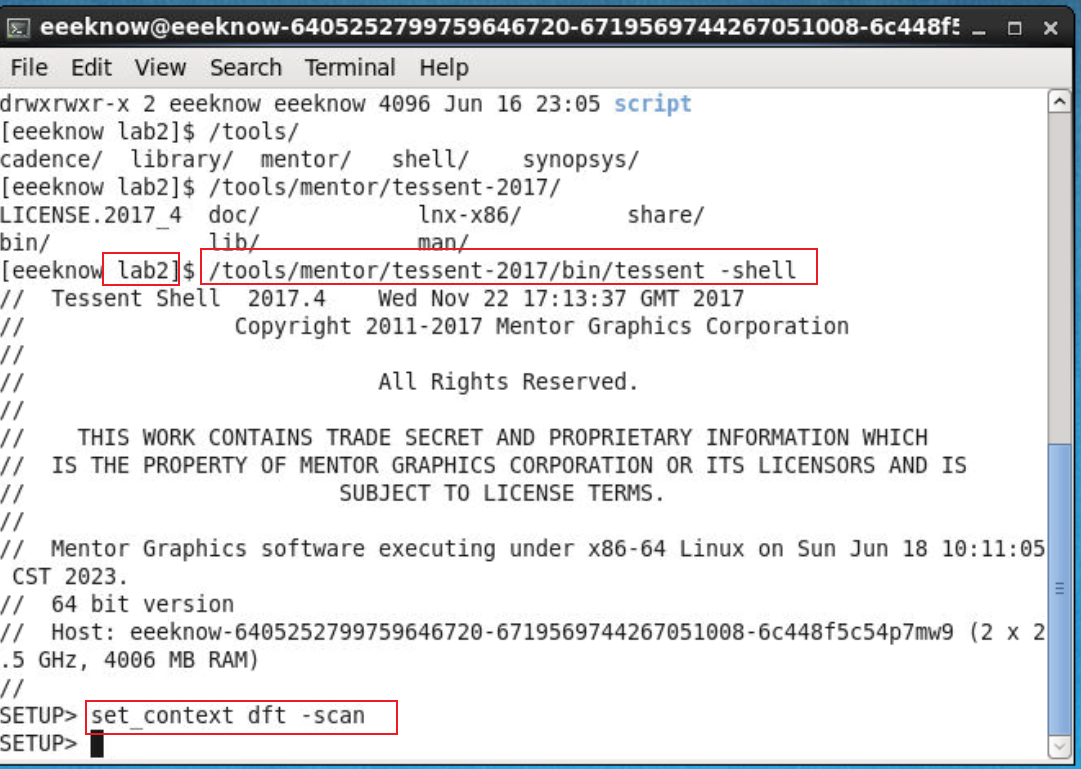

2.2 启动工具

#启动Tessent cd <your_working>/labs/lab2 /tools/mentor/tessent-2017/bin/tessent -shell

该章节要插入扫描链,需要设置以下context:

SETUP>set_context dft -scan

2.3 读入网表和库文件

执行以下命令行:

#指定网表文件 SETUP>read_verilog ./input/test.v SETUP>read_library [list ./input/sc12mc_logic0040ll_base_lvt_c40.mdt ./input/dft_cells.mdt]

请注意,在执行这两个命令之后,工具并没有真正开始读入和解析网表,我们需要执行以下的命令行来让工具读入网表,相当于综合时的elaborate design。

#读入网表文件

SETUP>set_current_design

执行set_current_design后,工具开始读入网表,假如网表有什么语法错误,工具会报错,若网表没有问题,工具执行完后如下:

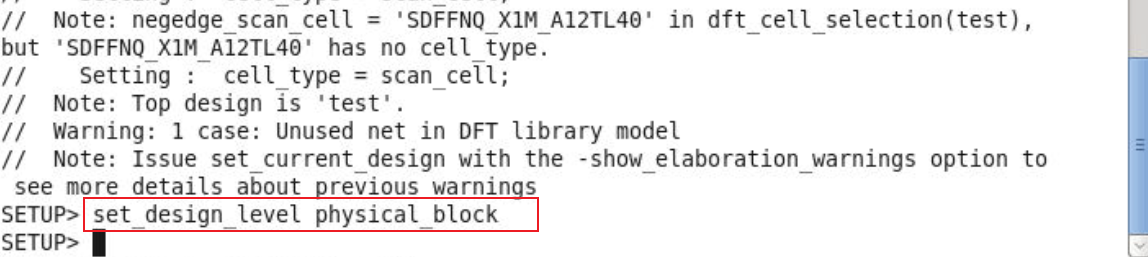

本次实验设定为一个小block,需要通过如下命令行告诉工具,当前层次结构为block,而非top:

SETUP>set_design_level physical_block

在之后章节中,会利用这个命令告诉工具在top level 插入某些逻辑。

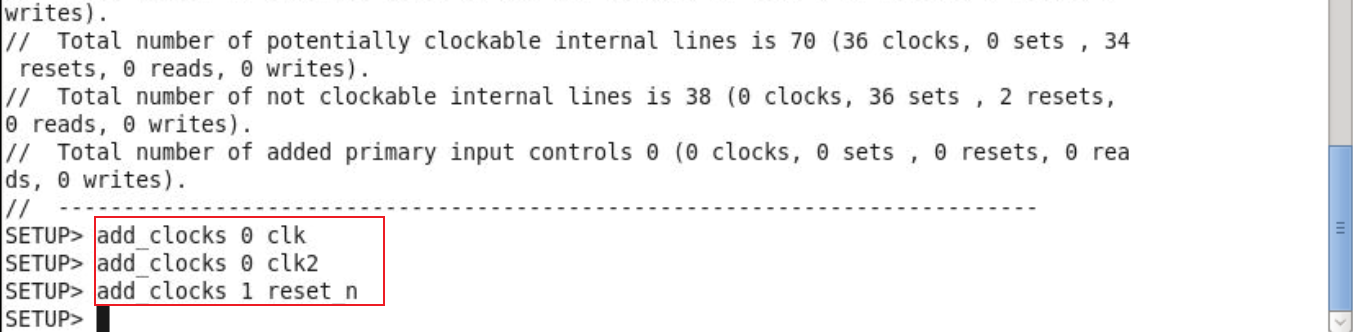

2.4 指定时钟、复位信号

对于一个普通的数字电路设计,时钟和复位、置位信号是必不可少的,我们通过命令行告诉工具,这些信号在inactive状态的值。

如果第一次接触这个陌生的block,大家可能不清楚有几个时钟或者复位信号,我们可以通过下面的命令来让工具自动的侦测相关信号:

SETUP>analyze_control_signals

工具分析完网表后,会报出如下信息:

根据上面的信息,我们可以知道,该block中共有两个时钟输入:

/clk

/clk2

它们的off-state都为0.

另外,还有一个reset端:

/reset_n

它的off-state为1.

【问题】:off-state指的是什么?

这个实验课程用到的block总共有2个时钟输入端,分别为clk和clk2,一个复位信号reset_n。

analyze_control_signal这个命令在这里很有用,可以帮大家分析出相关的信息。但是,对于复杂的设计,工具不一定能准确的分析出所有的信号,在实际项目中,建议大家可以用这个命令做辅助性分析,并和电路设计人员咨询所有的时钟、置位、复位信号,以防工具漏掉某些信号,导致后续的DRC检查报错。

【问题】DRC violation指的是什么?

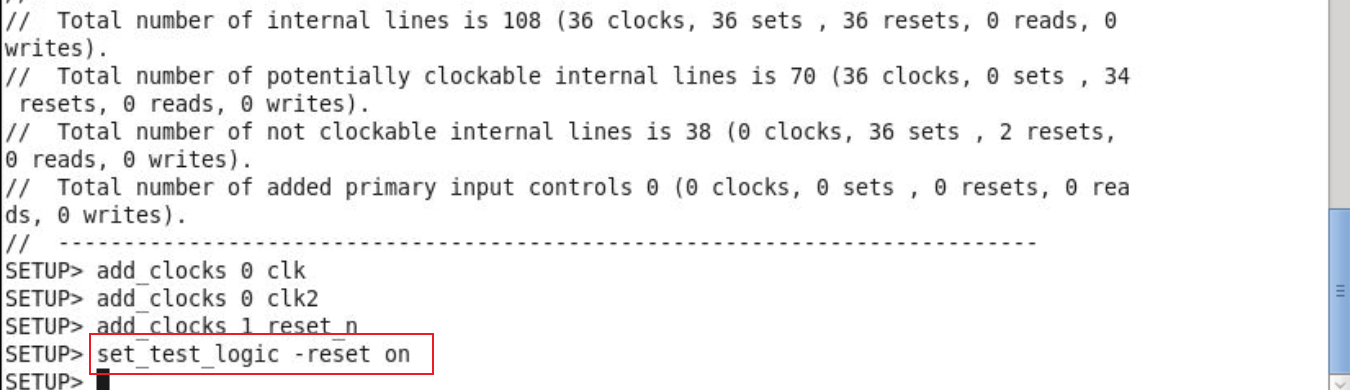

另外,为了让工具在插入扫描链的时候自动修复时钟和复位信号上可能存在的DRC violation,我们可以打开如下选项:

SETUP>set_test_logic -reset on

2.5 进行DRC检查

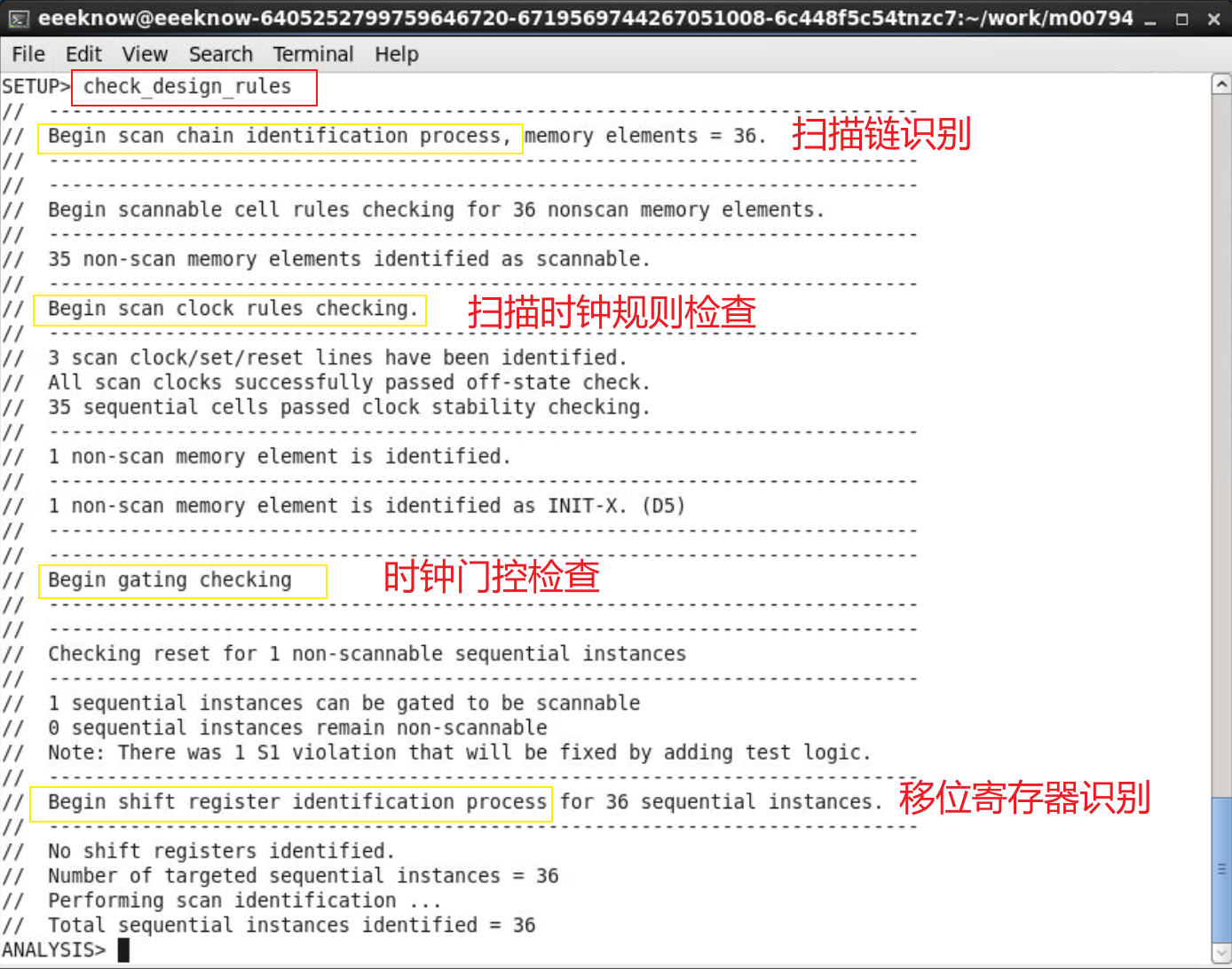

在指定所有的时钟、复位信号后,我们需要对这个block进行扫描链插入之前的DRC规则检查。

SETUP>check_design_rules

DRC规则检查会报告当前设计里有多少时序单元,是否有DRC违例。

如果有DRC违例,工具会报出详细的错误,我们也可以借助多种手段来分析DRC违例(后续有章节专门介绍)。这节课程里用到的设计是符合扫描链插入的DRC检查的,没有违例。

大家请留意,在DRC检查通过之后(没有报DRC warning或者error),Tessent的system模式从SETUP自动跳转为ANALYSIS。在实际工作中,如果工具发现严重的DRC错误,可能会影响后续的扫描链插入,system模式是不会跳转到ANALYSIS的,只有DRC检查通过的情况下,工具才会自动跳转到ANALYSIS模式。

2.6 插入扫描链

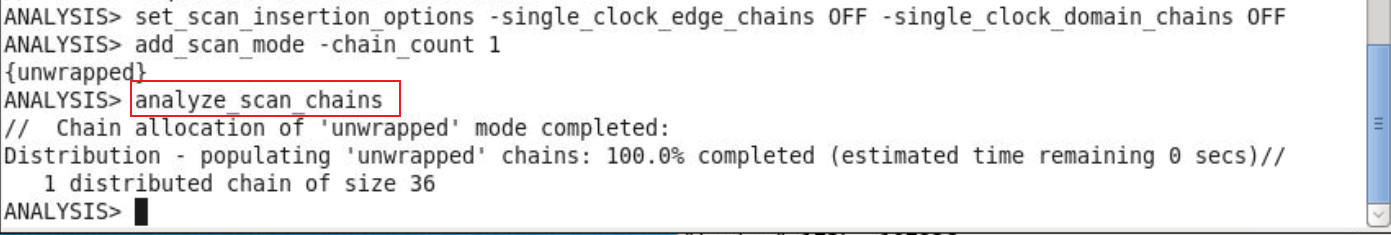

在DRC检查通过后,可以按照需要插入扫描链。首先,我们可以通过set_scan_insertion_options来配置工具串链的行为,比如,不同时钟域的寄存器是否可以串到同一条扫描链中,不同时钟沿触发的寄存器是否可以串到同一条扫描链中等等。另外,我们还可以指定扫描链的条数。

#指定工具串链行为 ANALYSIC>set_scan_insertion_options -single_clock_edge_chains OFF -single_clock_domain_chains OFF #指定扫描链条数 ANALYSIS>add_scan_mode -chain_count 1

在做配置时,我们需要保证上面的设置和实际设计不会有过约束的情况出现。举个例子,这个block里共有两个时钟域:clk & clk2。如果我们指定了-single_clock_domain_chains ON,意味着工具至少会建两条扫描链,一条是clk时钟域的寄存器,一条是clk2时钟域的寄存器,如果此时你指定add_scan_mode -chain_count 1,也就是要求工具只建一条扫描链,这样冲突的设置就会导致工具在把寄存器分配到扫描链上时报错。

【问题】clock_edge与clock_domain有什么区别?为何同时设置?

#工具把寄存器分配在扫描链上

ANALYSIS> analyze_scan_chains

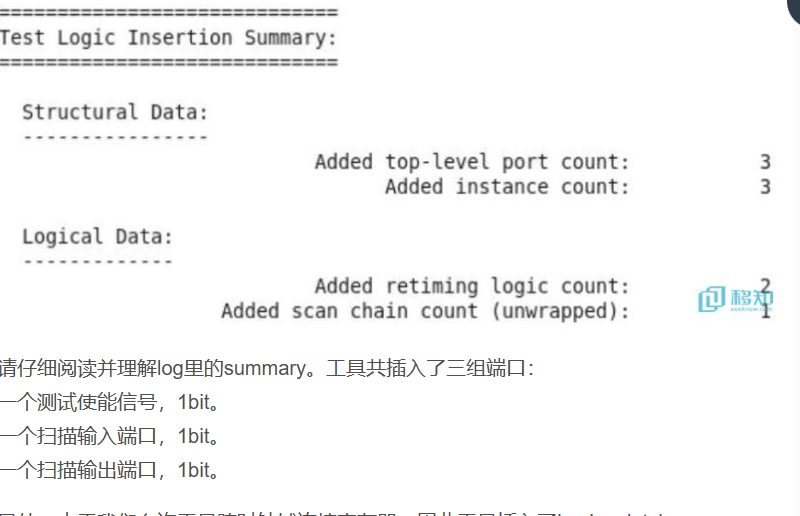

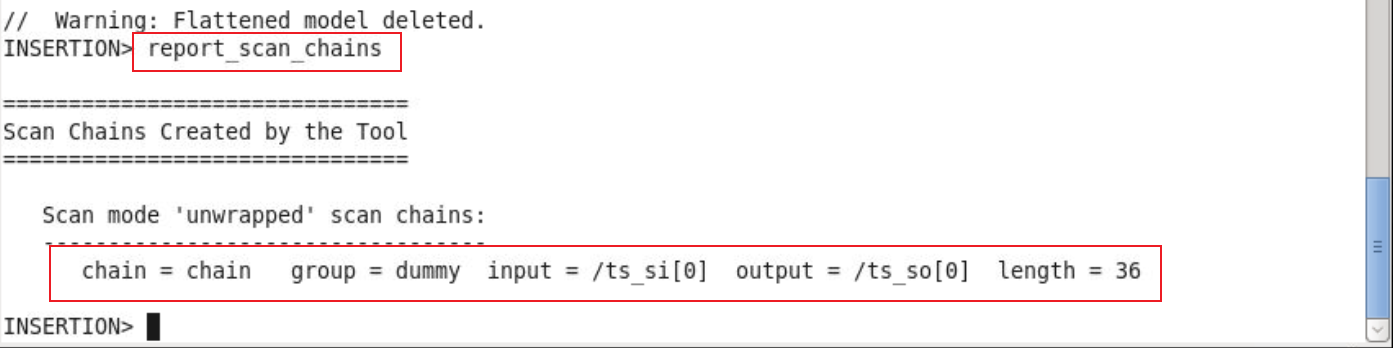

从log里可以看出,工具会插入1条chain,chain的长度为36.

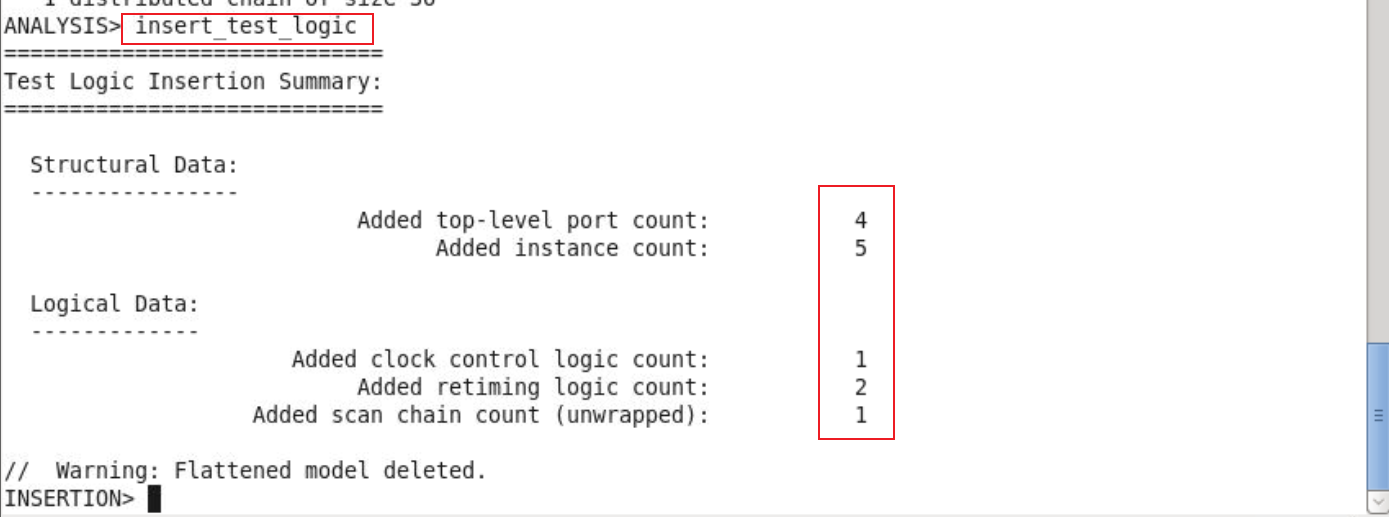

然后我们执行下面的命令行,让工具插入必要的DFT逻辑,如跨时钟域的lockup latch,扫描端口等。

#工具插入测试逻辑

ANALYSIS> insert_test_logic

这里实际操作生成的log与实例中的log不一致。

【问题】实操中显示工具插入4个端口与5个例化,这个端口和例化如何查看?

可以通过命令报告扫描链的情况,例如:

#报告扫描链

INSERTION> report_scan_chains

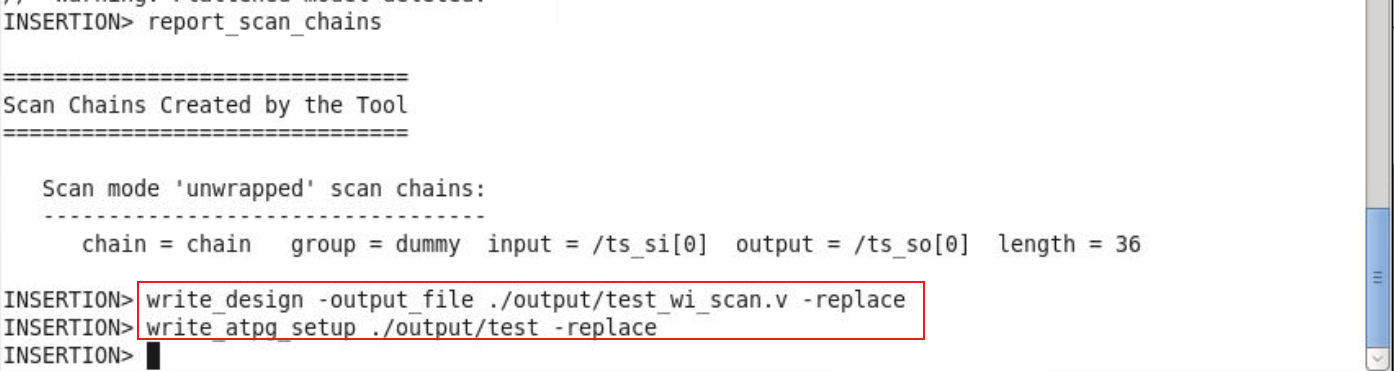

2.7 保存扫描链网表

在扫描链插入之后,我们需要保存网表和其他ATPG文件。

SETUP>write_design -output_file ./output/test_wi_scan.v -replace

SETUP>write_atpg_setup ./output/test -replace

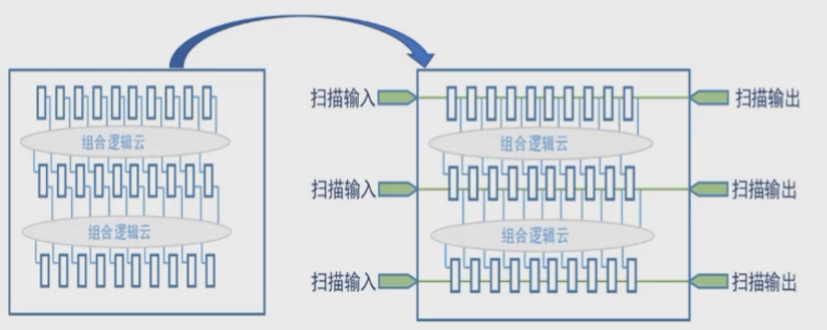

打开./output/,可以看到新增了4个文件: