SPI

SPI的特性是工作方式众多,有标准SPI和QSPI:

QSPI: QSPI 是 Queued SPI 的简写,是 Motorola 公司推出的 SPI 接口的扩展,比 SPI 应用更加广泛。在 SPI 协议的基础上,Motorola 公司对其功能进行了增强,增加了队列传输机制,推出了队列串行外围接口协议(即 QSPI 协议)。使用该接口,用户可以一次性传输包含多达 16 个 8 位或 16 位数据的传输队列。一旦传输启动,直到传输结束,都不需要 CPU 干预,极大的提高了传输效率。与 SPI 相比,QSPI 的最大结构特点是以 80 字节的 RAM 代替了 SPI 的发送和接收数据寄存器。

Dual SPI Flash: 对于 SPI Flash 而言全双工并不常用,可以发送一个命令字节进入 Dual 模式,让它工作在半双工模式,用以加倍数据传输。这样 MOSI 变成 SIO0(serial io 0),MISO 变成 SIO1(serial io 1),这样一个时钟周期内就能传输 2 个 bit 数据,加倍了数据传输。

Quad SPI Flash: 与 Dual SPI 类似,Quad SPI Flash增加了两根 I/O 线(SIO2,SIO3),目的是一个时钟内传输 4 个 bit 数据。

所以对于 SPI Flash,有标准 SPI Flash,Dual SPI Flash, Quad SPI Flash 三种类型。在相同时钟下,线数越多传输速率越高。

二 SPI的Motorola SPI 通信协议和TI的SSP通讯协议:主要区别就是片选的不同:

Motorola SPI:通讯期间片选一直低电平(有效)

SSI(Synchronous Serial Interface):启动通讯时片选先置高,维持图个CLK周期然后拉低。

双机通讯问题:

对于全双工SPI通信,主从机之间的收发本质上是两个移位寄存器的数据交换。这里需要注意主机读的情况:主机想读多少数据就要向从机写多少数据,要考虑:

1.主从机SPI的底层配置;

2.通信协议的设计;相对比较简单,根据自己的需求设计数据帧格式

3.主从机整体框架搭建;主要是关于中断

如果按照下面的读写,如果从机突然掉电,主机就一直等待。

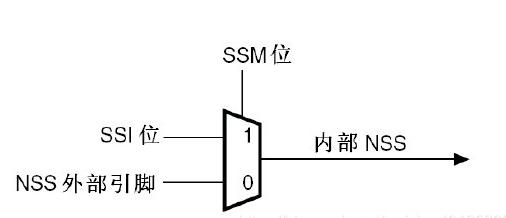

NSS分为内部引脚和外部引脚。

NSS外部引脚可以作为输入(一般用作硬件方式从机的片选I)信号或者输出(一般用于主SPI去片选与之相连的从SP)信号。

这张图的解释。对于从机SPI寄存器CR1中的SSM位,置1时代表软件片选,置0时代表硬件片选。上图的意思是;如果SSM置0,则内部NSS由外部NSS引脚电平确定;如果SSM置1,内部NSS由SSI决定,通过CR1中的SSI位来驱动,此时外部NSS引脚无效了,随你怎么用,哪怕是复用为SPI_CS也起不到任何作用,因为内部的NSS电平是由SSI位决定的,注意它不是简单的“与门”。

对于从机而言,如果SSM=0,即硬件片选,则CS引脚必须连接到主机的CS上在CS=0时被其控制。在CS=1时被释放。才不会触发中断和接收数据。即从机必须设置SSM=0。

主机是软件片选还是硬件片选:对于一主多从的情况主机用软件片选,从机用硬件片选。

推荐软件片选,SSI=1维持主机地位。

如果主机选择了硬件模式,一般都会以为片选引脚会在发送时自动拉低,在结束发送时自动拉高,但是实际上,手册上的说法是:使能SPI后片选引脚就会输出低直到关闭SPI(对于我的使用场景,就算你一直拉低也没什么哈)。

从机如果软件片选,随便指定一个GPIO为外中断连接到主机的CS上,进入中断后,通过SPI_NSSInternalSoftwareConfig(User_SPI,SPI_NSSInternalSoft_Reset)。来控制CR1寄存器的SSI=0来选择片选,退出时来搞SSI=1取消片选,非常麻烦。

按照标准的SPI协议,当SPI被配置为主机模式后,通过SPI对从设备进行操作时,其NSS应该自动置低,从而选中(使能)从设备;一旦不对从设备进行操作,NSS立刻置为高。

但是,我在实际调试过程中却发现:STM32 SPI NSS无法自动实现跳变。

ST官方技术人员也证实:STM32 SPI NSS是不会自动置位和复位的。按照官方说法,ST已经将其列入了改进计划。

引申:其它的SSOE支持多主或动态切换:

每个SPI设置成硬件NSS,通过NSS检测,一旦发现系统中无NSS低信号,自己就输出低,从而成为主机;当系统中有NSS低信号时(及已经有其它SPI宣布为主机),自己就配置为从机。所谓的hard模式的NSS,实际就是为了实现多机间通信的。

主机要想发数据:备注:都空闲时M_TX_PIN=S_TX_PIN=0,高有效。

- 先读S_TX_PIN,如果为高则退出,否则继续。

- 在将M_TX_PIN=1,延时一小会儿,再读S_TX_PIN,如果为高则M_TX_PIN=0退出,否则进入临界区保护进行发送操作。

- 发送完成M_TX_PIN=0退出。

从机操作类似。

硬件SPI:

STM32的NSS(输入输出、软硬件模式):

硬件一对一方式(2中方法):

1STM32的NSS=VCC;从机的NCC=GND

2STM32的NSS接到从端的NSS,然后使能SPI_CR2的SSOE位。当SSOE为1时,并且SPI处于主模式控制时,NSS就输出低电平,也就是拉低,自动选择从端。

软件模式(NSS分内部NSS和外部NSS):

主机(STM32MCU):设置SPI_CR1寄存器的SSM(使能软件管理NSSq位)为1和SSI(内部NSS拉高这样STM32的SPI为于主机)位为1,此时外部NSS可以配置成一般的GPIO.

从机(STM32MCU):SPI_CR1寄存器的SSM(使能软件管理NSSq位)为1和SSI=0;

若从机是非MCU则可以将从机CSS=GND或者一条IO(也可以是NSSPIN即外部NSS)来控制从机CSS

http://blog.sina.com.cn/s/blog_6d0c454d0101aax7.html

软件SPI:速度慢,但比较灵活。一主多从比较方便。

MISO/MOSI与SI/SO:

注意主从机的MISO和MOSI是不交叉的,即主机的MOSI对从机的MOSI.

SI/SO:意思是串行输入和输出,单这个是不能确定怎么连接,需要知道标注SI的设备是做主机还是从机,若是主机表示输入即MISO.

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· .NET Core 中如何实现缓存的预热?

· 从 HTTP 原因短语缺失研究 HTTP/2 和 HTTP/3 的设计差异

· AI与.NET技术实操系列:向量存储与相似性搜索在 .NET 中的实现

· 基于Microsoft.Extensions.AI核心库实现RAG应用

· Linux系列:如何用heaptrack跟踪.NET程序的非托管内存泄露

· TypeScript + Deepseek 打造卜卦网站:技术与玄学的结合

· Manus的开源复刻OpenManus初探

· AI 智能体引爆开源社区「GitHub 热点速览」

· 三行代码完成国际化适配,妙~啊~

· .NET Core 中如何实现缓存的预热?