【转载】MOS开关(verilog)

MOS开关

一. MOS开关

1. NMOS 源极(d)接Gnd

一般情况下,可认为晶体管受栅极(g)电平VG的控制(control).

1). VG=H,源极(s)与漏极(d)接通;

2). VG=L,源极(s)与漏极(d)断开.

源极(s)与漏极(d)接通, 则漏极(d)被下拉到Gnd.

2. PMOS 源极(d)接VDD

1). VG=H,源极(s)与漏极(d)断开;

2). VG=L,源极(s)与漏极(d)导通.

源极(s)与漏极(d)接通, 则漏极(d)被上拉到VDD.

3. CMOS

CMOS电路中包括NMOS所组成的部分为下拉网络(pull-down network, PDN), PMOS所组成的部分为上拉网络(pull-up network, PUN).

优点:无论输入电平是高电平还是低电平, 电路中都没有电流通过, 即CMOS电路在静态下没有功耗.

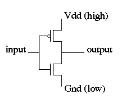

举例:CMOS反相器

其中PMOS为上拉器件, 导通即把输入上拉至VDD; NMOS为下拉器件, 导通即把输入下拉至Gnd.

二. Verilog描述

在Verilog中, 关键字nmos和pmos用作定义两种类型的MOS开关.

1. 实例化

nmos n1(output, input, control); // 实例化(调用)一个NMOS开关

pmos p1(output, input, control); // 实例化(调用)一个PMOS开关

2. 举例: CMOS反相器

module invertor(out, in);

output out;

input in;

supply1 Vdd; // 定义电源

supply0 Gnd; // 定义地

pmos (out, Vdd, in);

nmos (out, Gnd, in);

endmodule

文章来源:http://www.cnblogs.com/adamite/archive/2008/11/28/1342969.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号