本文是对AMBA APB5协议的中文翻译。

AMBA APB5协议技术规范

第一章 引言

这一章介绍了APB协议的概述。主要包含了以下部分:

1.1关于APB协议

APB协议是一个低成本接口,优化了极低功耗并且减少了接口复杂度。APB接口不是流水线式的,它是一个简单的,同步的接口协议。每一次传输至少花费两个周期完成。

APB接口是针对外围设备的可编程控制寄存器设计的。APB外设通常通过APB桥连接到主存系统。例如,从AXI到APB可以用来连接许多APB外设到一个AXI内存系统。

APB传输通过一个APB桥启动。APB桥也可以称为一个请求者。一个外设接口对一个请求进行响应。APB外设也可以称为一个完成者。此技术规范将使用请求者和完成者。

第二章 信号描述

2.1 AMBA APB信号

这一部分描述了APB接口信号。

APB接口的一些信号有固定的宽度,一些是变化的宽度。当宽度是不固定时,使用一个属性来描述。如果属性的值是0,它意味着这个信号不在当前的这个接口。

Table2-1提供了一个APB协议接口信号的描述。

| 信号 | 来源 | 宽度 | 描述 |

| PCLK | clock | 1 | 时钟. PCLK是一个时钟信号。所有的APB信号是在PCLK的上升沿计时。 |

| PRESETn | System bus reset | 1 | 复位. PRESETn是一个复位信号,是active low.PRESETn通常是连接到系统总线的复位信号。 |

| PADDR | Requester | ADDR_WIDTH | 地址.PADDR是APB的地址信号。PADDR最大到达32bit。 |

| PPROT | Requester | 3 | 保护类型。PPROT表明事务的正常,优先或安全保护的等级,事务是否是一个数据访问或指令访问。参阅 Protection unit support on page 3-27 |

| PSELx | Requester | 1 | 选择。请求者为每一个完成者生成一个PSELx信号。PSELx表明完成者被选择并且一个数据传输被请求。 |

| PENABLE | Requester | 1 | 使能。PENABLE表明APB传输第二个或后续的周期。 |

| PWRITE | Requester | 1 | 方向。PWRITE为高表明APB写访问,为低表明APB读访问。 |

| PWDATA | Requester | DATA_WIDTH | 写数据。当PWRITE是高时,PWDATA写数据总线在写周期被APB桥请求者驱动。PWDATA是8bit,16bit和32bit 位宽。 |

| PSTRB | Requester | DATA_WIDTH/8 | 写选通。PSTRB表明在写传输时,那一个字节通道更新。写数据总线的每8bit有一个写选通。PSTRB[n]对应PWDATA[(8n + 7):(8n)]. PSTRB在读传输期间不能是active。 |

| PREADY | Completer | 1 | 准备。PREADY被完成者用来扩展一个APB传输。 |

| PRDATA | Completer | 1 | 读数据。当PWRITE为低,在读期间,PRDATA读数据总线被选中的完成者驱动。PRDATA可以是8bit,16bit和32bit。 |

| PSLVERR | Completer | 1 | 传输错误。PSLVERR是一个可选择的信号,被完成者置为高从而来表明一个APB传输错误的情形。参阅Error response on page 3-25 |

| PWAKEUP | Requester | 1 | 唤醒。PWAKEUP表明与APB接口的任何活动。参阅Wake-up signaling on page 3-28. |

| PAUSER | Requester | USER_REQ_WIDTH | 用户请求属性。PAUSER的最大宽度建议为128bit。参阅User signaling on page 3-29 |

| PWUSER | Requester | USER_DATA_WIDTH | 用户写数据属性。PWUSER的最大宽度建议为DATA_WIDTH/2。参阅User signaling on page 3-29 |

| PRUSER | Completer | USER_DATA_WIDTH | 用户读数据属性。PRUSER的最大宽度建议为DATA_WIDTH/2。参阅User signaling on page 3-29 |

| PBUSER | Completer | USER_RESP_WIDHT | 用户响应属性。PBUSER的最大宽度建议为16bit。 |

2.1.1 地址总线

一个APB接口有一个地址总线,PADDR,主要为读和写传输。PADDR表明字节地址。

关于数据宽度,PADDR允许非对齐,但是结果是不可预测的。例如,一个Completer可能使用非对齐地址,对齐地址或发出错误响应信号。

2.1.2 数据总线

APB协议有两个独立的数据总线,一个是读数据,一个是写数据。总线宽度是8bit,16bit或32bit。读和写的数据总线必须是相同的宽度。

数据传输不能同时发生,因为读数据和写数据总线没有它们自己独立的握手信号。

第三章 传输

这一章描述了典型AMBA APB传输,错误响应和保护单元支持功能。它包含以下部分:

写传输

写选通

读传输

错误响应

保护单元支持

唤醒信号

用户信号

3.1 写传输

这一部分描述了写传输的几种类型:

没有等待状态

有等待状态

在这一部分显示的所有信号都是在PCLK的上升沿采样。

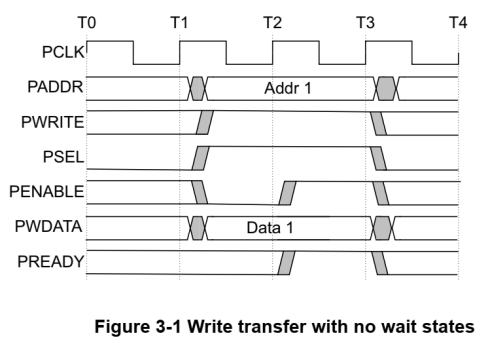

3.1.1 没有等待状态

图3-1显示没有等待状态的一个基本的写传输。

写传输的建立阶段发生在图3-1的T1。选择信号PSEL置高,这表明PADDR,PWRITE,PWDATA必须是有效的。

写传输的存取阶段在图3-1的T2,这时PENABLE置高。PREADY在PCLK的上升阶段被完成者置高从而用来表示写数据在T3被接收。PADDR,PWDATA和任何其他控制信号必须保持不变直到传输完成。

在传输的结尾,PENABLE置低。PSEL也置低,除非有另一次传输到相同的外设。

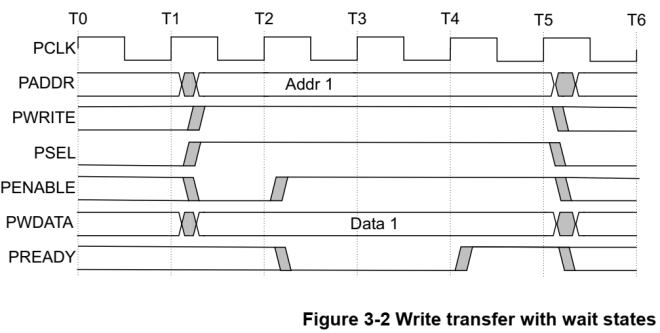

3.1.2有等待状态

图3-2显示了完成者如何使用PREADY来扩展传输。

在存取阶段,当PENABLE为高时,完成者通过驱动PREADY为低来扩展传输。以下信号在PREADY为低时保持不变:

地址信号,PADDR

方向信号,PWRITE

选择信号,PSELx

使能信号,PENABLE

写数据信号,PWDATA

写选通信号,PSTRB

保护类型信号,PPROT

用户请求属性,PAUSER

用户写数据属性,PWUSER

当PENABLE为低时,PREADY可以为任何值。这样就确保了有固定两个周期存取的外围设备可以使PREADY为高。

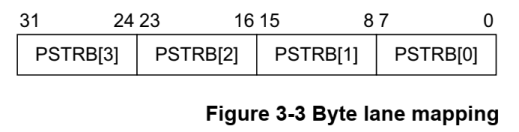

3.2 写选通

PSTRB确保了在写数据总线上的稀疏传输。每一位PSTRB对应写数据总线上的1byte。当置为高时,PSTRB表明写数据总线的字节通道的有效信息。

写数据总线的每8bit有一个写选通,因此PSTRB[n]对应PWDATA[(8n+7):(8n)]。

图3-3显示了在32bit数据总线上的关系:

对读传输,请求者必须驱动PSTRB所有位为低。

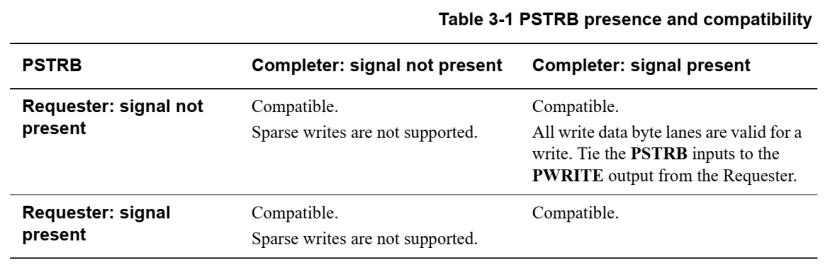

3.2.1 PSTRB的存在和兼容性

PSTRB是一个选择信号。一个APB外设可能支持一组有限的访问类型,这必须为程序员编制文档。这意味着,如果本文档声明不支持稀疏写数据,那么所有的PSTRB存在组合都可能是兼容的。

PSTRB在连接requester和Completers时的兼容性如表3-1所示。

3.3 读传输

在这一部分读传输有两种类型:

有等待状态

没有等待状态

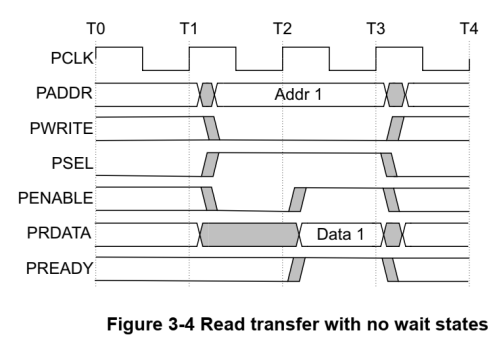

3.3.1 没有等待状态

图3-4显示了一个读传输。

地址PADDR,写PWRITE,选择PSEL,和使能PENABLE信号的时序是和图3-20描述的写传输一样。完成者必须在读传输完成前提供数据。

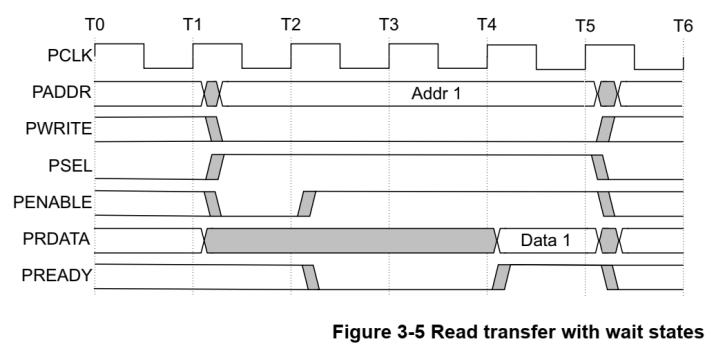

3.3.2 有等待状态

图3-5显示了PREADY信号如何扩展传输。

如果PREADY在存取阶段被驱动为低,那么次传输被扩展。以下信号当PREADY为低时保持不变:

地址信号,PADDR

方向信号,PWRITE

选择信号,PSEL

使能信号,PENABLE

保护信号,PPROT

用户信号,PAUSER

在3-23页的图3-5显示了使用PREADY增加了两个周期。但是,增加周期的任意数量可以从0开始往上。

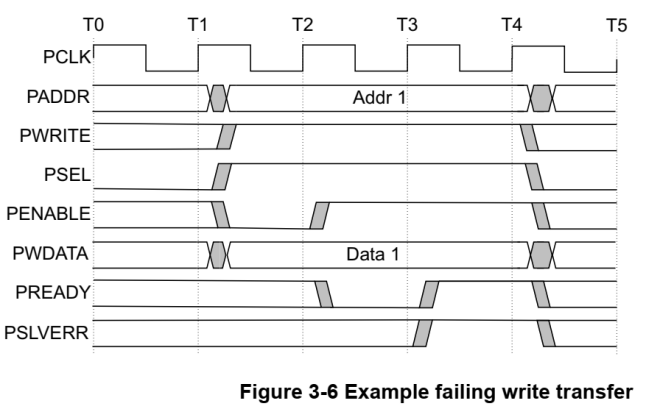

3.4 错误响应

PSLVERR可以被用来表明在一次APB传输中的一个错误的状况。错误可能发生在读和写事务中。当PSEL,PENABLE和PREADY为高时,PSLVERR在APB传输的最后一个周期仅仅被当做有效。

建议PSEL,PENABLE和PREADY为低时,PSLVERR驱动为低,但是不是强制要求。

接收到错误的事务可能改变或不改变外设的状态。这是特定于外围设备的,任何一种状态都可以接受。

当一个写事务接收一个错误,这不说明外设内部的寄存器没有更新。

接收到一个错误的读事务可能返回一个无效的数据。外设不需要在读取一个错误时驱动数据为全0。接收到一个错误响应的读传输的请求者可能仍然使用这个数据。完成者不能依赖一个错误响应来阻止PRDATA的读取。

完成者不要求支持PSLVERR。当一个完成者不支持PSLVERR时,请求者适当的输入是低。

3.4.1 写传输

图3-6显示了一个失败的具有一个错误写传输的例子。

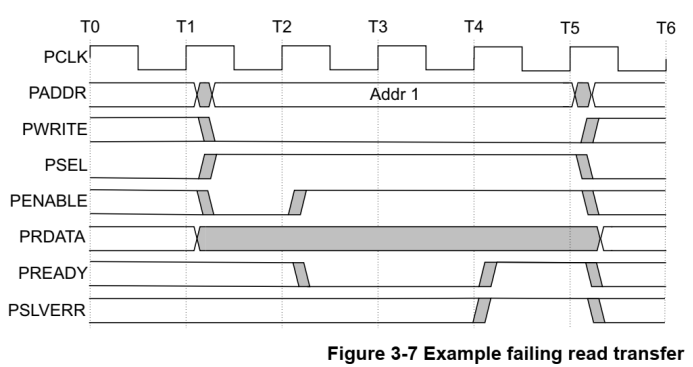

3.4.2 读传输

读传输也可以完成具有一个错误响应,从而表明没有可以使用的有效读数据。

3.4.3 PSLVERR的映射

当桥接时:

从AXI到APB:PSLVERR上的APB错误被映射回RRESP(读)和BRESP(写)

从AHB到APB:PSLVERR上的APB错误被映射回HRESP进行读写

3.5 保护单元支持

为了支持复杂的系统设计,通常需要为系统中的互联和其他的设备对事务提供保护。对APB接口,这个保护是由PPROT[2:0]信号提供。图3-2显示了具有保护等级编码的三个读取保护等级。

PPROT Protection Description Comments

PPROT[0] 正常或优先 PPROT[0]被requester使用来表示处理模式。一个优先的处理模式在一个系统中通常有更高的访问等级。 低表示正常模式访问。高表示优先模式访问。

PPROT[1] 安全或非安全 PPROT[1]在系统中用于更高等级的处理模式的区分。 低表示安全模式访问。高表示非安全模式访问。

PPROT[2] 数据或指令 PPROT[2]提供了一个事务是数据或指令的提示。事务提示是作为一个提示提供的,不是在所有情况下都是准确的。 低表示数据访问。高表示指令访问。

注意:

PPROT的主要用途是作为安全或不安全事务的标识符。使用PPROT[0]和PPROT[2]标识符的不同解释是可以接受的。

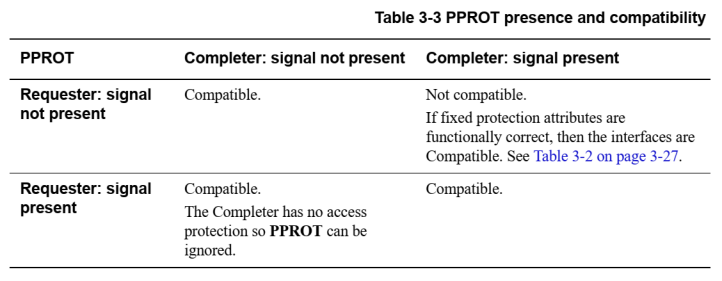

3.5.1 支持存在和兼容性

PPROT是Requester和Completer接口上的一个可选信号。

图3-3描述了当连接一个Completer和Requester时,PPROT的兼容性。

3.6 唤醒信号

这部分描述了APB接口的唤醒信号。

3.6.1 介绍

唤醒信号,PWAKEUP,用来表明APB接口上的任何活动。PWAKEUP提供了一个无故障信号,可以路由到时钟控制器或类似元件,从而使能电源和时钟到连接的元件。

唤醒信号属性用来表明是否一个元件支持唤醒信号:

TRUE 出现唤醒信号

FALSE 不出现唤醒信号。如果唤醒信号的属性没有声明,就认为是FALSE。

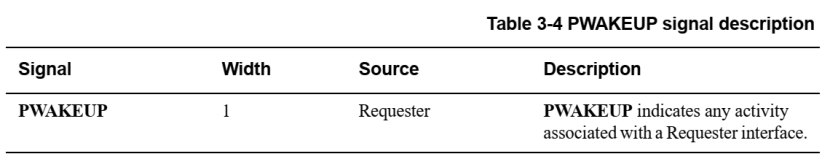

3.6.2 PWAKEUP信号

表3-4描述了PWAKEUP信号。

PWAKEUP信号的规则和建议是:

PWAKEUP是和PCLK同步的,必须适用在不同的时钟域中异步采样。这要求PWAKEUP是无干扰的glitch-free。例如,这可以直接通过寄存器或无干扰OR树生成来实现。

PWAKEUP允许在PSELx的前面,中间或以后生效。

在PREDAY生效之前,Completer被允许等待PWAKEUP生效。如果PWAKEUP出现但是从没有置起,接口可能死锁。

如果PWAKEUP和PSELx在相同周期中都是HIGH,则在PREADY生效之前,PWAKEUP必须保持有效。

建议在PSELx生效之前,PWAKEUP生效至少一个周期,以防止延迟接受新事务。

建议在没有进一步传输要求时,PWAKEUP设置为无效。

允许,但不建议,在没有传输发生时,PWAKEUP生效后失效。

建议连接的请求端和完成端同时设置时钟门控。

如果一个Completer接口时钟独立于Requester时钟进行门控,并且使用PWAKEUP来启用Completer时钟,则有可能Completer错过传输的Setup阶段。建议连接的请求端和完成端同时设置时钟门控。

3.7 接口时钟

这一部分描述了APB接口的用户信号。

3.7.1 介绍

APB协议的用户可能会遇到需要添加APB协议中未指定信号的应用。用户信号定义了添加这个信号到事务的标准方法,不用定义信号的使用。

一般情况下,不建议使用用户信号。APB协议接口没有定义这些信号的功能,如果两个元件以一种不兼容的方式使用相同的用户信号,讲导致互操作性的问题。

用户信号只能添加到APB5接口协议中。

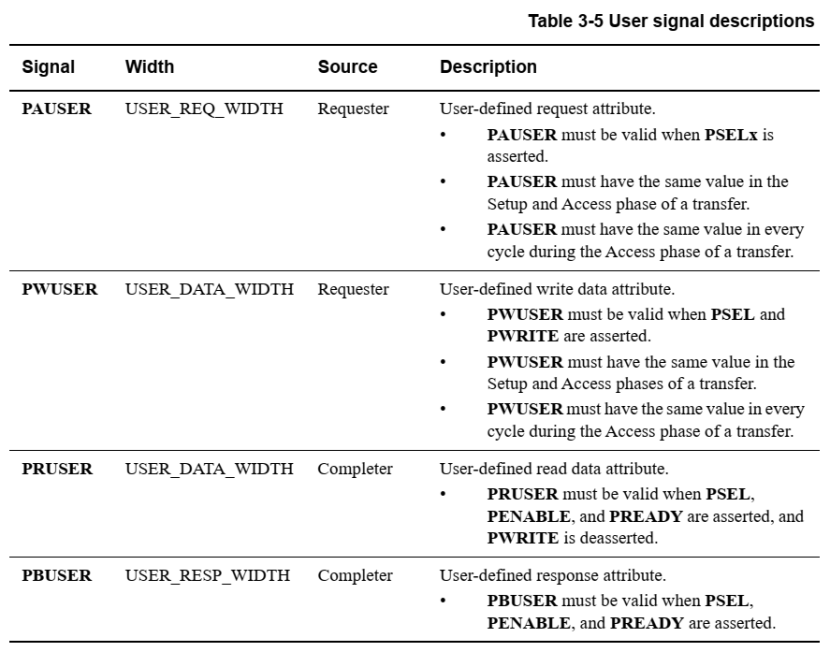

3.7.2 信号

所有的信号是可选的。如果相关的宽度属性是0,这个信号是不出现。

表3-5提供了用户信号的描述。

3.7.3 用户信号的建议

在用户信号实现的地方,本规范不支持所有用户信号。用户信号的宽度是实现定义,对请求,数据和响应可能是不同的。

建议在跨桥或互联的域上,包含所有用户信号的规定。但是,在completer没有要求包含这些信号。

建议USER_DATA_WIDTH为数据总线宽度的整数倍(以字节为单位),以帮助进行数据宽度和协议转换。

第四章 操作状态

这一章描述了AMBA APB协议的操作状态。它包含以下部分

操作状态在4-32

4.1 操作状态

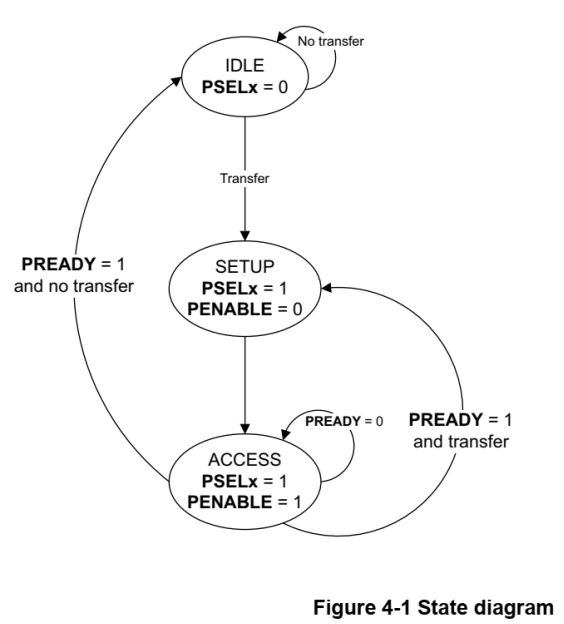

图4-1显示了APB接口的操作状态。

状态机通过以下状态运行:

IDLE 这是APB接口的默认状态

SETUP 当一个传输请求时,这个接口移动到SETUP状态,这里适当的选择信号PSELx是断言。接口只保持SETUP状态一个周期,在下一个时钟的上升沿一直会转到ACCESS状态。

ACCESS 使能信号,PENABLE,在ACCESS状态被断言。以下信号在SETUP转换到ACCESS状态期间或在ACCESS状态期间保持不变:PADDR

PPROT

PWRITE

PWDATA,只为写传输

PSTRB

PAUSER

PWUSER

从ACCESS状态退出受来自completer的PREADY信号控制:

如果PREADY被completer保持为低,然后接口保持ACCESS状态

如果PREADY被completer保持为高,然后接口退出ACCESS状态,如果没有更多的传输请求,总线返回到ILDE状态。如果接下来是另一个传输,总线进入到SETUP状态。

第五章 接口校验保护

本章描述了一种检测组件间接口单比特错误的奇偶校验方案。它包括以下部分:

使用校验的保护

接口保护的配置

校验检查

错误侦测行为

校验检查信号

5.1 使用校验的保护

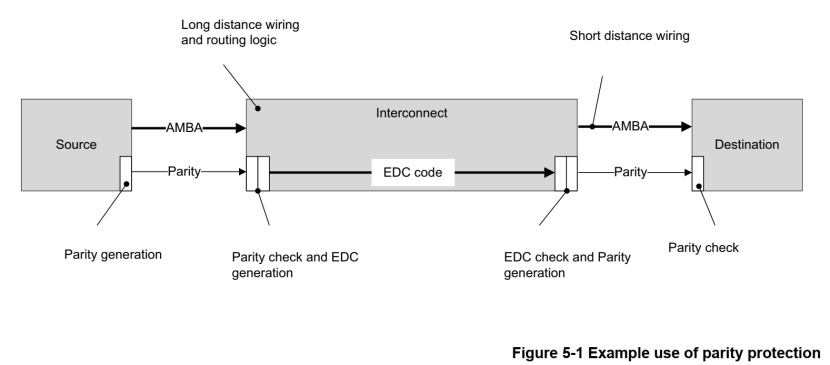

对于安全关键的应用,检测和纠正SoC内单个导线上的瞬态和功能错误是必要的。

在一个系统元件中,一个错误在连接的组件间可能传播和引起大量的错误。错误侦测和纠正需要端到端操作,覆盖所有原到目的的所有逻辑和线。

实现端到端保护的一种方式是在组件中利用定制的EDC(Error Detection and Correction)方案,并在组件中实现简单的错误侦测方案。在这些组件之间,没有逻辑,而且单比特错误不会传播到多比特错误。这一部分描述了一个在组件间的接口上检测单比特错误的校验方案。如果发生在不同的校验信号组,多比特可以被侦测到。

图5-1显示了可能使用校验的位置。

5.2 接口保护的配置

接口的EDC方案是由Check_Type属性定义。以下是Check_Type的值定义:

FALSE 接口上没有校验信号

Odd_Parity_Byte_ALL 所有信号都包括奇校验。奇校验的每个bit可以覆盖8bit。

如果Check_Type没有声明,认为FALSE。

只有APB5有校验信号。

5.3校验检查

字节奇偶校验接口保护添加的检查信号有以下共同的属性:

使用奇校验。奇校验意味着在接口信号和检查信号总有奇数个bit断言。检查信号与每一个接口信号有关。

每一个奇校验位覆盖不超过8bit的有效载荷。这个限制假设在生成每个奇偶校验位的时间允许中最多有三个逻辑级别可用。

覆盖关键控制信号的校验信号用一个奇偶校验为定义。单一的奇校验bit位是原始关键控制信号的翻转。关键控制信号可能有一个最小的可以利用的时间余量。

对于一个大于1bit的检查信号:

----在有效载荷中,检查信号bit[n]对应[(8n+7):8n]

----如果有效载荷不是一个整数的字节数,检测信号的最高位覆盖的位数少于有效载荷最高位的8bit。

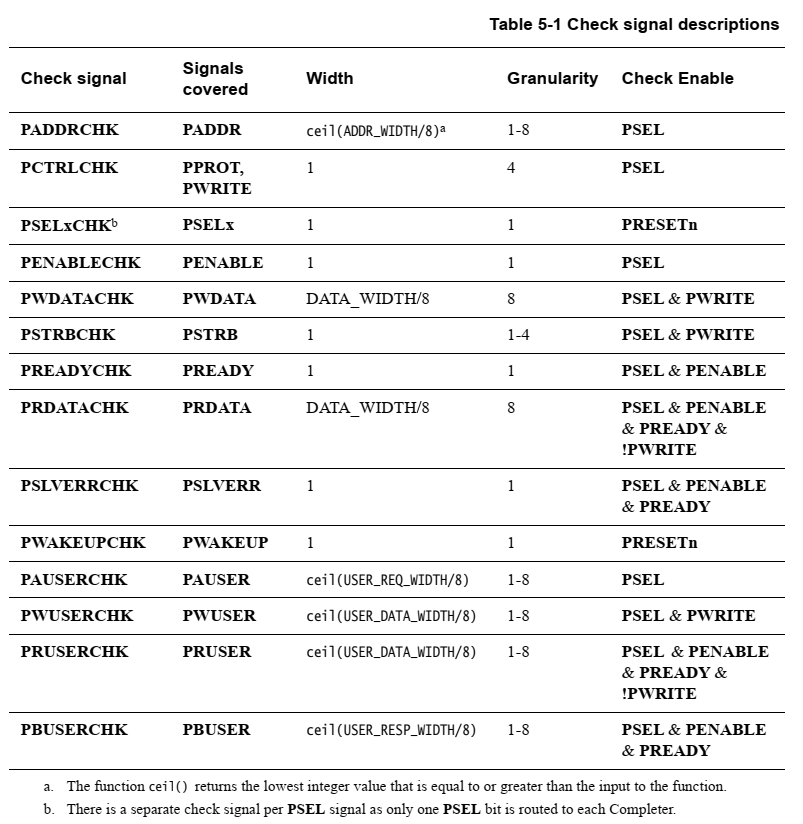

检查信号必须在检查使能项为True的每个周期中被正确驱动。参阅Table 5-1 on page 5-38.

校验信号必须适当的驱动有效载荷中所有相关的位,不论这些位在传输中被有效的使用。例如,PWDATACHK的所有位必须被正确的驱动,即使一些字节是无效的数字字节。

如果检查信号所覆盖的一些信号在接口上不存在,那么缺失的信号被假定为LOW。

如果检查信号所覆盖的信号都没有出现在接口上,则检查信号从接口中被省略。

5.4 错误检测的行为

当检测到校验错误时,关于元件或系统的行为这个技术规范不是规范性的。依赖于系统和受影响的信号,一个翻转为有广泛的影响。它可能无害,会导致性能问题、数据损坏、安全违规或死锁。

当检测到错误时,Completer可能:

中断或传播传输

纠正校验检查信号或传播错误

更新内存或保持不动

通过其他方式发出错误响应,例如一个中断

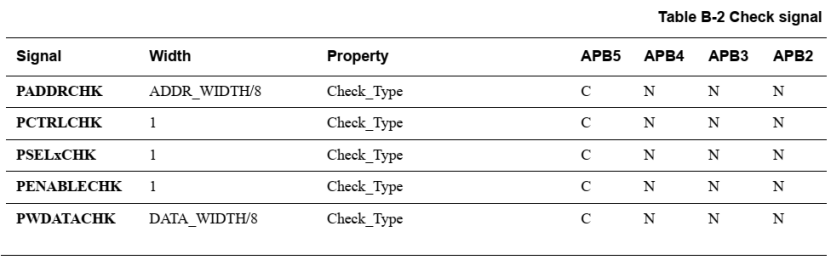

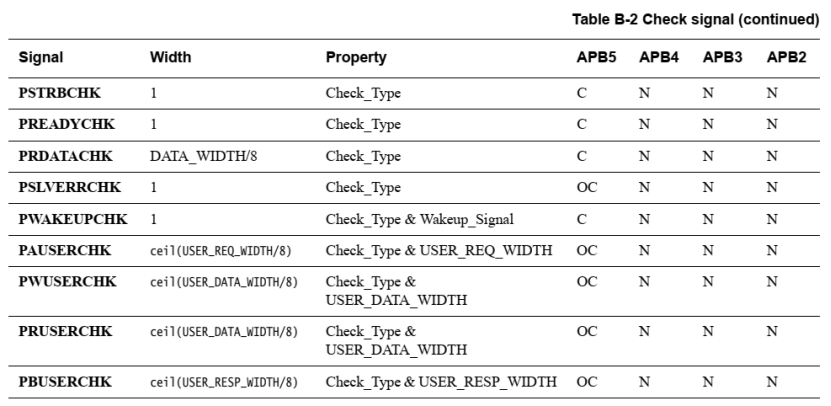

5.5 校验检查信号

检查信号与PCLK是同步的,必须在检查使能项为True的每个周期中正确驱动。

表5-1显示了校验检查信号。

A.函数ceil()返回一个等于或大于输入的最小的整数值。

B.每个PSEL信号有一个单独的检查信号,因为只有一个PSEL位路由到每个Completer。

附录A 信号验证

本附录总结了描述信号何时必须有效的规则.

A.1 验证规则

以下信号必须一直有效:

PSEL

PWAKEUP

当PSEL置起时,以下信号必须有效

PADDR

PPROT

PENABLE

PWRITE

PAUSER

PSTRB

PWDATA,只为有效写数据通道

PWUSER,只为写

当PSEL和PENABLE置起时,以下信号必须是有效的:

PRDATA,只为读

PSLVERR

PRUSER,只为读

PBUSER

建议将不需要有效的信号驱动到零。

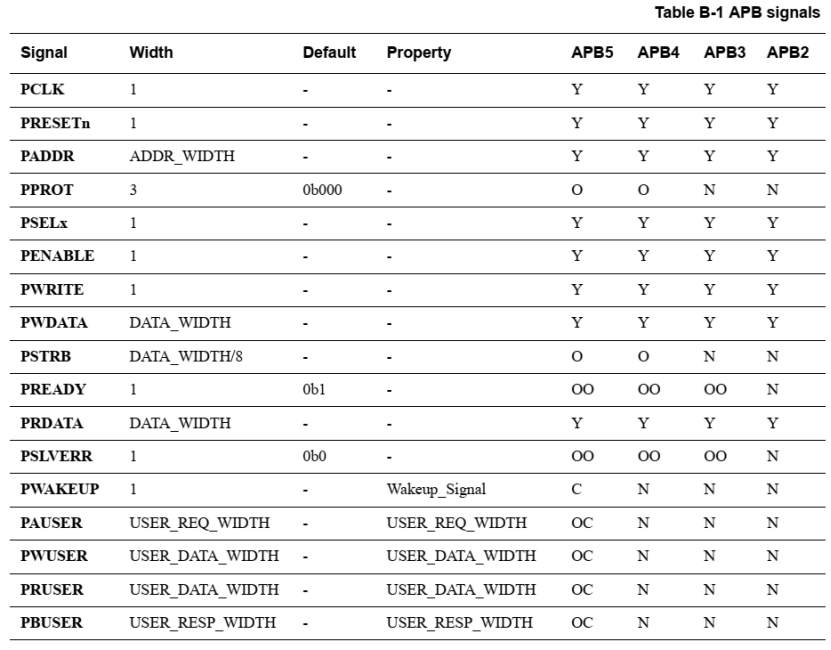

附录B 信号清单

此附录提供了APB上所有信号的总结

B.1 APB信号

表B-1描述了APB信号清单。表B-2描述了APB检查信号的清单。可选信号有一个默认值,应该用于任何非驱动输入。

表B-1及表B-2所使用规则如下:

Y 强制

N 必须不能呈现

O 对输入和输出可选

OO 对输出端口可选,对输入端口强制

C 有条件的,如果属性为真,必须呈现

OC 可选条件,可选,但只能在属性为True时出现

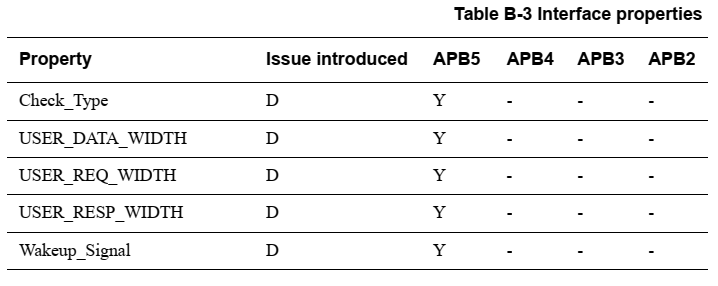

接口属性如表B-3所示。

如果一个表项不是Y,该属性必须为False或该接口类型未声明。