计算机系统结构大题精讲5-页面替换算法-Cache 和加速比

1、一个由Cache存储器与主存储器组成的二级存储系统,已知主存容量为1M字,Cache容量为32K字。采用组相连地址映像与变换,缓存共分8组,主存与缓存块的大小均为64字。

1)画出主存与缓存的地址格式,说明各字段名称与位数

主存

总容量:log2,1024*1024=20

区号:主存容量/Cache容量=1024*1024/32*1024=32

log2,32的对数等于5

组号:log2,8的对数,等于3

组内块号:5

块内地址:log2,64的对数,等于6

Cache总容量:loh2,32*1024=15

所有组内块号=15-6-3=6位

| 区号 | 组号 | 组内块号 | 块内地址 |

| 5位 | 3位 | 6位 | 6位 |

| 组号 | 组内块号 | 块内地址 |

| 3位 | 6位 | 6位 |

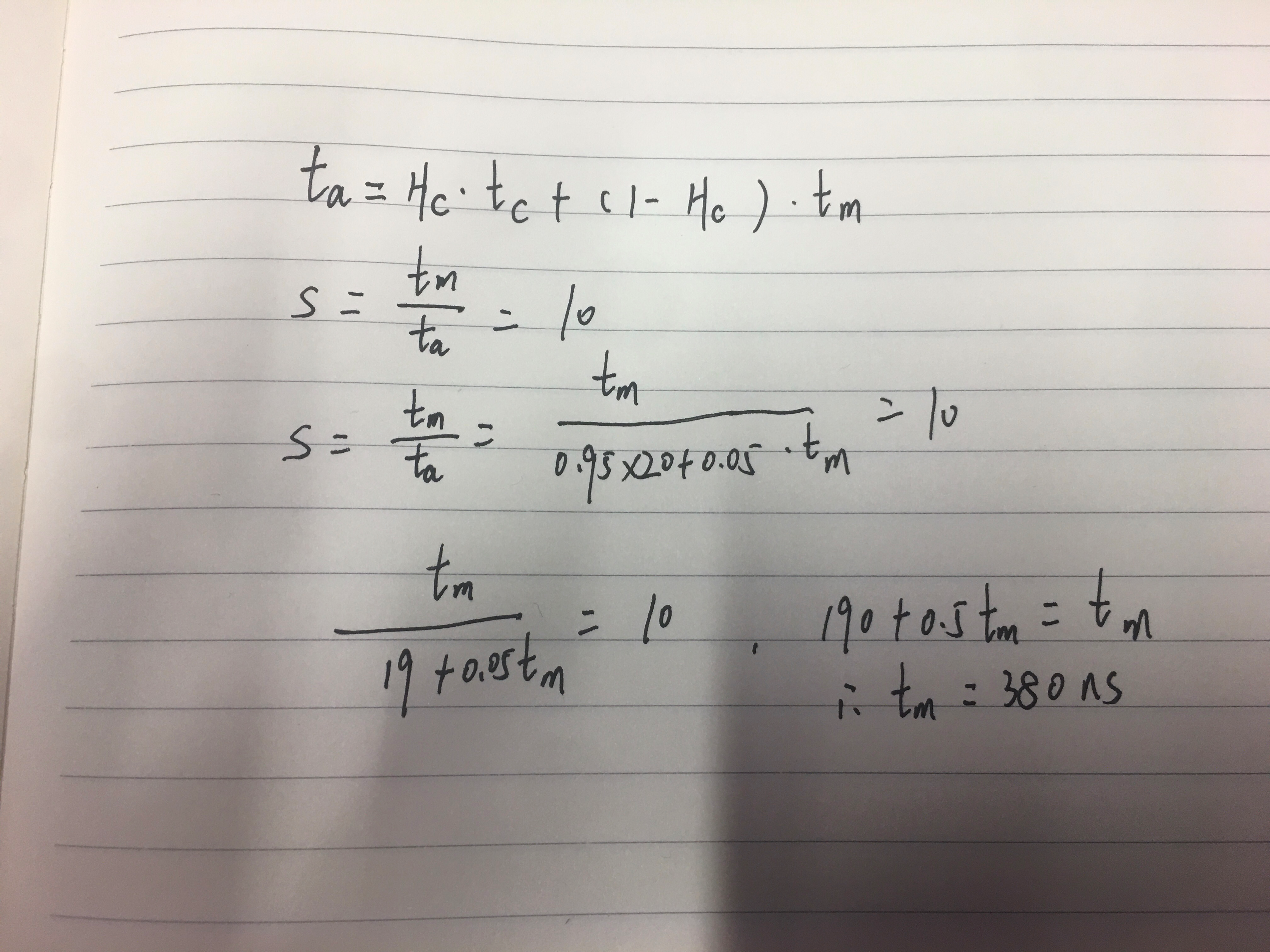

2)假设缓存存取周期为20ns,命中率为0.95,采用缓存后的加速比要达到10,计算主存的存取周期

ta(缓存等效存取周期)=Hc(缓存命中率)*Tc(缓存存取周期)+(1-Hc)*Tm(主存存取周期)

本文来自博客园,作者:{Tester十点半},转载请注明原文链接:https://www.cnblogs.com/jialeliu/p/16731392.html

浙公网安备 33010602011771号

浙公网安备 33010602011771号