双端口RAM和多模块存储器

双端口RAM

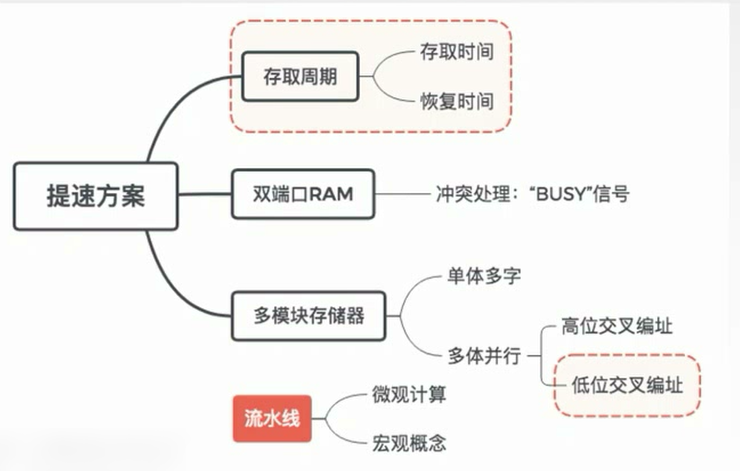

提高存储器访存速度一些措施。

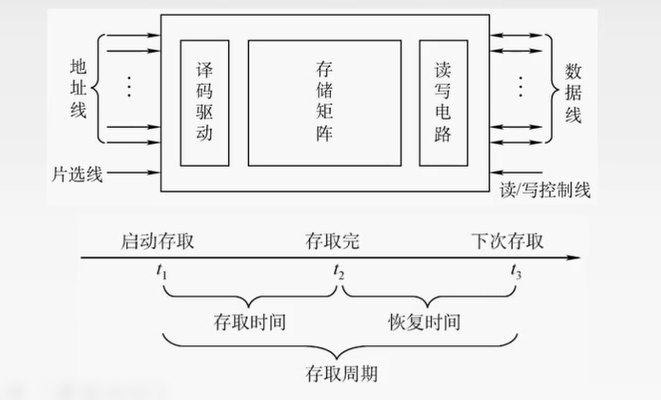

存取周期

进行一次存取之后,是不能立即进入下一次存取的,存储器要进行一次恢复。

存取周期=存取时间+恢复时间

- 对不同时间进行不同存取操作,双端RAM

- 流水线的方式,多模块存储器

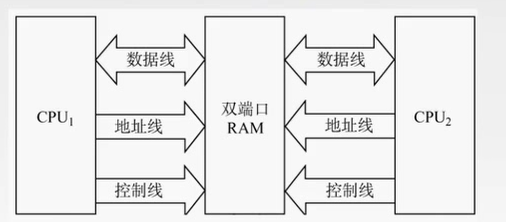

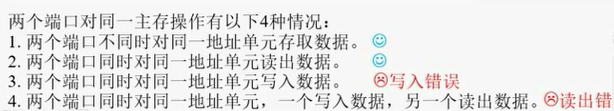

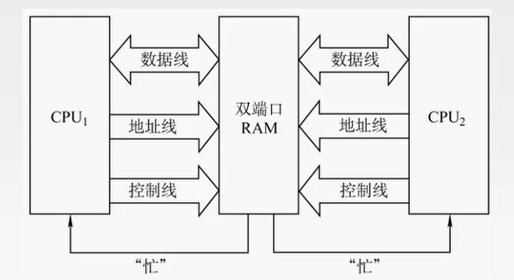

双端口RAM

置一个忙信号。

多模块存储器

CPU的速度比存储器要快的,如果从存储器中同时存取n个字。可以提高cpu使用资源

补充:可以并行工作,如总线宽度为mW时,可以同时取出长度为mW的数据。

普通存储器

每行为1个存储单元

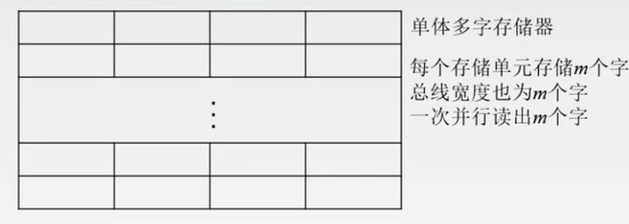

单体多字存储器

每个存储单元存储m个字,总线宽度也为m个字,一行并行读出m个字。

增加了存储器的带宽。

缺点:指令和数据在主存内必须连续存放。

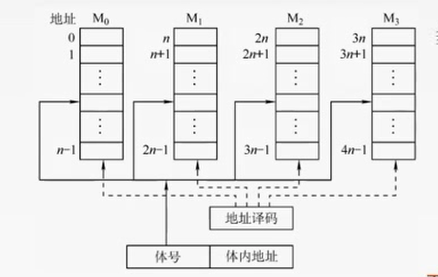

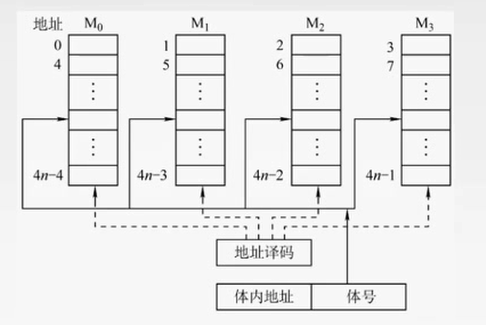

多体并行的存储器

每个模块都有相同的容量和存取速度,各个模块都有独立的读写控制电路、地址寄存器和数据寄存器

编制方式:

高位交叉编址的多体存储器

高位是体号,低位是体内地址

假如有8个存储单元

相当于说,先确定是哪一个(存储体),然后在在那一个里面找相对应的一块。

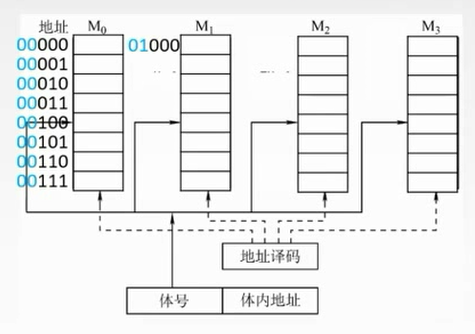

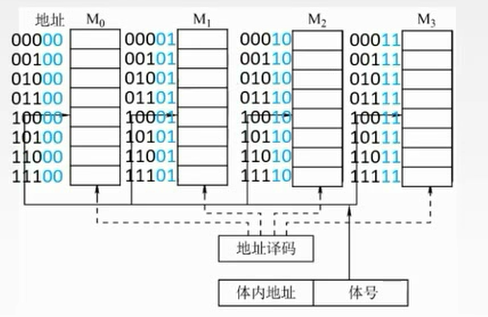

低位交叉编址的多提存储器

低位是体号,高位是体内地址

假如有8个存储单元

先找到具体的位置,在看哪一个存储体。

为什么要这么弄?

假如每个存储体的存储周期为T

连续访问:

00000

00001

00010

00011

00100

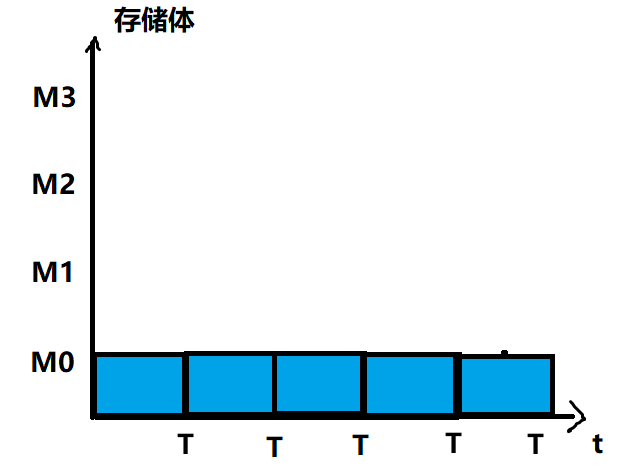

高位

其实就是在M0里一直访问

时空图:

如果连续访问这个5个地址,需要花费5t个时间。并没有带来什么好处。

高位交叉编址相当于扩容,每个其实还是相当于独立的,并没有带来时间优势。

采用高位交叉编址,连续取n个存储字,耗时nT

低位

先访问M0的0号单元,接下来00001,是M1的0号单元,只需要间隔一小段时间。然后就是M2,M3.都是用一小段时间。可以相当于是同时访问。大大减少了存取时间。

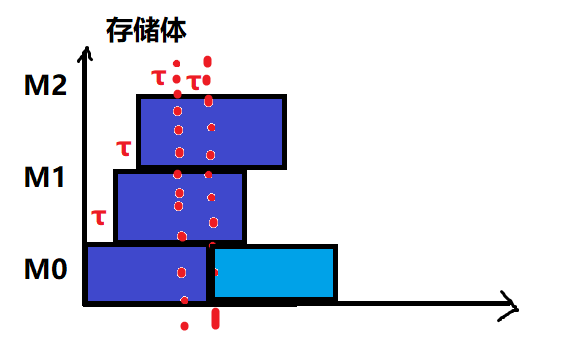

时空图:

时间如何计算?

假设启动完M0后启动M1的时间间隔是τ,启动完M1在启动M2的时间间隔是τ、启动完M2在启动M3的时间间隔是τ,接下来启动完M3在启动M0的时间间隔也是τ

所以就有总时间T+4τ

假如连续存取n个存储字,采用低位交叉编址,耗时:T+(n-1)τ

流水线(考试常考)

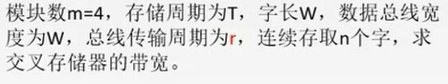

微观(计算题)

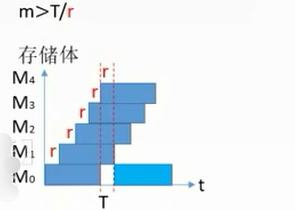

有m个存储体,存储周期是T,字长W,每隔r时间启动下一个存储体,连续存放n个字,求存储器的存取速率。

如果m<T/r

还需要在等多一个r

如果m>T/r

所以:

如果n较大时,带宽->W/r

对比单个存储体的带宽:W/T

宏观(概念题)

一个存储周期内,交叉存储器可以提供的数据量为单个模块的m倍。

回顾

提出这样的存储器是为了提高CPU的访存速度

本文作者:Jev_0987

本文链接:https://www.cnblogs.com/jev-0987/p/13561073.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步