半导体存储器

半导体存储器

半导体存储芯片的基本结构

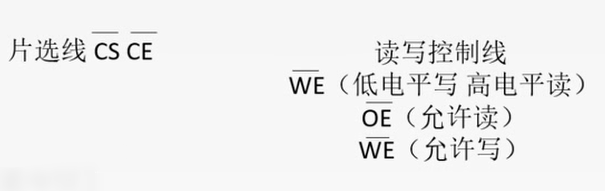

片选线:确定哪一个存储芯片被选中

上面有一杠:低电平有效

- 存储矩阵:由大量相同的位存储单元阵列构成。

- 译码驱动:将来自地址总线的地址信号翻译成对应存储单元的选通信号,该信号在读写电路的配合下完成对被选中单元的读/写操作。

- 读写电路:包括读出放大器和写入电路,用来完成读/写操作。

- 读/写控制线:决定芯片进行读/写操作。

- 片选线:确定哪个存储芯片被选中,可用于容量扩充。

- 地址线:是单向输入的,其位数与存储字的个数有关。

- 数据线:是双向的,其位数与读出或写入的数据位数有关。

SRAM(静态RAM)

static random access memory

DRAM:dynamic random access memory

随机存储存储器

半导体材料,构成不同的电路

一旦断电立马丢失信息。

DRAM(动态RAM)的刷新(重要)

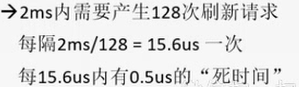

- 多久刷新一次?刷新周期:一般是2ms

- 每次刷新多少存储单元?以行为单位,每次刷新一行的存储单元——为什么要用行列地址?

以前的那个太多条线了

拆分为行列地址(DRAM行、列地址等长)

存储单元排列成2^{n/2} * 2^{n/2} 的矩阵

减少了选通线的数量。

- 如何刷新?有硬件支持,读出一行的信息后重新写入,占用1个读/写周期

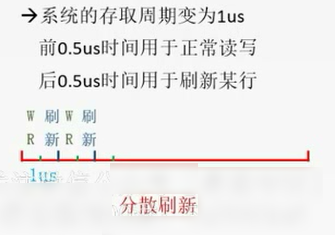

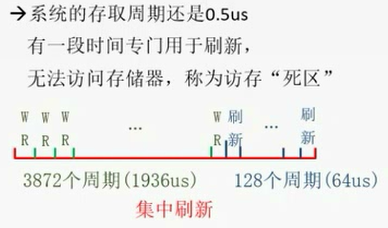

- 在什么时候刷新?假如DRAM内部结构排列成128*128的形式,读/写周期(存取周期)0.5us ,2ms共2ms/0.5us=4000个周期

思路一:每次读完都刷新一行(分散刷新)

思路二:2ms内集中安排时间全部刷新(集中刷新)

思路三:2ms内每行刷新1次即可(异步刷新)

RAM的读写周期(稍作了解)

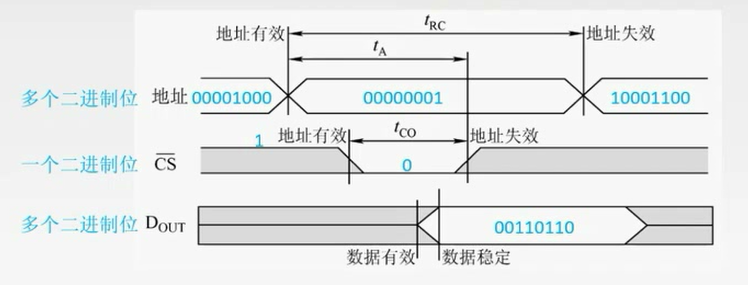

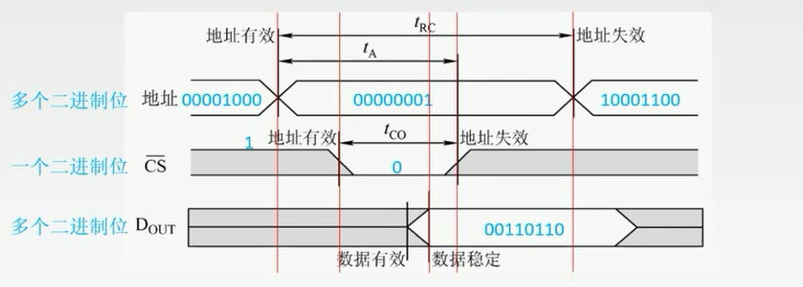

静态SRAM读周期

首先给一个地址信号,地址产生效果,地址线有快有慢,需要等待稳定。

经过一段时间后片选线才能有效。找到读的是哪一个存储元的信息。

等多一段时间,进行数据的读操作,

数据线上稳定了有信号,开始读。数据线稳定输出,

完全读出,片选线才失效(保持到数据稳定输出)。

等多一段时间,地址信号才撤回,下一个地址。

如果读写控制线为1根,则整个读过程中WE(一杠)为高电平

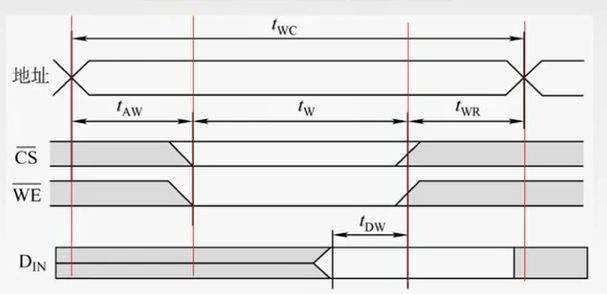

SRAM的写周期

首先给一个地址,等待地址稳定后

ROM(只读存储器)

随机存取

易失性,一断电丢失

RAM:易失性存储器

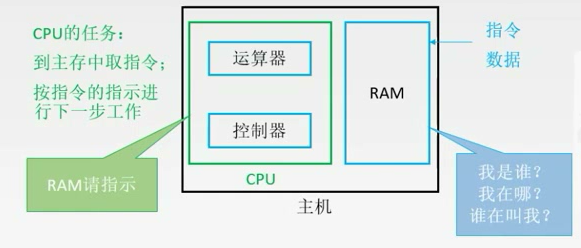

CPU任务:到主存中取指令;按指令的指示进行下一步工作

ROM断电之后也不会丢失。

先把辅存里的OS调到ROM

为什么不全用ROM?因为有时候还是要写的

非易失性:ROM

ROM:Read-Only Memory

本文作者:Jev_0987

本文链接:https://www.cnblogs.com/jev-0987/p/13561065.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步