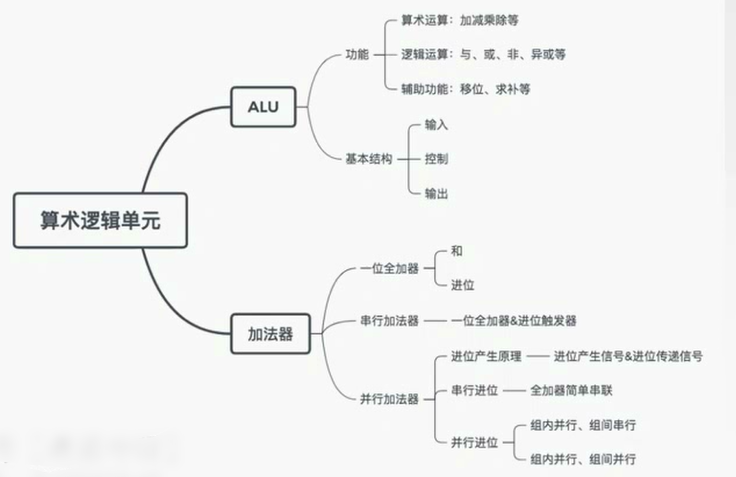

算术逻辑单元

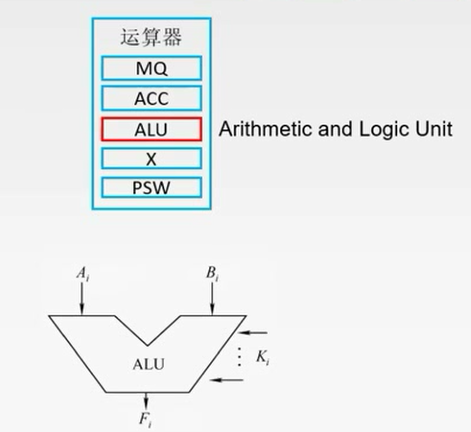

运算器、算术逻辑单元、累加器、状态寄存器、通用寄存器

ALU

算术逻辑单元

运算器当中最重要的部分就是算术逻辑单元

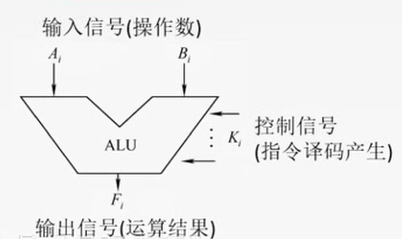

算术运算:加减乘除

逻辑运算:与或非异或

辅助功能:移位、求补

接受一个输入信号,在接收一个控制信号,根据控制信号所给的控制信息对输入信号进行操作,产生输出信号。

数字电路基础知识补充

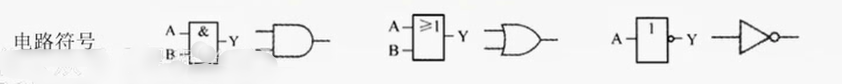

逻辑符号

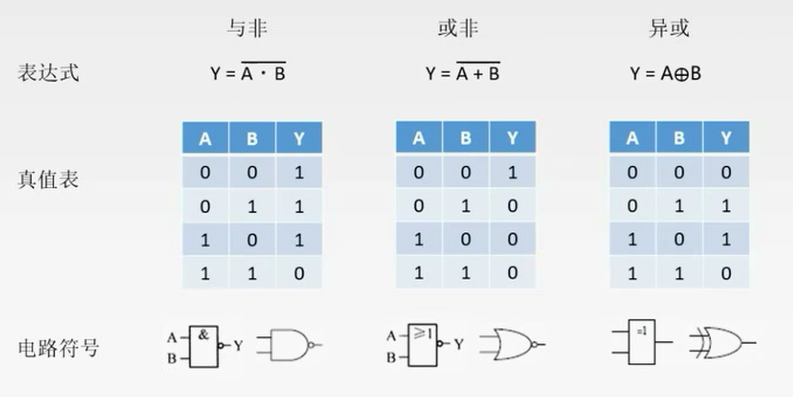

与或非

与门的天然逻辑:“屏蔽”(当a是0的时候,不论b是什么都输出0)

复合逻辑

半导体电路实现起来方便。

与门的天然逻辑“屏蔽”

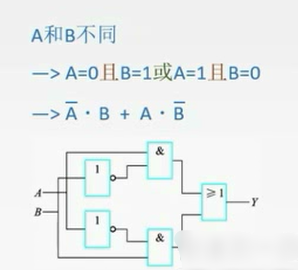

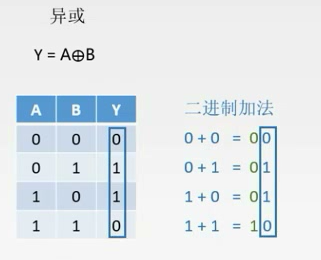

异或的天然逻辑“加法”“奇偶“

同或(了解即可)

加法器

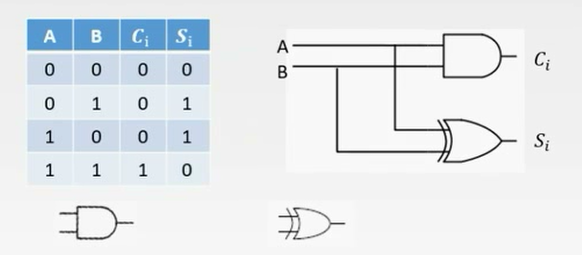

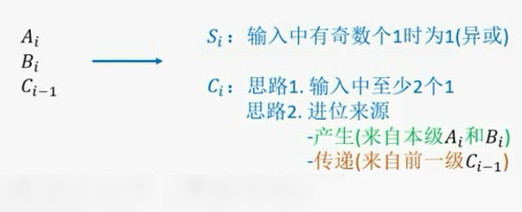

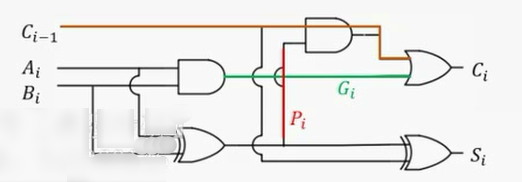

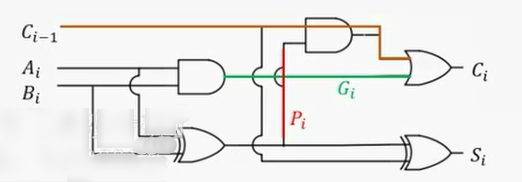

组合逻辑电路设计-一位全加器

与+异或(半加器)

还需要一个进位器

串行加法器

只有一个全加器,数据逐位串行输入到加法器中进行计算

如果操作数长n位,加法就要分n次进行,每次产生一位和,并且串行逐位地送回寄存器。

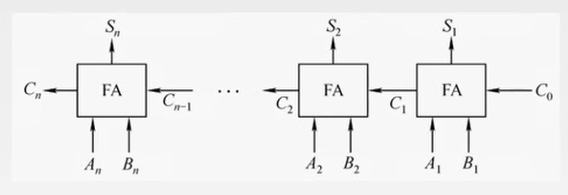

并行加法器

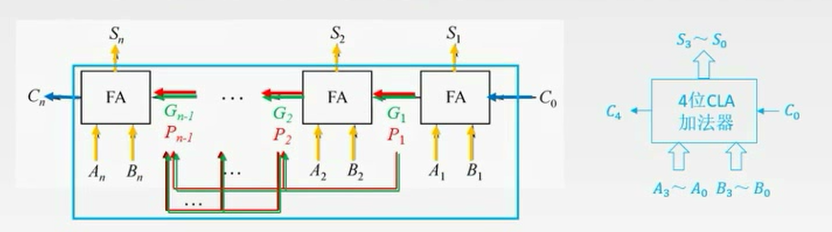

串行进位的并行加法器:把n个全加器串接起来,就可进行两位数的相加。

串行进位又称为行波进位,每一级进位直接依赖于前一级的进位,即进位信号是逐级形成的。

这样进位是比较麻烦的,要从下一级获得进位,需要等待

改进

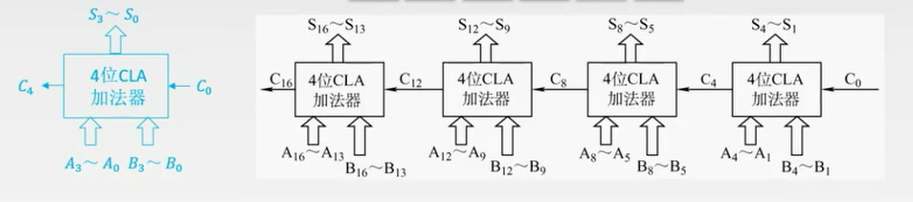

并进进位的并行加法器:各级进位信号同时形成,又称为先行进位、同时进位。

单极先行进位方式,又称为组内并行、组间串行进位方式。

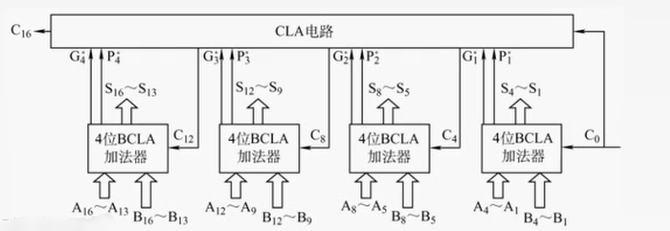

多级先行进位方式,又称为组内并行、组间并行进位方式

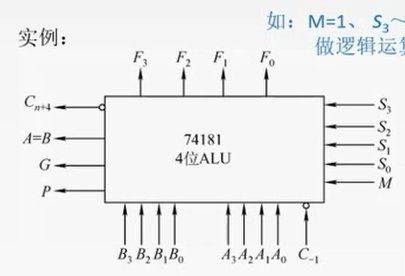

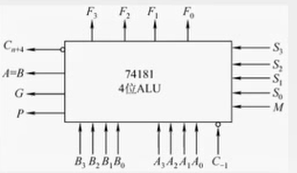

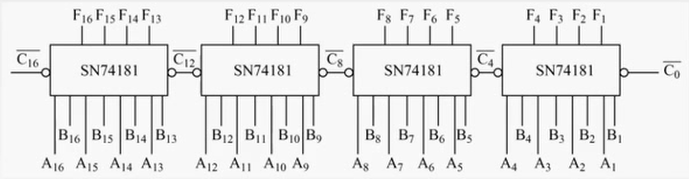

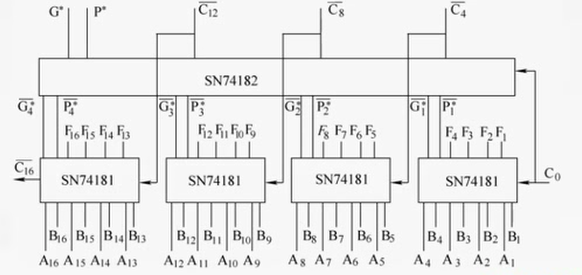

ALU芯片的组织

串行

并行

知识回顾

本文作者:Jev_0987

本文链接:https://www.cnblogs.com/jev-0987/p/13432401.html

版权声明:本作品采用知识共享署名-非商业性使用-禁止演绎 2.5 中国大陆许可协议进行许可。

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步