STM32H563核心板调试笔记(一)

前言

这是组里师兄负责的项目,以FPGA为数据采集核心,但还需要执行一些流程性的指令,因此还需要一个CPU。我们不用Zynq是因为它里面的CPU性能比较强,功耗比较高(其实我们没有人很懂Zynq,可以说这是我们选型的假设,现在选都选好了,你就承认吧)。而MCU部分组里也就我比较懂,于是我经过一番比较后,选择了STM32H5系列作为该项目逻辑上的核心控制器。

我们主要关心的是性能和接口,尤其是MCU与FPGA之间通信的接口。经过比较,我发现Octo-SPI可能比FSMC有更高的带宽,因为后者的外设缺少packing功能,从而每次传输只能传输至多16位数据,而传输频率大约可以达到CPU频率除以3到5(其实我不懂AMBA,凭经验估计的)。Octo-SPI的外设具有packing功能,即DMA传过来32位数据以后它可以分4次发8位出去,反之亦然,而它的对外传输速率可以达到CPU主频250 MHz,这是通过125 MHz时钟加上DDR实现的(他们称为DTR)。

再往上,8位可以扩展到16位,但这种名叫XSPI的外设只有少数高端型号的最大封装才有(具体而言,STM32H7R3L8H6H),BGA的,暂时不想碰。话说回来,我也有点担心H563的性能能否满足项目要求。哦对了,在H563的各种封装中我选择了144-pin封装的,因为144-pin才开始支持SDRAM,并且恰好ZIT6最便宜,30元一片。刚好我发现H723Z跟H563Z的pinout基本兼容,只有6个不兼容的引脚,我都分别做了基于0欧电阻的兼容性设计。

在PCB设计方面,我尽量把元器件都放在了顶层,但受限于面积还是有一部分放在了底层。我专门挑选一些本来就不打算让嘉立创SMT的元器件放在反面,包括DC/DC的电感、调试器的F103和各种运放(连选型都没想好呢),这样我就只用做单面SMT,选择经济型给导师省点钱,还可以用上一些优选合作料,省钱又省心。

144-pin的布线难度比我想象中高很多,以至于这一块板的设计花了我一周不止(全职):10月17号立项,25号投产。4层还画不下,刚好体验一下6层板和盘中孔工艺。只可惜第一次做六层板,嘉立创就让我非常失望,因为原定交期29号,可实际上11月3号才发货。不知是什么原因,可能是PCB良率不高,第一批板子能上SMT的不足5片,于是只能再等一个盘中孔6层板的生产周期,才凑够了足够的PCB去做SMT。

SMT客服给的图,可是左上角才是我的板,有问题的板不是我的啊(经济型SMT只能拼版生产,这下一分价钱一分货了)

一波三折过后,终于在今天(11月5日)下午收到了我的第一块6层板。

全貌

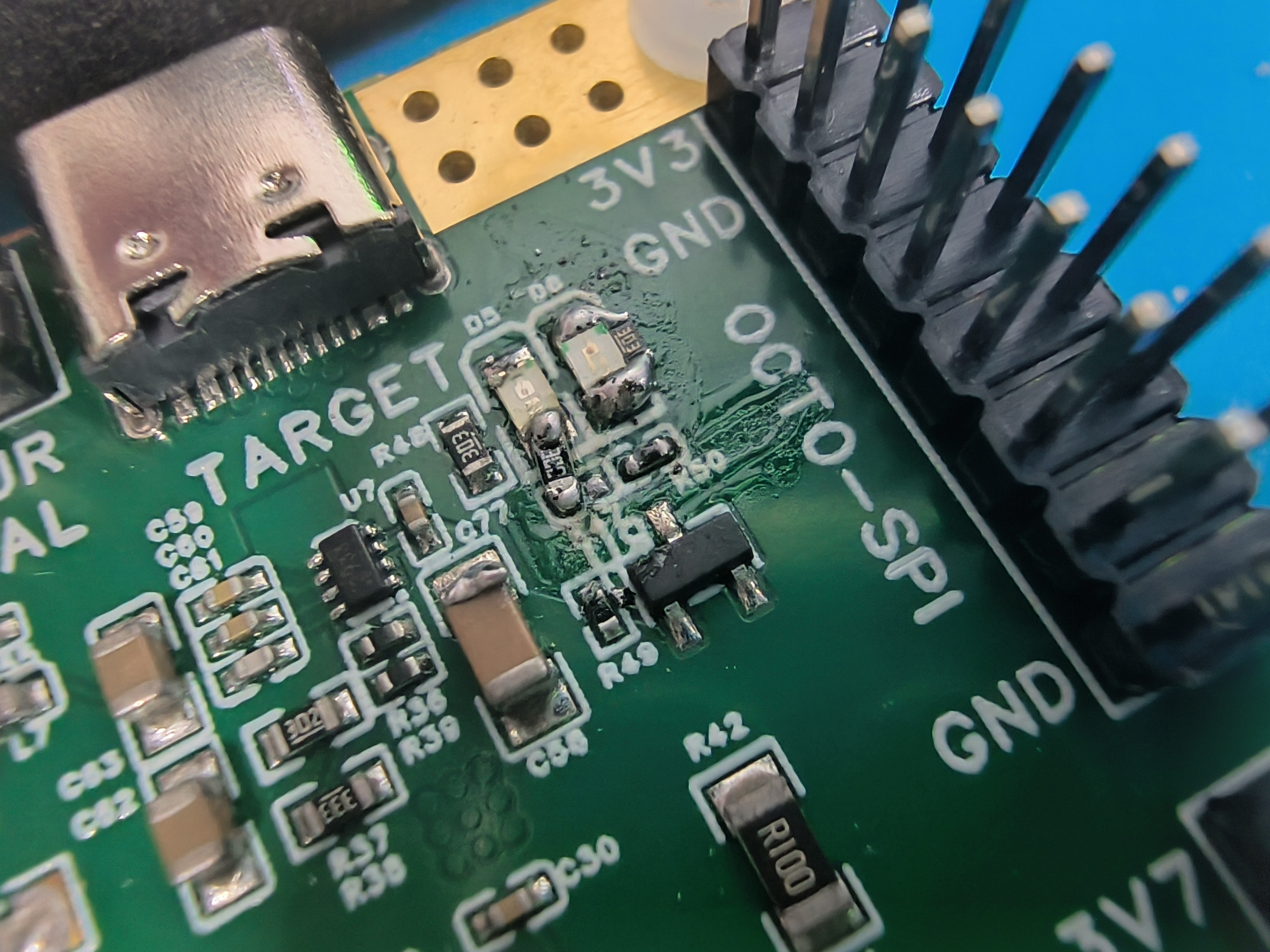

电源管理相关电路,其中最大的电容是1206封装的,还有0805的电容和LED,0603的电阻,0402的电阻和电容等,这种密度已经不适合纯手工焊接了

注意红色标记处的盘中孔,在树脂塞孔工艺下几乎不可见,焊盘非常平整

在开始调试之前,先用小台锯把右边小板切下来。忘了说了,这块小板是用来连接左边的核心板和FPGA板的。

测试各电源对地有没有短路。如果有,就别费后面的工夫了,好好查设计图吧。好在没有。

电源管理

核心板支持USB一线通,包括调试、串口和供电,另有一路Type-C直接连接到H563,包括USB FS和PD,电压不超过20 V。这两路供电可以共存,因为前者输入端接了一个肖特基二极管。呃,事实上是4个并联,为了降低压降。

由于PD一路最高能达到20 V,只用LDO肯定是不合适了,因此电源管理的思路是在USB经过肖特基二极管和PD直接并联,先DC/DC,再LDO到3.3 V。这样一来,从USB的5 V到3.3 V中间要经过肖特基二极管、DC/DC和LDO三级压降。因此肖特基二极管才需要并联多个,DC/DC要选择同步型的(这里假设使用buck,不引入buck-boost),LDO也要压降比较小。

最终选择的型号如下:

- DC/DC:TPS62933,3.8~30 V输入,3 A输出,开关频率200 kHz到2.2 MHz可调

- LDO: TPS7A7001,1.425~6.5 V输入,2 A输出,输出电压可调

这个DC/DC不是很好找,常用型号都不行,因为需求是低至4 V、高至20 V输入,同步整流,开关频率不要太低(太低了我不喜欢)。这一级的输出设置为3.7 V。

为啥都选TI的?因为我是TI孝子(TI的MCU除外,MCU方面我是ST孝子)。

下面开始动手。先焊接反面电感,焊接各排针。USB先不连,通过排针给输入5 V,成功得到3.7 V输出。

板上有一个电路监测输入电压,当电压超过6 V时,典型情况为PD握手成功,则会有一红灯亮起。这一功能可以用一颗TL431实现,在这块板上我用的是CJ431,因为它不要换料费。

VIN电压检测电路,当VIN>6 V时LED亮起,VPWR为DC/DC产生的3.7 V

工作原理:431的控制端(左)电压小于2.5 V(典型值)时,图示的“稳压二极管”关断,LED不亮;大于2.5 V时,导通,LED亮。

实测发现当电压低于6 V灯也会微亮,而高于6 V后亮度也不会变化得太明显。经测试,发现CJ431的导通电压达到1.8 V(即图中K极电压为1.8 V),留给LED和限流电阻的电压只有2 V,而设计时我在仿真里看到的导通电压只有1.2 V,由此给R50取值。这样一来,只有减小R50,才能让LED达到比较合理的亮度。手边0402电阻并不多,随便选了个100欧上去,看起来还不错。

现在低于6 V和高于6 V已有明显区别,但我还是想消除低于6 V时的微亮。产生这种现象的原因是CJ431在关断时也有电流泄露,而这种几十微安的电流流过LED产生的亮度是很容易观察到的(人眼是比较log的)。此时100欧电阻上有电压5 mV,而LED的电压为1.7 V。如果我能给LED并联一个电阻,使得两者总电流为50 uA时,电压小于1.7 V,那么LED就不会亮起。当然,这个电阻也不能太小,否则CJ431导通后LED也不会亮。经试验,电阻取30k即可。

电源电压指示电路(最终版)

旁边还有一个常亮的电源指示灯,为了让两个灯亮度相近,其限流电阻R47改成了20k(试出来的)。

电源电压指示电路实物图(最终版)

焊接两片LDO,两个3.3 V输出均正常。

功耗评估电路

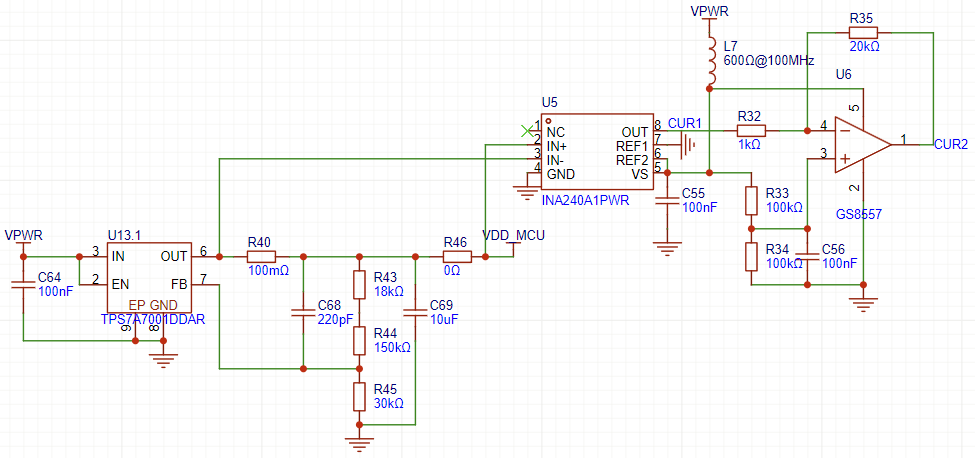

板上有一电路测量其中一路3.3 V的负载电流,其原理为测量采样电阻上的电压并放大。采样电阻有0.1欧、1欧和10欧通过焊接选择(让嘉立创全焊上,这样就不用自己备料了,反正几乎不要钱),位置有负载电容前和后两种:如果放在R40的位置,那么采样电阻上的压降在反馈前,不会影响输出电压,但LDO稳定性可能受到影响;如果放在R46的位置,那么LDO稳定性不受影响,但负载调整率比较高。

INA240是一款带PWM抑制功能的电流感应放大器,其A1后缀版本的放大倍数为20。

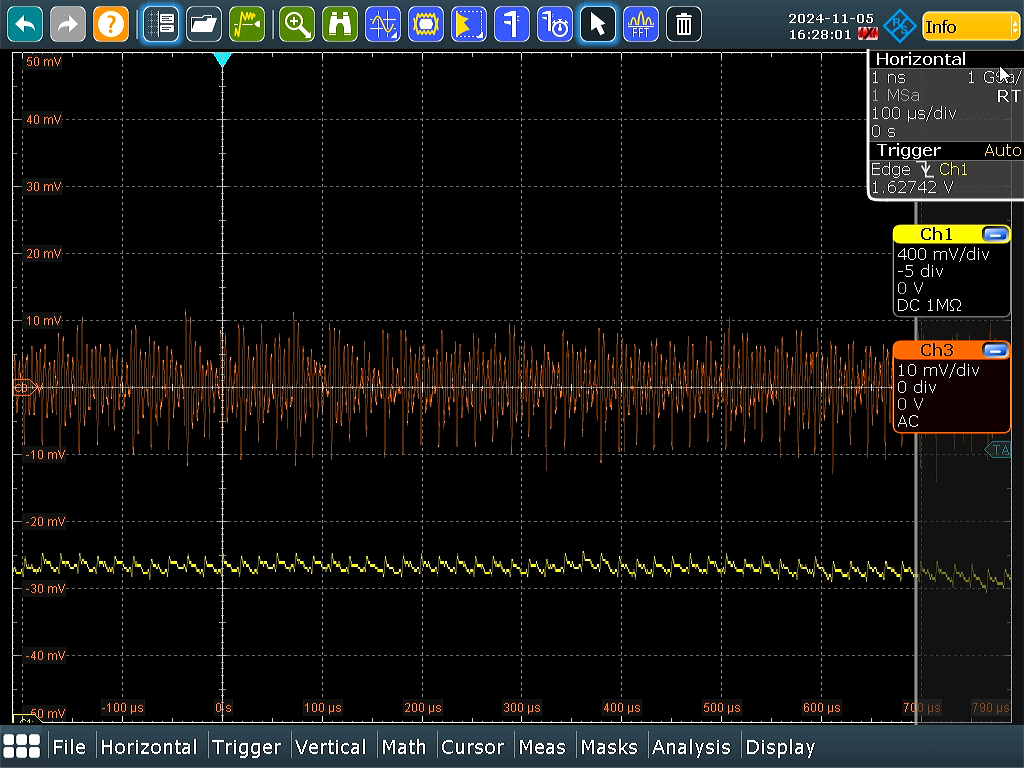

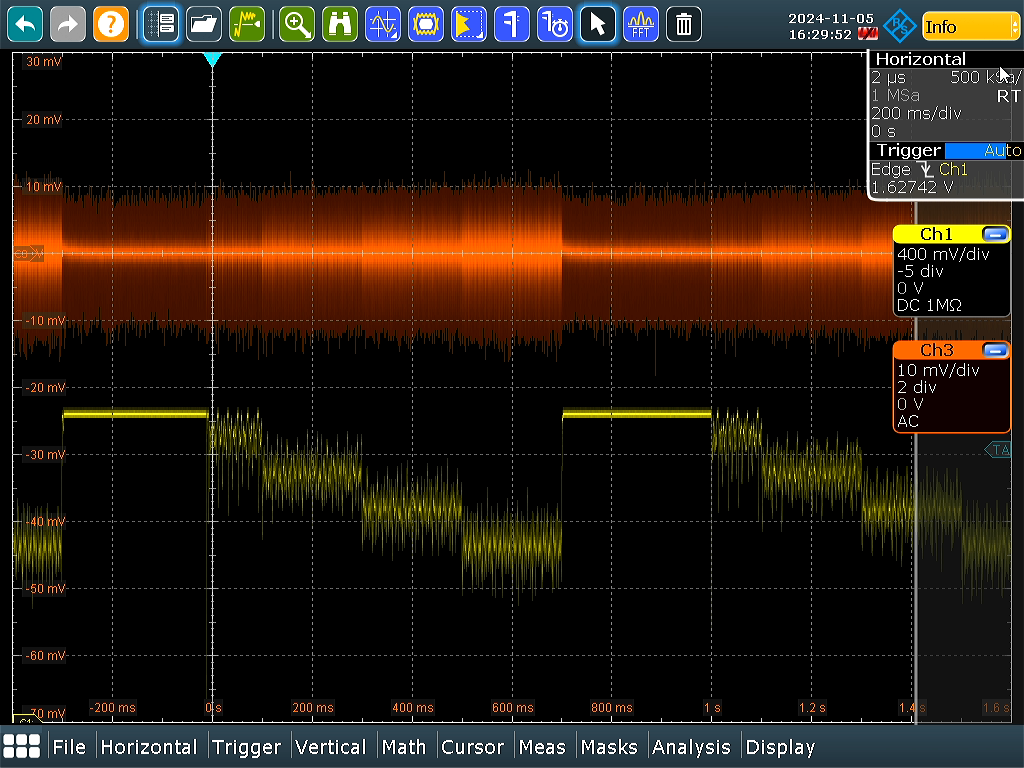

从折中的方案开始,R40=1 Ω,R46=0,则增益为20 Ω(意思是电流变化1 mA体现为输出电压变化20 mV)。从现在开始固定输入电压为10 V。负载电流0 mA时(实际上反馈电阻上有一点电流),输出电压小幅振荡;输出电流50 mA时,振荡幅度大约翻倍,在20 mVpp左右。

输出电流0 mA,CH1为电流检测电路输出(CUR1),CH2为输出电压(AC耦合)

输出电流50 mA

输出电流0~40 mA,10 mA步进,可以观察振荡幅度随电流的变化

电流检测中有大量50 Hz及其谐波分量,可能是电子负载的问题,电子负载型号为普源DL3021。

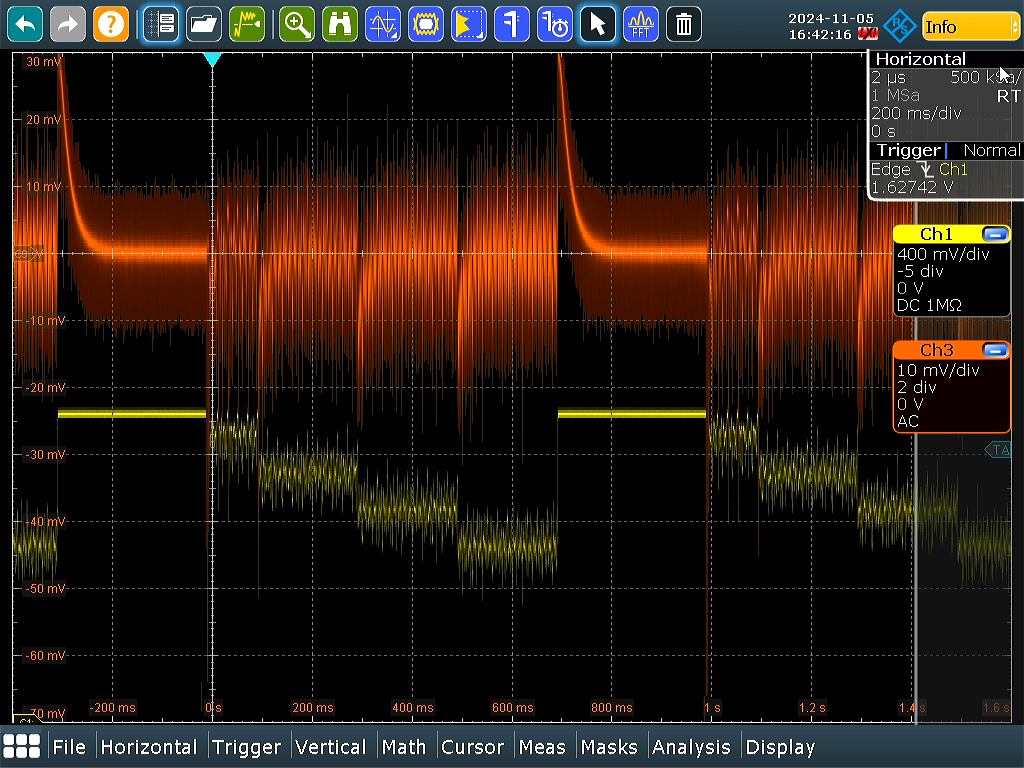

奇怪的是,如果把电阻放在R46,输出瞬态响应反而更差了,并且振荡幅度也不减小,说明振荡不是LDO稳定性问题。但我也不知道是什么原因。

输出电流0~40 mA,10 mA步进(R40=0,R46=1 Ω)

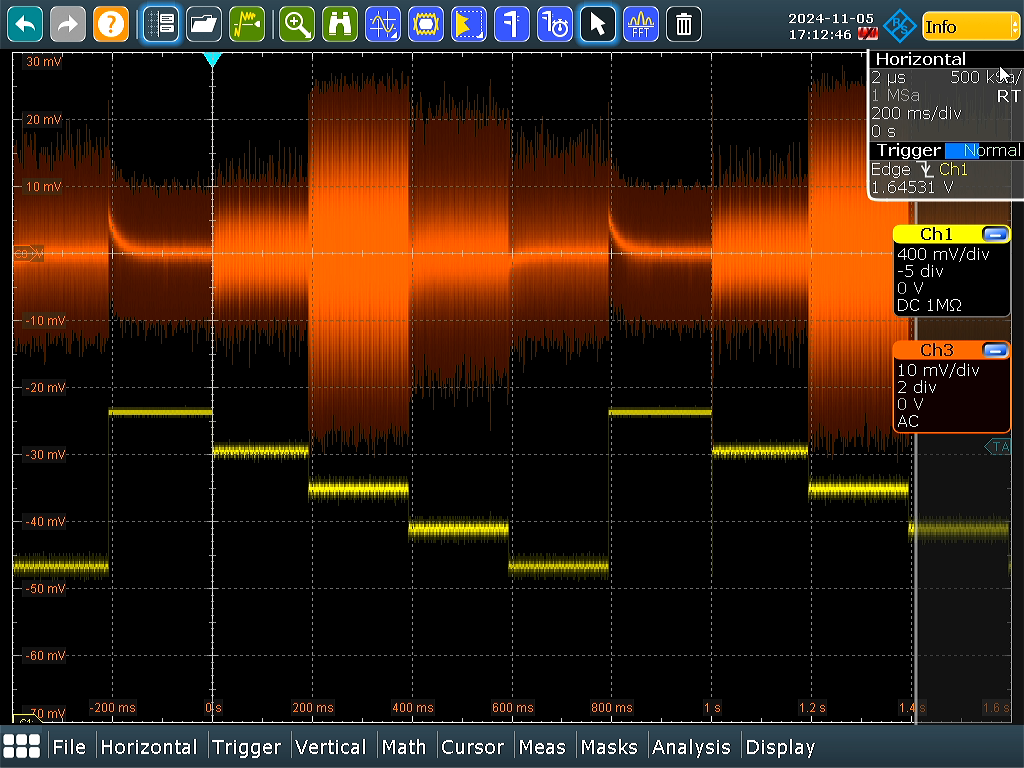

所以电阻还是放在R40吧。换成10欧,电流需要减小,但市电耦合的电流幅度不变,相当于电压噪声放大10倍,根本没法看。换成0.1欧试试。

输出电流0~400 mA,100 mA步进,可以观察振荡幅度随电流的变化

后面还有一级基于通用运放的20倍放大。面向库存选型,选择了GS8557了,这是一款增益带宽积达到13 MHz的精密运放。考虑到输出电流是单极性的,为了获得更大的输出范围,原理图中R33改成了105 k。

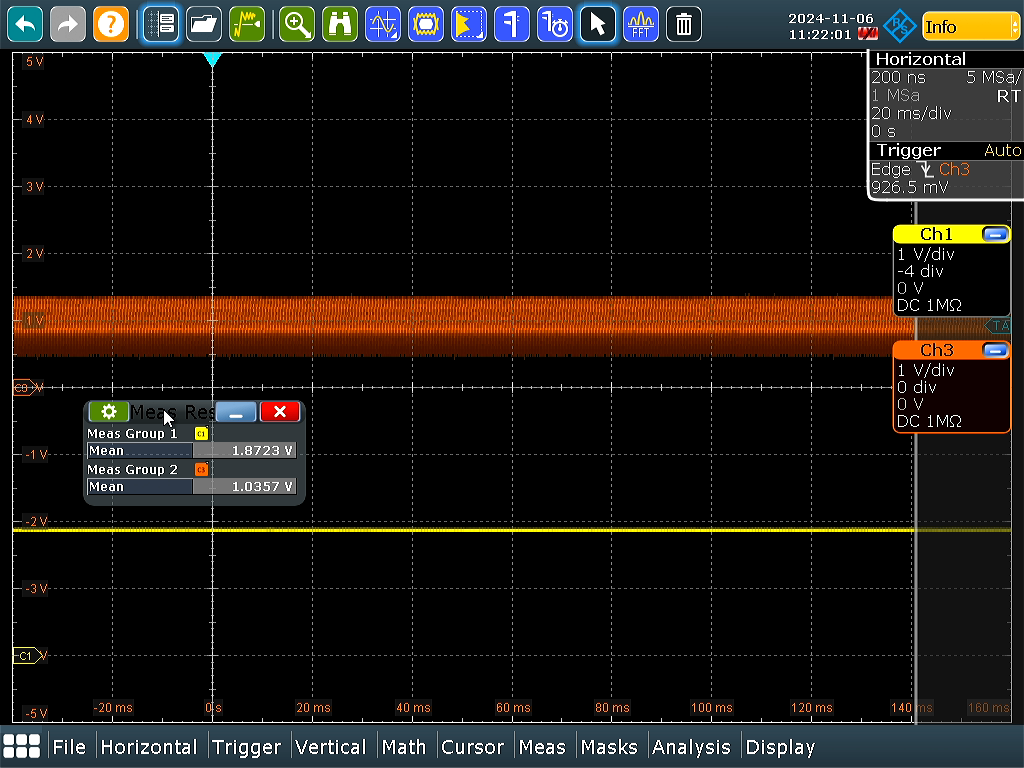

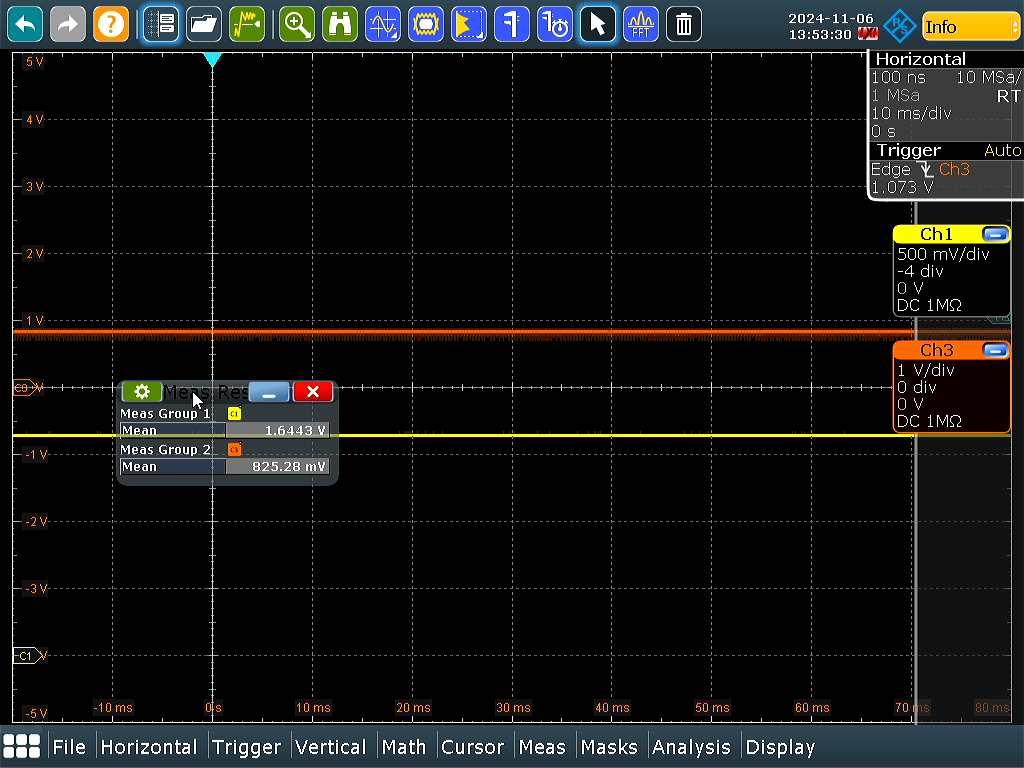

无负载时,电流感应放大器输出(CH1)与运放输出(CH3)

现在信号中的噪声还是很大,这是因为电流感应放大器一级REF2把电源波纹带了进来,甚至还放大了。我属实是低估了开关电源的波纹,尤其是轻载下的波纹,因为轻载下它会工作在PFM模式。不过也并不是无解:只需要把REF2接到一个稳定的直流电源上,它可以是另一路3.3 V LDO的输出;与此同时,R33的上端也应改接到该电源上。

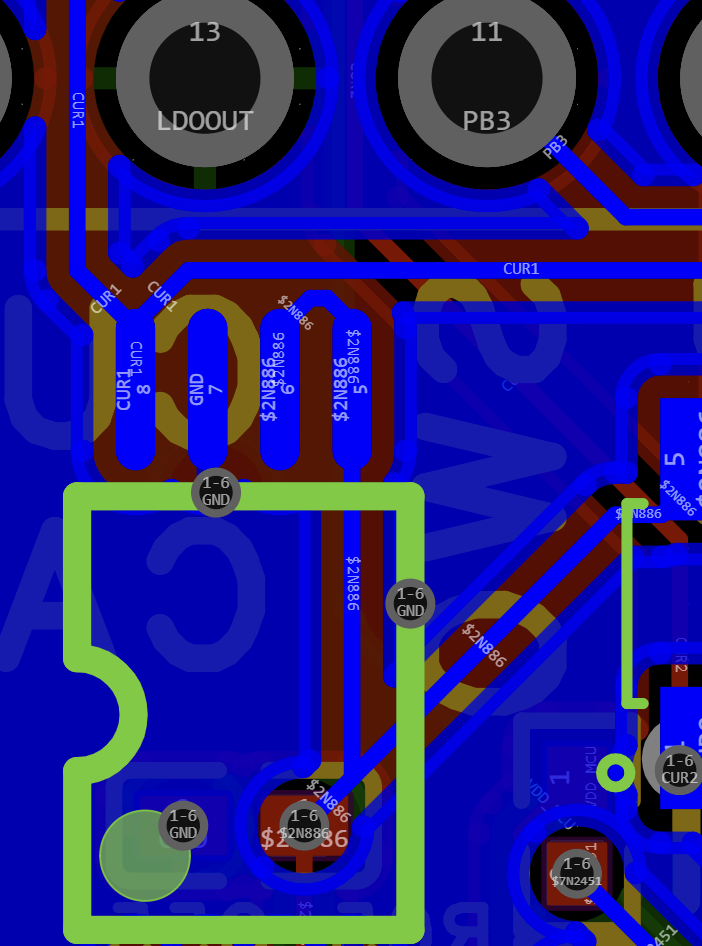

这在原理图上非常简单,在PCB上操作却不太容易。我大概是在画板的时候就想到了这个问题,特意把6号引脚(REF2)连接电源的那根线往外拐了一下,于是割线才变得稍有可行性。

PCB底面(已翻转):INA240A1局部

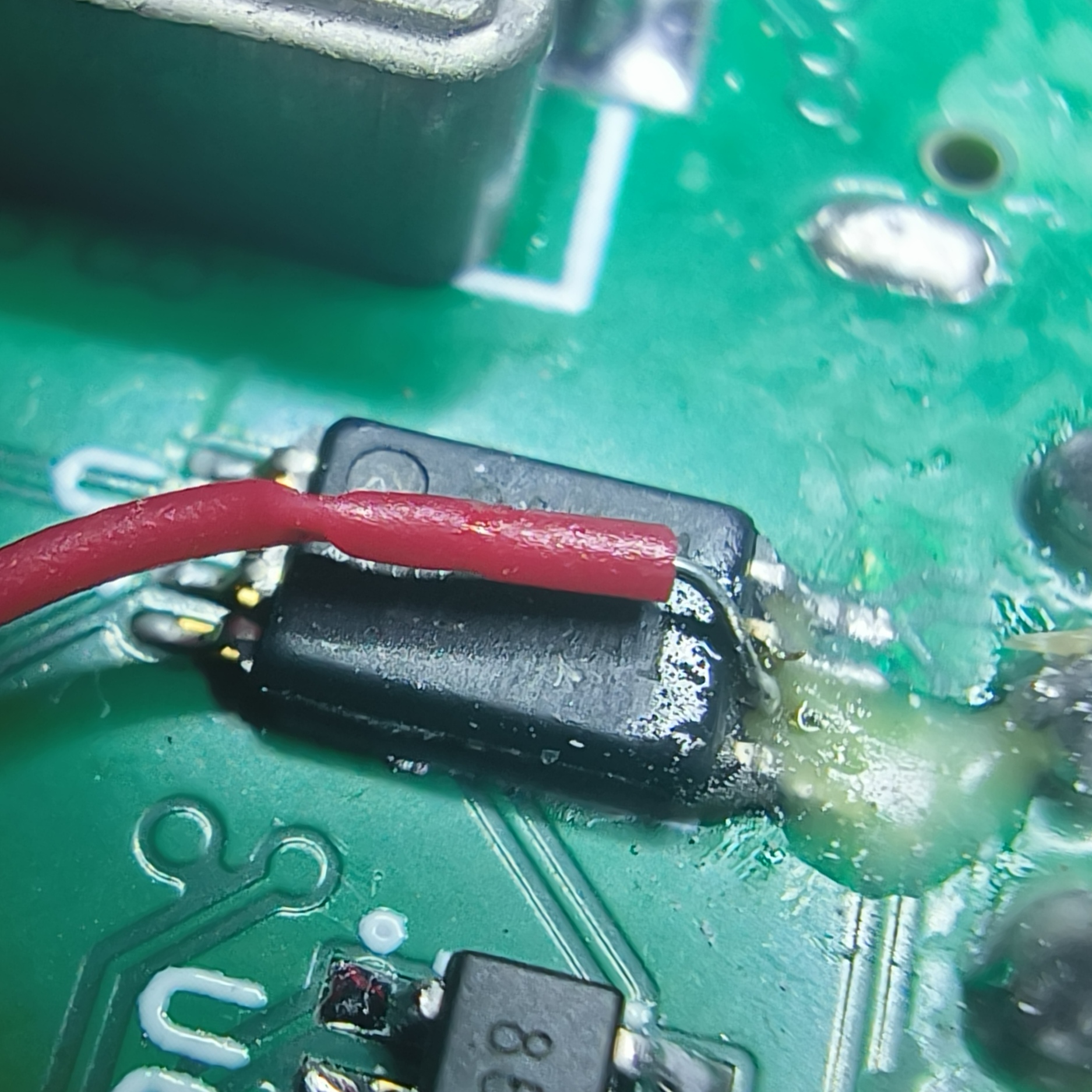

但是仍然有难度,借助实验室很牛逼的显微镜才割成功(不得不说真的牛逼),而且还不小心割到了上面的CUR1信号,最后加点锡焊回去,然后打上阻焊。

底层INA240处飞线

顶层飞线

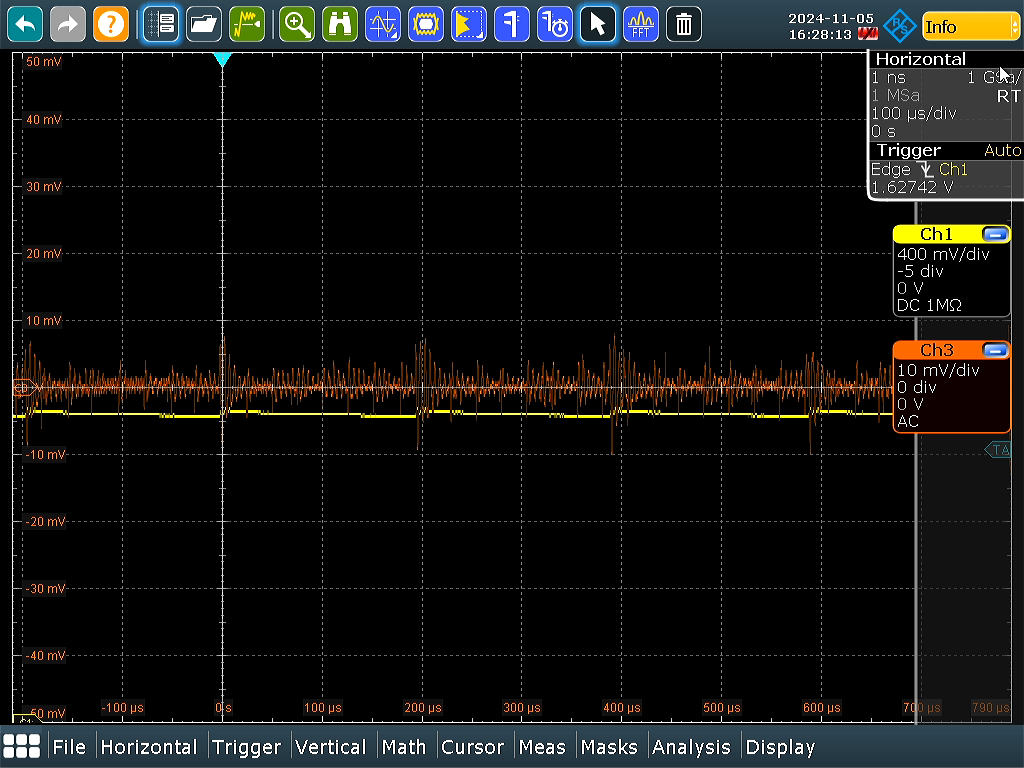

整改过后噪声就很小了,但还看得到,应该是两个放大器电源耦合进去的。

修改偏置电源后,无负载时,电流感应放大器输出(CH1)与运放输出(CH3)

市电耦合问题没有缓解,焊上单片机以后再看是不是电子负载的问题。

未完待续

下一篇目标:调试器、H563基本例程、SDRAM

posted on 2024-11-06 19:54 Jerry_SJTU 阅读(186) 评论(0) 编辑 收藏 举报

【推荐】国内首个AI IDE,深度理解中文开发场景,立即下载体验Trae

【推荐】编程新体验,更懂你的AI,立即体验豆包MarsCode编程助手

【推荐】抖音旗下AI助手豆包,你的智能百科全书,全免费不限次数

【推荐】轻量又高性能的 SSH 工具 IShell:AI 加持,快人一步

· 阿里最新开源QwQ-32B,效果媲美deepseek-r1满血版,部署成本又又又降低了!

· 开源Multi-agent AI智能体框架aevatar.ai,欢迎大家贡献代码

· Manus重磅发布:全球首款通用AI代理技术深度解析与实战指南

· 被坑几百块钱后,我竟然真的恢复了删除的微信聊天记录!

· AI技术革命,工作效率10个最佳AI工具