一些小知识小结下

(1)同步复位 VS 异步复位

首先这两种复位方式的区别,在代码上看很小,就是看在always里有没有rst_n,如果有时钟又有rst_n,则为异步复位,否则为同步复位。

那啥时候用同步复位?啥时候用异步复位?这个需要看情况,最简单的方法就是,如果输入的clk时钟信号是外部接口过来的,则用异步复位,因为同步复位,逻辑的复位需要时钟来配合,而外部接口的时钟信号clk万一罢工,此时电路板只能通过加断电重启,这是很不爽的^_^ !因此如果时钟信号不可靠,就用异步复位,比如以太网里的数据恢复时钟,对于这种情况用异步复位好。若时钟信号是FPGA内部模块产生的时钟,则可以使用同步复位。

另外使用异步复位,需要做异步复位同步释放处理,这个搞过FPGA的人都知道,还有人说用异步复位比同步复位节省资源,因为每个D触发器身上有个异步复位端,我觉得现在的FPGA资源规模,这个所谓优势就忽略吧,好,就这么多!(想起以前有个工牌上写的资深FPGA工程师的人,问他为啥喜欢用同步复位,他解释了一堆什么时序分析,讲的什么玩意儿,怪不得滋肾,只喜欢能深入浅出的大师)

(2)FPGA的工作验证占比很大

做测试验证时,不要考虑是否能实现,如何实现测试,应当直接去列举想要测试的功能点,将想这些功能点进行列表细化,这样做的好处一个是避免想到一个测一个这样的做法,这样容易漏测,另外可以通过列表看出整个验证工作的大致工作量,这样就可以看看小弟的工作量充不充实了,便于压榨,嘿嘿。。。

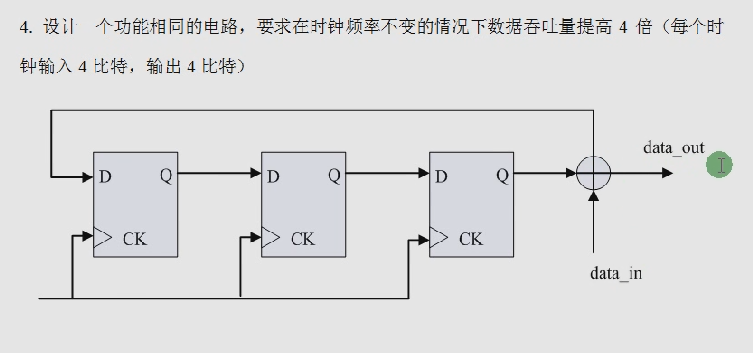

(3)来道笔试题尝尝

要求在时钟频率不变的情况下,提升电路的数据吞吐率。注意data_in和data_out的位宽为4bit。

可不是简单的复制4份电路哦!^_^,嗯!面试时可以拿出来考考小弟的数电基础!